计算机组成原理3.6高速缓冲存储器Cache

Posted 桃浪十七

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机组成原理3.6高速缓冲存储器Cache相关的知识,希望对你有一定的参考价值。

3.6.1 Cache工作的基本原理

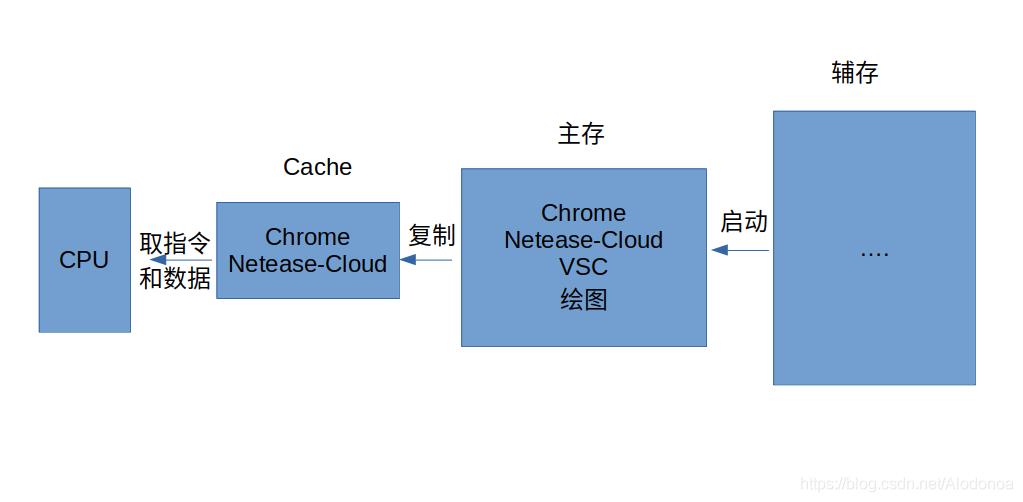

利用程序访问的局部性原理,包括空间局部性和时间局部性。举个粒子,比如现在使用Chrome浏览器,后台还在运行网愈云音乐,之前使用了VSC和绘图,则Cache把主存中存放的Chrome和网愈云的相关数据暂存到Cache块中,VSC和绘图工具依然保留在主存中。当我需要使用VSC时,Cache又会把VSC的相关数据暂存到Cache块中提供CPU访问。

3.6.2 Cache和主存的映射方式

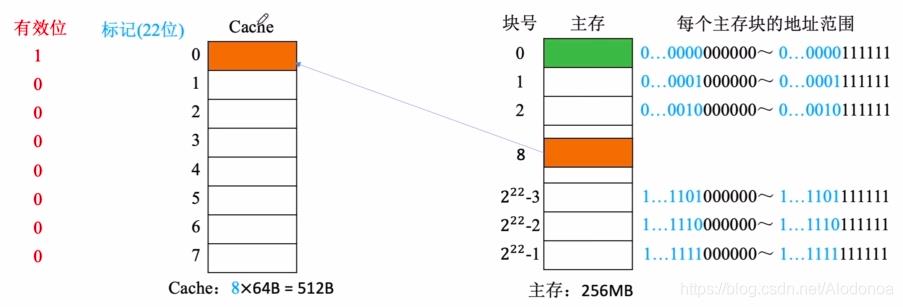

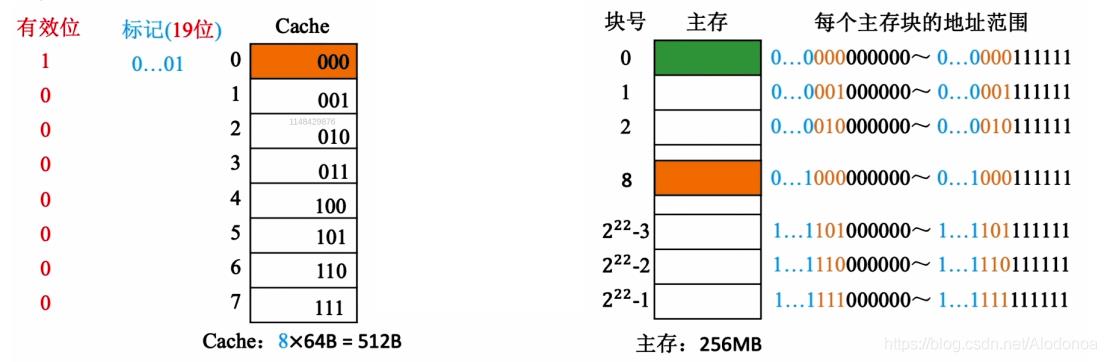

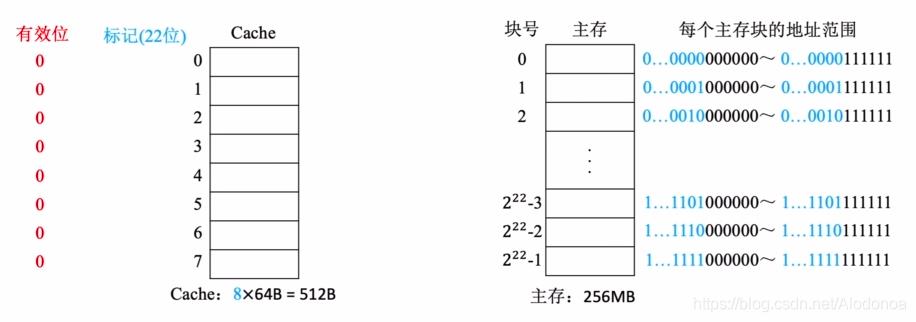

用一个题目举粒子,假设某个计算机主存地址空间为256MB,按字节编址,,其数据Cache有8个Cache行(块),行(块)长为64B。

1)直接映射

直接映射。每一块主存块只能放入Cache块中的唯一位置。

Cache由“有效位”“标记位”和“Cache块”组成,主存由“块号”“主存块”组成。

这里需要先明白几个注意的点:

1、有效位初始全部置为0,有效时候为1,无效为0;

2、每一块Cache块的大小与主存块的块长应保持一致;

3、Cache块的标记应该与主存块的块号一致;

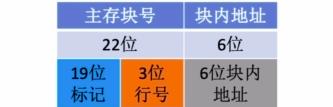

4、直接映射需要对主存块号对Cache块数进行取余操作,主存块在Cache中的位置=主存块号%Cache总块数,题目中则是,主存块号%23,相当于保留了主存块号的末尾3位,Cache中的标记位为主存块号的其余几位。此时Cache块号是主存块号的末尾3位。如下图

题目中主存地址空间256MB=228B,Cache块长64B=26,推断主存块块长也是64B,因此主存块应该有228/26=222个,取余运算后Cache块的块号应是后3位,Cache块的标记为主存块号前22-3=19位,块内地址即为块长,主存块和Cache块有下图关系

则直接映射CPU访存过程为:

将主存块号与Cache块的标记比较,若主存块的前19位与Cache块标记一致且Cache的有效为位为1,表示命中,根据标记位访问对应块内地址的数据。若不一致或者有效位为0表示未命中,则正常访问主存。

2)全相联映射

全相联映射。每一块主存块都可以转入Cache的任意位置。

这里借用学习时候的讲义来说明,

Cache由“有效位”“标记位”和“Cache块”组成,主存由“块号”“主存块”组成。

这里需要先明白几个注意的点:

1、有效位初始全部置为0,有效时候为1,无效为0;

2、每一块Cache块的大小与主存块的块长应保持一致;

3、Cache块的标记应该与主存块的块号一致;

这个题目中主存地址空间256MB=228B,Cache块长64B=26,推断主存块块长也是64B,因此主存块应该有228/26=222个,块内地址即为块长,主存块有下图关系

则全相联映射CPU访存过程为:

将主存块号与Cache块的标记比较,若一致且Cache的有效为位为1,表示命中,根据标记位访问对应块内地址的数据。若不一致或者有效位为0表示未命中,则正常访问主存。

3)组相联映射

组相联映射。主存块的数据可以放入特定Cache块组内的任意一个Cache块中,即为,组间采取直接映射,组内采取全相联映射。唯一不同点是,若题目采取2路组相联映射,那么取余运算是主存块号%分组数量,换言之,直接相联映射可以看作是1路组相联映射。本题组相联映射的主存块和Cache块关系是

则组相联映射CPU访存过程为:

根据主存块号后两位确定在Cache中所属分组,若主存块号前20位与Cache块标记一致,且有效位为1,表示命中,若未名中则正常访问主存。

3.6.3 Cache中主存块的替换算法

1、随机(RAND)算法,任意访问,当需要替换时随意替换确定的Cache块。

2、先进先出(FIFO,First In First Out)算法,选择最早调入Cache的Cache块进行替换。没有依据局部性原理,最早调入的可能是最常用的数据。

3、近期最少使用(LRU,Least Recently Used)算法,选择一段时间内访问次数最少的Cache块进行替换,作为堆栈类算法它依据了局部性原理。

手算LRU,观察哪个Cache块是一段时间内使用最少的,将其替换。

机器实现LRU,为每一个Cache块设置一个计数器,记录该Cache块有多久没有被访问,初始计数器为0。命中Cache块时,对应计数器归0,比其低的计数器+1,剩余不做改变;未名中且还有空闲Cache块时,数据放入空闲Cache块且对应计数器归0,其余非空闲Cache块+1;未名中且Cache无空闲块时,将访问的数据替换到计数最大的Cache块,并且计数器归0,其余Cache块计数器+1。

3.6.4 Cache写策略

Cache设置“脏位”,初始为0,CPU对Cache写命中,脏位变为1.

1、全写法,CPU对Cache写命中时,同时把数据写入Cache和主存,,此处会增加一个用SRAM做的FIFO写缓冲来暂存写入Cache的数据,当CPU执行其他时会把写缓冲的数据写入对应的主存块。

2、写回法,CPU对Cache写命中时,只把数据写如Cache,等该Cache块要被替换时候再把数据同步到主存中。

3、写分配法,若CPU未对Cache命中,会访问主存并把数据调入Cache进行修改,适合配合写回法使用。

3、非写分配法,若CPU未对Cache命中,会直接把数据写入主存,不会把主存数据调入Cache进行修改,适合配合全写法。

现代计算机通常设置了多级Cache,多级Cache之间采用全写法和非写分配法保证数据一致,Cache和主存之间采用写回法和写分配法。

以上是关于计算机组成原理3.6高速缓冲存储器Cache的主要内容,如果未能解决你的问题,请参考以下文章

计算机组成原理 王道考研2021 第三章:存储系统 -- 高速缓冲存储器Cache基本概念和原理(程序访问的局部性原理)Cache和主存的映射方式替换算法写策略