(计算机组成原理)第三章存储系统-第六节1:高速缓冲存储器Cache及其相关基本概念程序访问的局部性原理和命中率

Posted 快乐江湖

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了(计算机组成原理)第三章存储系统-第六节1:高速缓冲存储器Cache及其相关基本概念程序访问的局部性原理和命中率相关的知识,希望对你有一定的参考价值。

由于程序的转移概率不会很低,且数据分布的离散性较大,所以单纯依靠并行主存系统提高主存系统的频宽是有限的。这就必须从系统结构上进行改进,也即采用存储体系,通常有以下两类

- Cache-主存层次

- 主存-辅存层次

一:Cache的基本原理

前面的讲解中我们说到过,虽然主存的速度很快,但是与CPU相比还是小巫见大巫了,因此再快的CPU面对拉胯的主存,还是会无能为力,所以Cache的出现就是为了解决这个问题。

以我们日常使用的手机为例,当你打开微信时,与微信有关的数据和代码将会被加载进主存,微信的数据有很多,比如文字数据、支付数据、运动数据等等,这些数据实则是相当庞大的。有的人使用微信可能只偏好于视频聊天功能,因此在这样的情况下,如果还是让CPU到主存中一个一个的去读取就显得不合适了

此时我们可以这样做:把这一部分的数据复制一份给Cache,由于Cache的速度和CPU十分接近,这样的话这种由主存速度慢所带来的短板效应就会被减弱

现代计算机,Cache会被集成在CPU内部,而且会用SRAM实现,前面我们说过,SRAM虽然速度很快但是集成度差,因此成本就高,这也就是为什么Cache通常都是几M的原因

二:程序访问的局部性原理

如下有这样一段简单的C语言程序

int sumarrayrows(int a[M][N])

{

int i,j,sum=0;

for(i = 0 ;i < M ;i++)

for(j = 0;j < N;j++

sum+=a[i][j];

return sum;

}

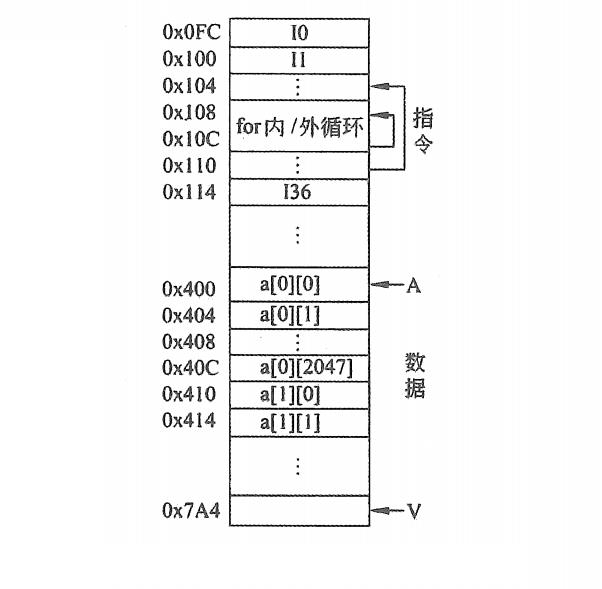

该程序在运行后会被加载进内存,程序运行的本质就是CPU在执行指令,指令又会调用数据,因此这段程序在主存分布情况可能如下

- 假定M、N为2048,按字节编址,int占用4个字节

- 这个二维数组看似是二维的,实则在主存中是一维的,相当于把第二行接到了第一行的尾巴后面。

程序访问的局部性原理包括空间局部性和时间局部性。

对于空间局部性:是指在最近的未来要用到的信息,很可能与现在使用的信息在存储空间上是邻近的。比如上面的例子中是一个数组,访问完一个元素后,其实下一个元素的物理位置和它就是相邻的,指令也是一样。

对于时间局部性:是指在最近的未来要用到的信息,很可能是现在正在使用的信息。最经典就是循环,比如上面的for循环中的sum+=a[i][j],这一条语句很明显会被重复使用多次。

结合上面我们说到的Cache,基于局部性原理,我们不难想到:可以把CPU目前访问的地址“邻近”的部分数据放到Cache中,这样的话CPU的访存操作大多数会针对Cache进行,从而提高程序的执行速度

接着我们再看下面这样一段程序,它只是在上面程序的基础上把“一行一行的访问”变为了“一列一列的访问”,这样一个简单的改变会带来很大的性能差异

int sumarrayrows(int a[M][N])

{

int i,j,sum=0;

for(i = 0 ;i < N ;i++)

for(j = 0;j < M;j++

sum+=a[i][j];

return sum;

}

- 之前访问的时候访问完

a[0][0],下一个访问的就是a[0][1],而现在下一个就变成了a[1][0]了

可以看出这样一段代码它的空间局部性很差。因为每次访问都要跳过2048个数组元素,也就是8192字节,假如主存与Cache的交换单位小于9KB,则每访问一个数组元素都需要装入一个主存块到Cache中。

三:主存块

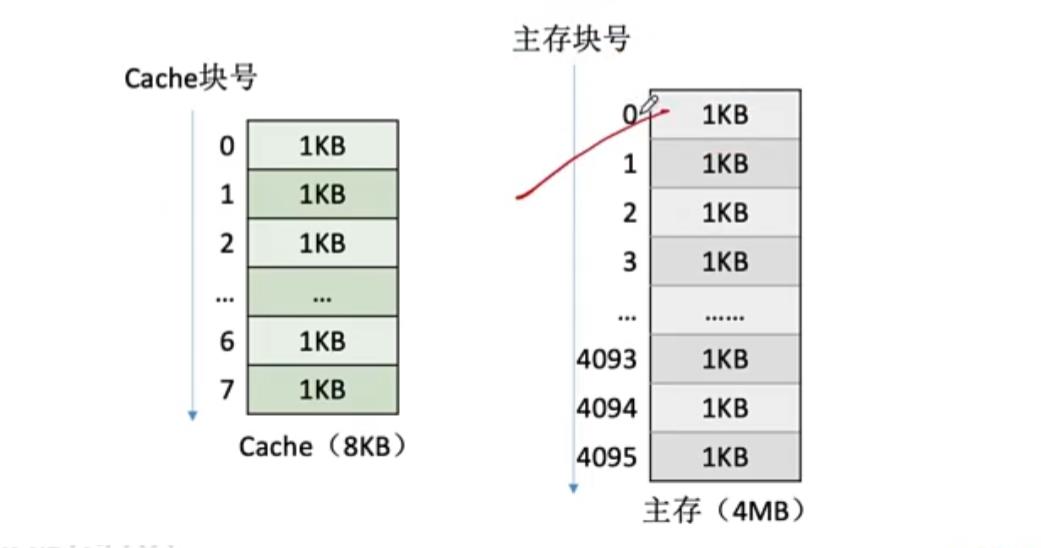

那么如何界定这个所谓的“邻近”区域呢?我们可以将主存的存储空间分块,比如每1KB为一块,主存与Cache之间会以块为单位进行数据交换

比如上面的数组中,对于a[0][0]我们先判断其属于哪一块,确定好之后将它所在的块复制到Cache中去

假设主存大小为4M,每1KB为一块,4M=4096KB,因此会被分为4096块,然后对其编号(0-4095)。

由于

2

22

=

4194304

2^{22}=4 194 304

222=4194304,所以这些地址至少需要22位才能全部表示,我们将22位地址拆分为两个部分,前12位可以表示块号(

2

12

=

4096

2^{12}=4096

212=4096),后10位表示块内地址(

2

10

=

1024

2^{10}=1024

210=1024)

假设Cache大小为8KB,块号为0-7。接着数据交换时就可以一块一块的交换了

需要注意:操作系统中将主存中的“一个块”称之为“一个页/页面/页框”,Cache中的“块”也称之为“行”

四:命中率和缺失率

假设 t c t_{c} tc为访问一次Cache所需要的时间, t m t_{m} tm为访问一次主存的所需要的时间

我们称命中率 H H H为CPU欲访问的信息已经在Cache中的比率,则缺失率为 M = 1 − H M=1-H M=1−H

CPU访问数据时可以先访问Cache,如果Cache没有命中再访问主存,那么平均访问时间

t

=

H

t

c

+

(

1

−

H

)

(

t

c

+

t

m

)

t=Ht_{c}+(1-H)(t_{c}+t_{m})

t=Htc+(1−H)(tc+tm)

也可以同时访问Cache和主存,如果Cache命中则立即停止访问主存,否则直到主存中数据访问到,则平均访问时间为

t

=

H

t

c

+

(

1

−

H

)

t

m

t=Ht_{c}+(1-H)t_{m}

t=Htc+(1−H)tm

以上是关于(计算机组成原理)第三章存储系统-第六节1:高速缓冲存储器Cache及其相关基本概念程序访问的局部性原理和命中率的主要内容,如果未能解决你的问题,请参考以下文章