cpld的QuartusII中用中文注释该怎样设置?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了cpld的QuartusII中用中文注释该怎样设置?相关的知识,希望对你有一定的参考价值。

中文注释应如何设置?帮帮!

对啊,

比如

module add_4(a,b out); //"这儿怎么用中文"

我是用QuartusII 10.0和Notepad++编辑器混合使用的。

也听说Quartus 11.0 能支持中文输入,你可以尝试一下。 参考技术A 吥懂 参考技术B 你是指程序中的注释用中文吗?》

Quartus II 上手攻略

第一次接触EDA实验,对这方面的相关操作并不熟悉。本篇文章结合上课内容和B站Quartus进行整理,总结一下Quartus 这款软件的基本使用。

参考的B站教学链接:《Quartus II 软件安装与入门教程》

Quartus 软件简介

Quartus II 是Altera公司为其FPGA/CPLD芯片设计的集成化专用开发软件,有原理图、VHDL、Verilog HDL等多种设计输入形式,内嵌综合器以及仿真器,可以完成从设计输入、综合适配、仿真到下载的完整FPGA设计流程。

用自己的语言总结:Quartus不仅支持在上面绘制电路,进行仿真,还支持编写代码,并且支持将代码下载到FPGA上。因此,总软件大小比较大,大约15G左右(我的是正版免费的Lite版本)

Quartus 软件下载

关于Quartus软件下载,有个地方需要注意,若要保证其仿真功能的正常运作,在安装界面必须勾选Modelsim。

官网上面有三个版本,前两个大型的是商业版需付费使用,轻量版本Lite可以免费使用。

我在官网下的最新版本并未注意到这个问题,导致仿真时会报错Error loading design

卸载之后,我安装的是Quartus18.1的版本,直接安装即可,一路next。

安装包由B站视频的UP提供:

18.1lite版本下载地址:

链接:https://pan.baidu.com/s/1JMH75Y7l1cW8x_uveJ1pVg

提取码:i83y

仿真流程

详细的仿真流程看视频更为清晰,这里仅放置一些关键设置图。

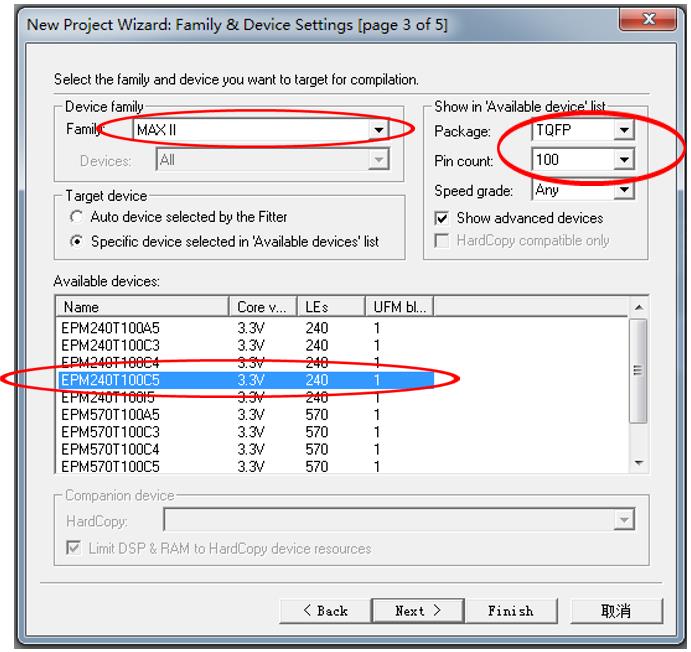

新建工程时的设置:

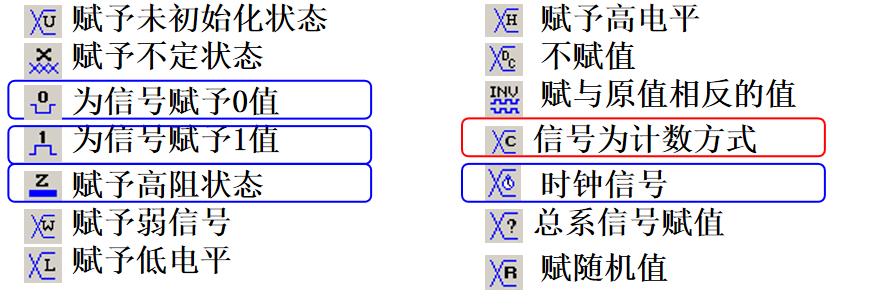

仿真界面的按钮含义:

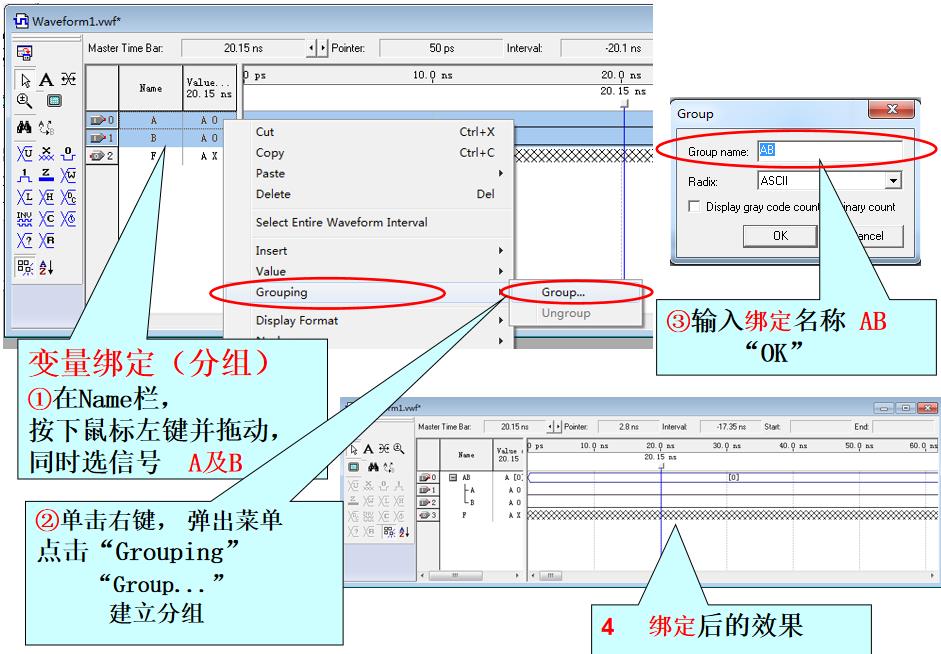

仿真界面的信号分组操作:

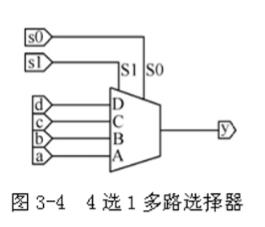

仿真实例:4选1多路选择器

原理图:

verilog代码

仿真可以有两种方式,直接画电路图或者编写verilog代码。

这里采用verilog的方式:

在File->New->选择Verilog HDL File ,写入verilog代码:

module MUX41a(a,b,c,d,s1,s0,y);

input a,b,c,d;

input s1,s0;

output y;

reg y;

always @ (a or b or c or d or s1 or s0)

begin : MUX41

case({s1,s0})

2'b00 : y<=a;

2'b01 : y<=b;

2'b10 : y<=c;

2'b11 : y<=d;

default : y<=a;

endcase

end

endmodule

注:文件保存名与模块名必须一致(这点和matlab类似)

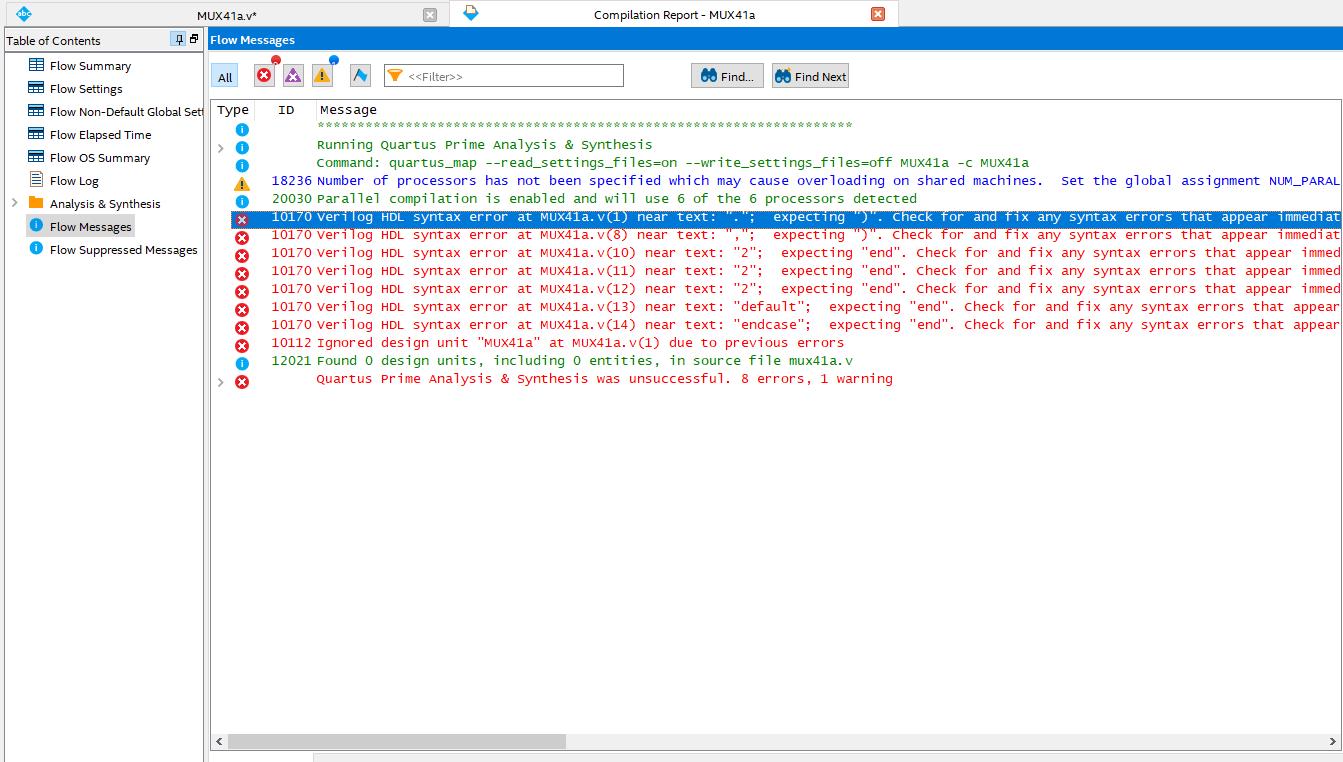

编译之后,如果有报错,可以在Flow Messages查看

仿真结果

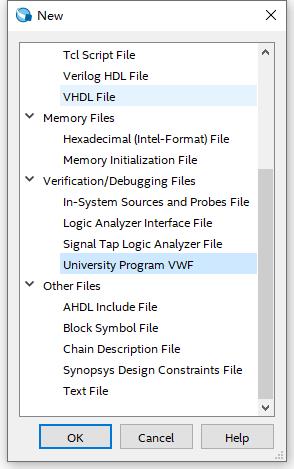

打开仿真文件:

File->New->University Program VWF

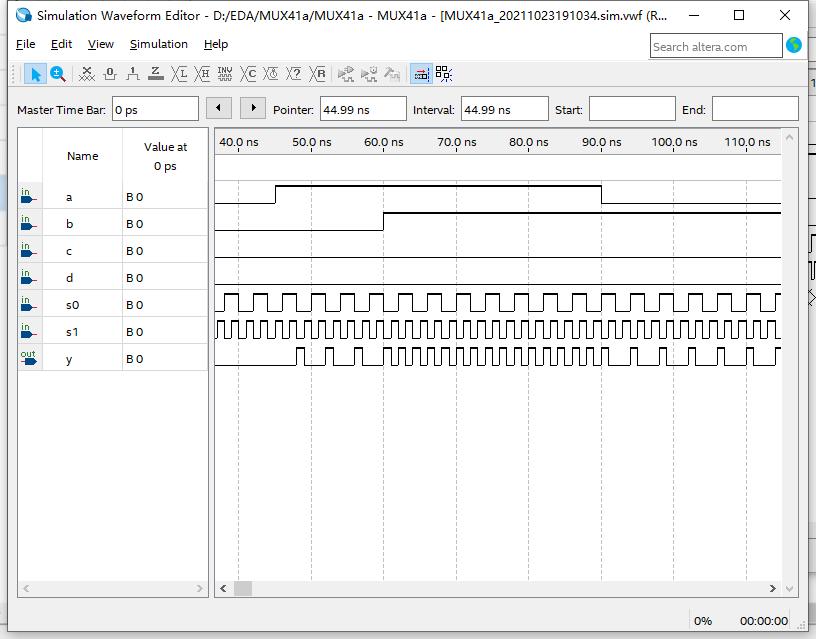

设置各参数进行仿真,编译直接保存文件即可。

仿真结果:

电路图形式

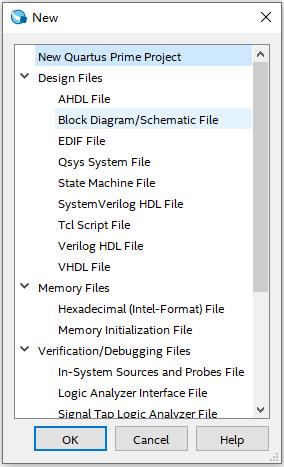

选择File->New->Block Diagram/Schematic File

手动绘制电路图,之后编译,效果类似。

与编程方式相比,该方式较为麻烦。

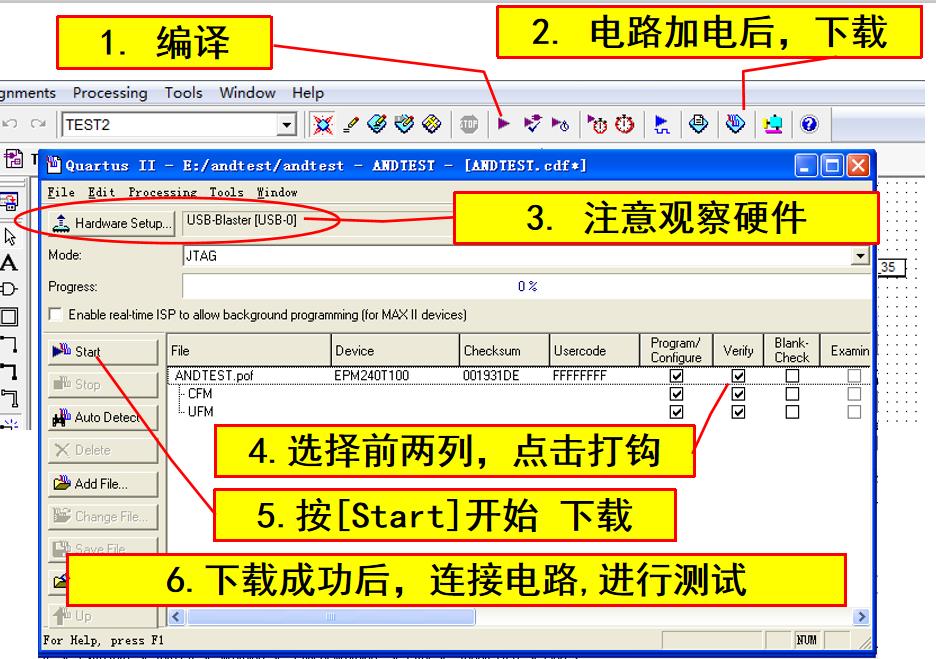

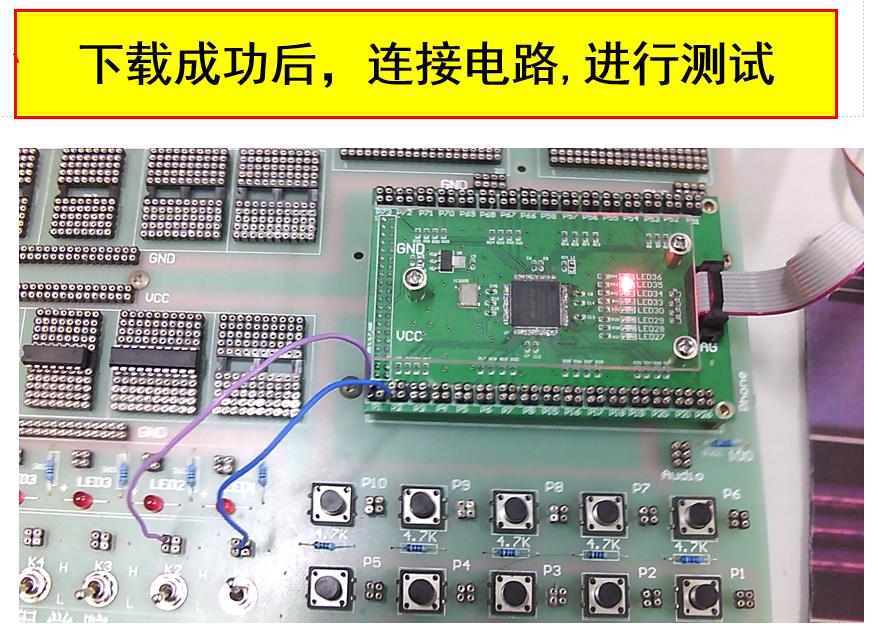

下载到FPGA

下载过程尚未实践,先将PPT内容整理一下。

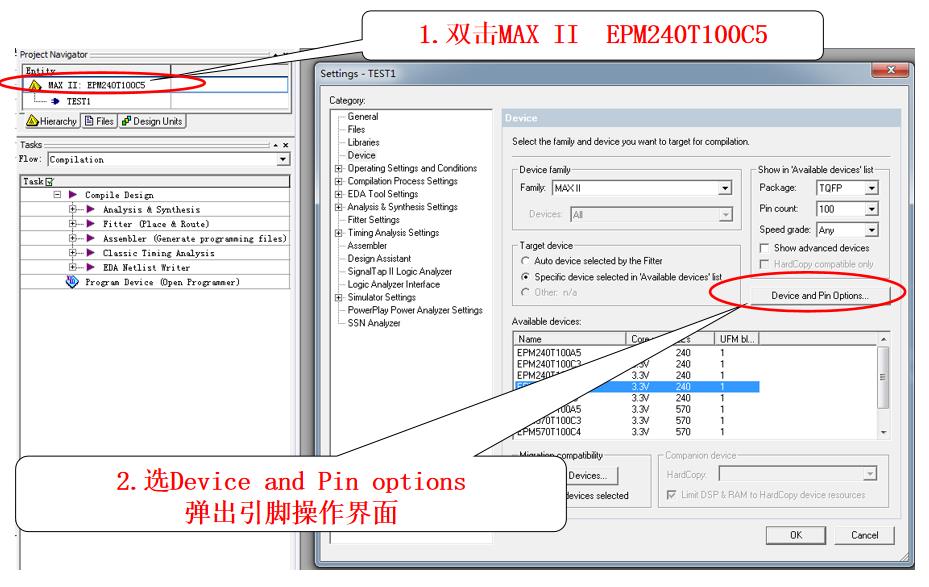

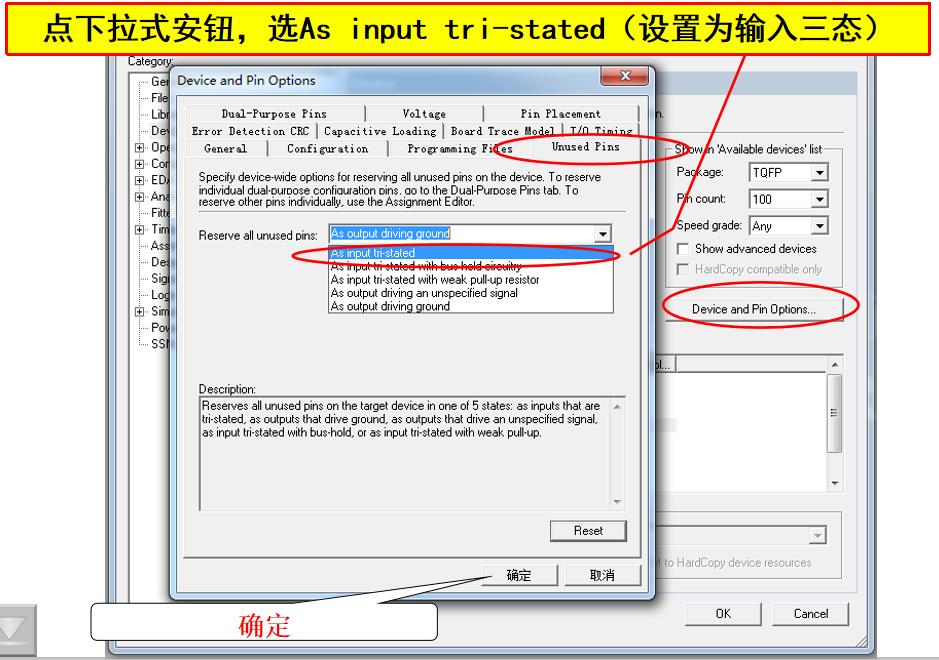

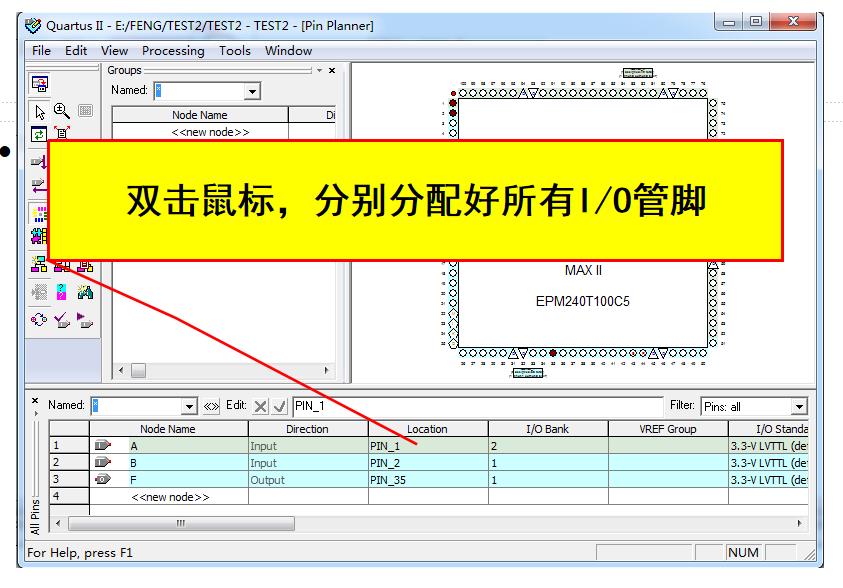

对未用引脚进行设置

感悟

verilog语言每一条可以与实际电路图进行对应,不愧是硬件描述语言。

以上是关于cpld的QuartusII中用中文注释该怎样设置?的主要内容,如果未能解决你的问题,请参考以下文章

quartusII10.1编写代码的时候怎么不能输入汉字啊,我想用中文写注释,怎么切换也不行