verilog 为啥乘法器写的那么复杂? 不是这样写也可以吗 assign c = a * b;

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog 为啥乘法器写的那么复杂? 不是这样写也可以吗 assign c = a * b;相关的知识,希望对你有一定的参考价值。

现在很多的数据存储在ram里是以补码形式存储的,现在a和b都是补码表示,乘法之后还需要是补码,如果你用*号,那乘法之前需要求补码,乘法之后需要再求补码,岂不是很麻烦,还会占用额外的面积和延时。用verilog写一个wallance-booth乘法器,直接是补码乘法器,便可以直接乘法了。综合工具里面一般都有乘法器,当然那是最优化的,面积和延时还有功耗都是最优的,但是不知道这些乘法器是不是补码乘法器,如果不是,还是需要代码里面做补码运算的。 参考技术A 直接用*其实就是调用了硬件内部的乘法器,可是有些不带乘法器的就只能用语言实现,也就会看到你所说的复杂代码了 参考技术B 以前综合工具不支持乘法器。

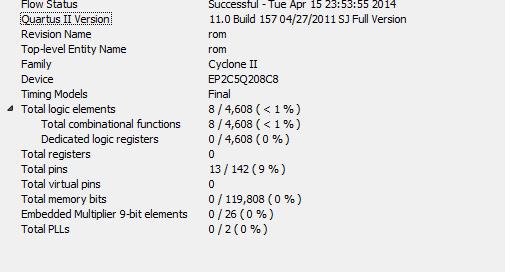

用verilog写的ROM用quartusII综合后为啥没综合到memory bit里而是综合到了LE里面要怎样才能弄到memory

module rom(addr,en,data);

input en;

input[3:0] addr;

output[7:0] data;

reg[7:0] data;

function[7:0] romout;

input[3:0] addr;

begin

case(addr)

3'h0:romout=8'b1010_1001;

3'h1:romout=8'b1111_1101;

3'h2:romout=8'b1110_1001;

3'h3:romout=8'b1101_1101;

3'h4:romout=8'b1011_1001;

3'h5:romout=8'b1100_0010;

3'h6:romout=8'b1100_0101;

3'h7:romout=8'b0000_0100;

3'h8:romout=8'b1110_1100;

3'h9:romout=8'b1000_1010;

3'h10:romout=8'b1100_1111;

3'h11:romout=8'b0011_0100;

3'h12:romout=8'b1100_0001;

3'h13:romout=8'b1001_1111;

3'h14:romout=8'b1010_0101;

3'h15:romout=8'b0101_1100;

default:romout=8'bx;

endcase

end

endfunction

always@(*)

begin

if(en)

data=romout(addr);

else

data=8'bz;

end

endmodule

谢谢你的回答,那再问一下上面的代码能不能综合到FPGA的memory里面?当要利用FPGA的memory资源时就只能像你说的那样用memory compiler?感觉要弄个ROM让它利用上FPGA的memory资源时就只能用ROM IP了。(我是新手,对FPGA的一些知识还很不了解,有些问题可能是错的,但还是希望大家能够指出来)

追答memory compiler 里面定义RAM位数、容量之后,初始化加载rom数据,不就是相当于ROM的功能了吗?FPGA通常用来做芯片设计验证,实际ASIC设计中,调用ROM IP

本回答被提问者采纳 参考技术B 我来回答一下吧,最终结果看资源的,根据资源消耗情况,软件自己决定是用le还是用mem,当然在综合策略选择上,可适当人为干扰,比如调整优化策略(面积/速度优先),但主要决定权在软件本身对资源的评估以上是关于verilog 为啥乘法器写的那么复杂? 不是这样写也可以吗 assign c = a * b;的主要内容,如果未能解决你的问题,请参考以下文章

verilog中除法运算在modelsim仿真中只要一个时钟周期就能完成,实际上也是这样吗?