verilog中除法运算在modelsim仿真中只要一个时钟周期就能完成,实际上也是这样吗?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog中除法运算在modelsim仿真中只要一个时钟周期就能完成,实际上也是这样吗?相关的知识,希望对你有一定的参考价值。

比如说always@(posedge clk)

begin

e<=(a*a+b*b)/(c*d)

end

这种写法不仅能综合,而且在用modelsim仿真中只需要一个周期就能出结果,对吗?modelsim到底能不能正确的反应一个所需的时钟数。

有知道的吗?求指点

乘法,和除法,如果不使用厂家提供的ipcore的话,要自己搭建。

我的经历,要自己搭建,一般需要多个时钟周期,需要的周期数,依赖于参与运算的数据位宽。 参考技术B 关注这个问题

modelsim常用操作之波形仿真

modelsim波形仿真的新手问题

1、实验目的

在刚接触modelsim时,被其繁复的操作流程所困,一度只能依靠在quartus中修改代码编译后再重启modelsim,自动导入才能得到波形。这样的操作最大的问题就是修改代码的成本巨大。每次更新波形的时间在5分钟左右。为此,通过不断地学习,终于将波形仿真的各个事项了解清楚。这里做一下记录,方便以后回顾。

2、实验操作

①纯modelsim的verilog仿真

一般来说,前仿真是不需要器件的。如果使用了IP核就另论。这里先通过纯modelsim仿真了解modelsim的工作目录的结构,为后面的联合仿真的刷新提供基础。

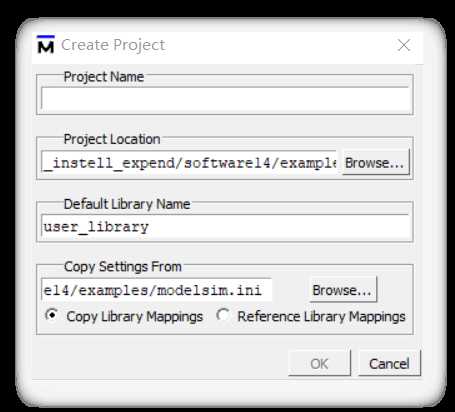

这里直接使用图片集描述:

这个操作感觉意义不大,在新建工程中也也可以创建library。

这个可以添加project和library,构建设计平台。

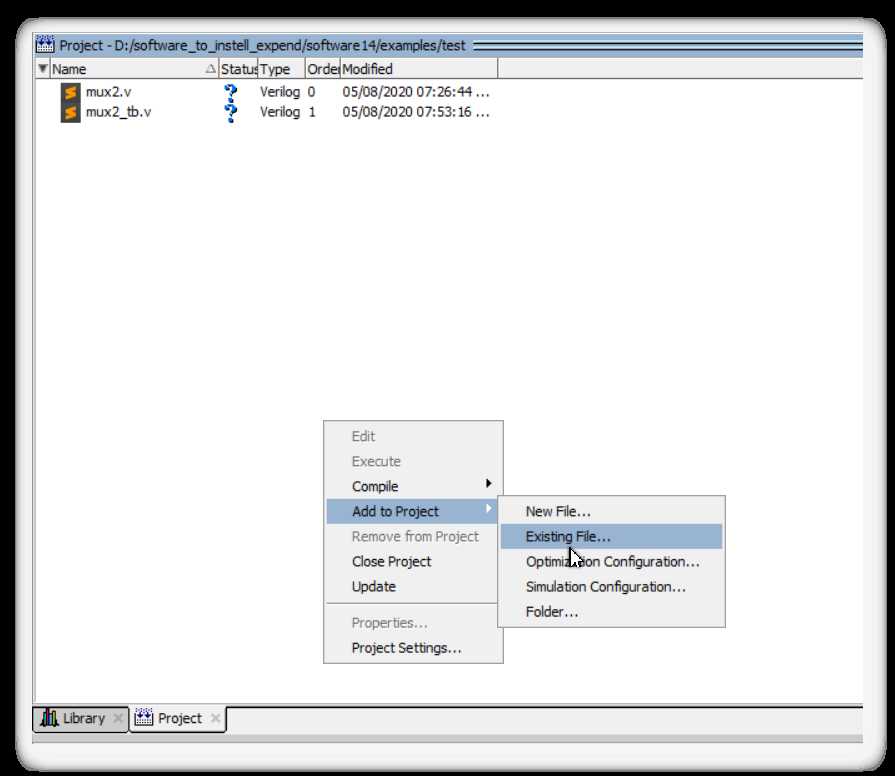

然后进入project窗口,这个窗口就是用于编辑工程的,具体操作在前面的一篇关于modelsim的操作中有,这里不具体说明。

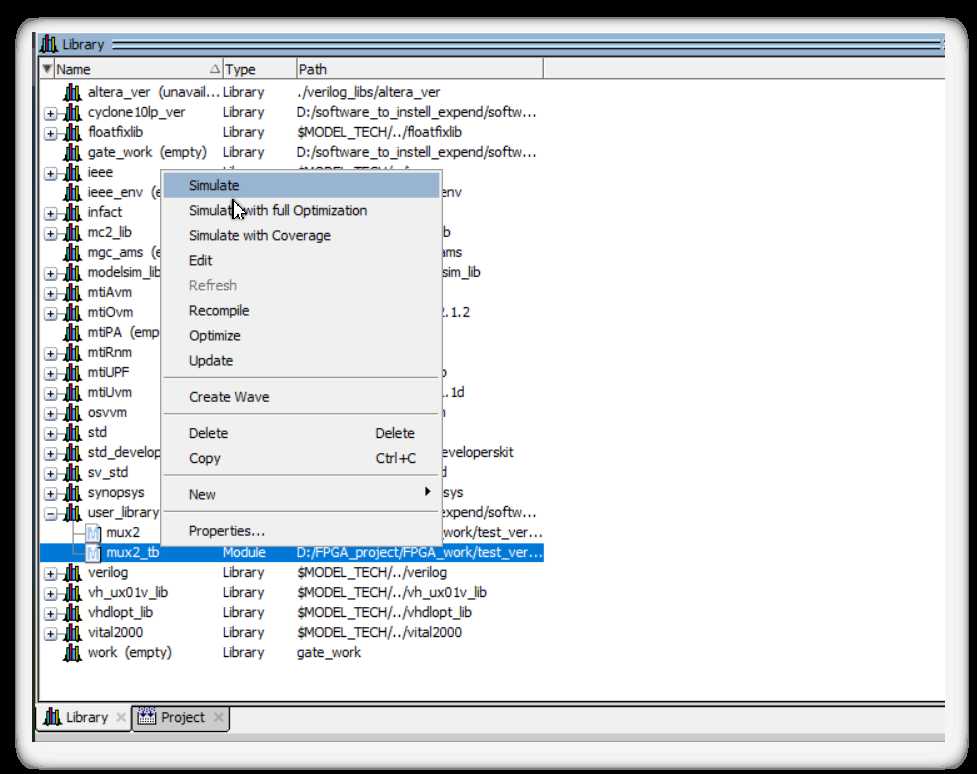

添加本地文件和编译都在右击中。接下来转到library界面,就在上图的左下角的library中。

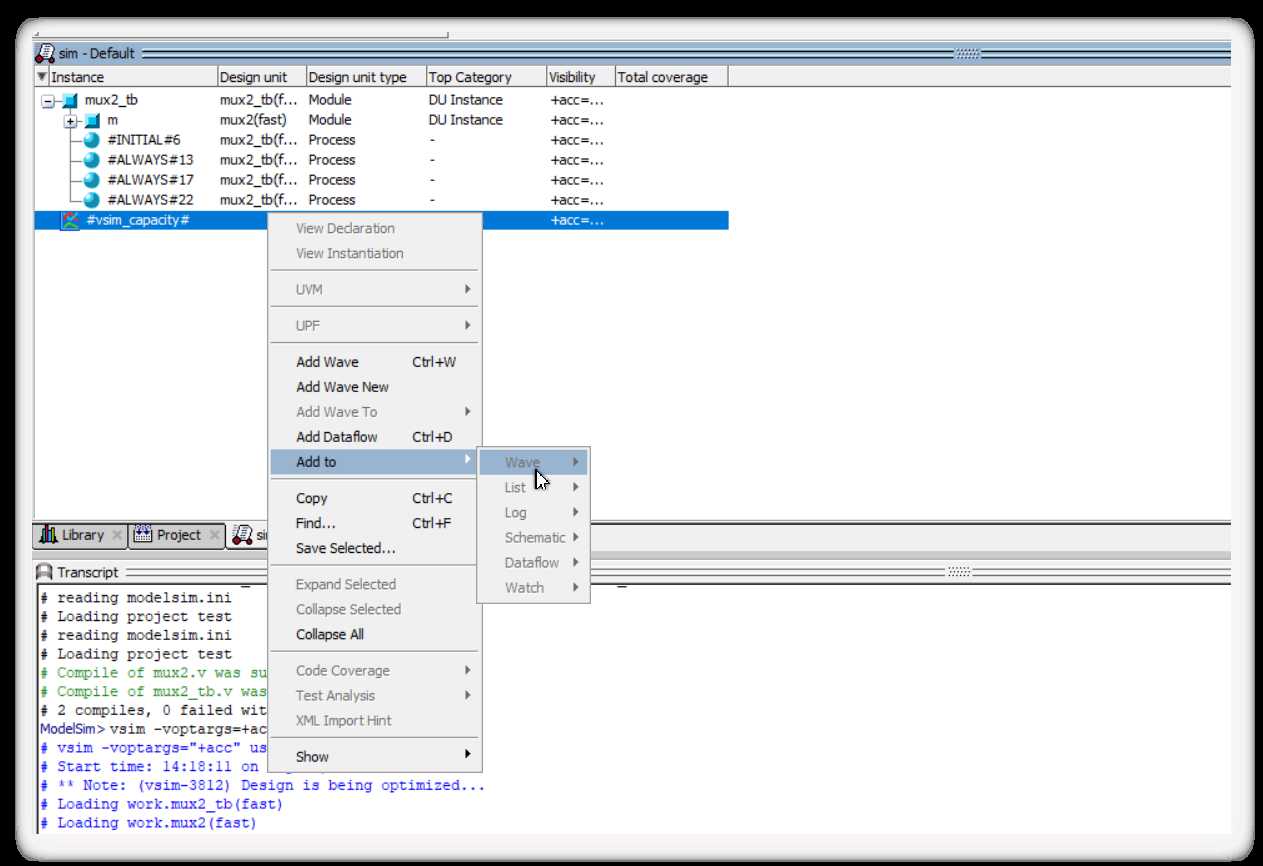

进入仿真阶段。这是后会自动出现sim界面。(还是在左下角可以看到)

这里是没有波形的,需要手动添加观测信号。

这里的wave是暗的,为什么?可以看到sim的亮线指在sim_capacity上,而非mux2_tb上,导致没有可以选择的观察信号。同理,如果指向其他的地方,被选择的观察信号可能是别的模块,比如被测模块。如果两个模块有同名变量且没有连接,那就可能出现多个同名不同值的波形。(这里值得注意,但凡是右击,都要确定光标所在,否则容易出错)

正确地添加信号后会出现wave(有些是浮动的,有些是嵌入的)

有信号名,但是没有波形。这里出现的问题是没有运行。光开显示器不开主机,有啥子用。运行的快捷键在运行时间的右侧,三种方式。第一个是正常运行,第二种是继续(一般有stop系统函数的时候使用较多,第三个一直运行。运行时间的位置比较明显,就是一堆快捷键中的数字输入框。

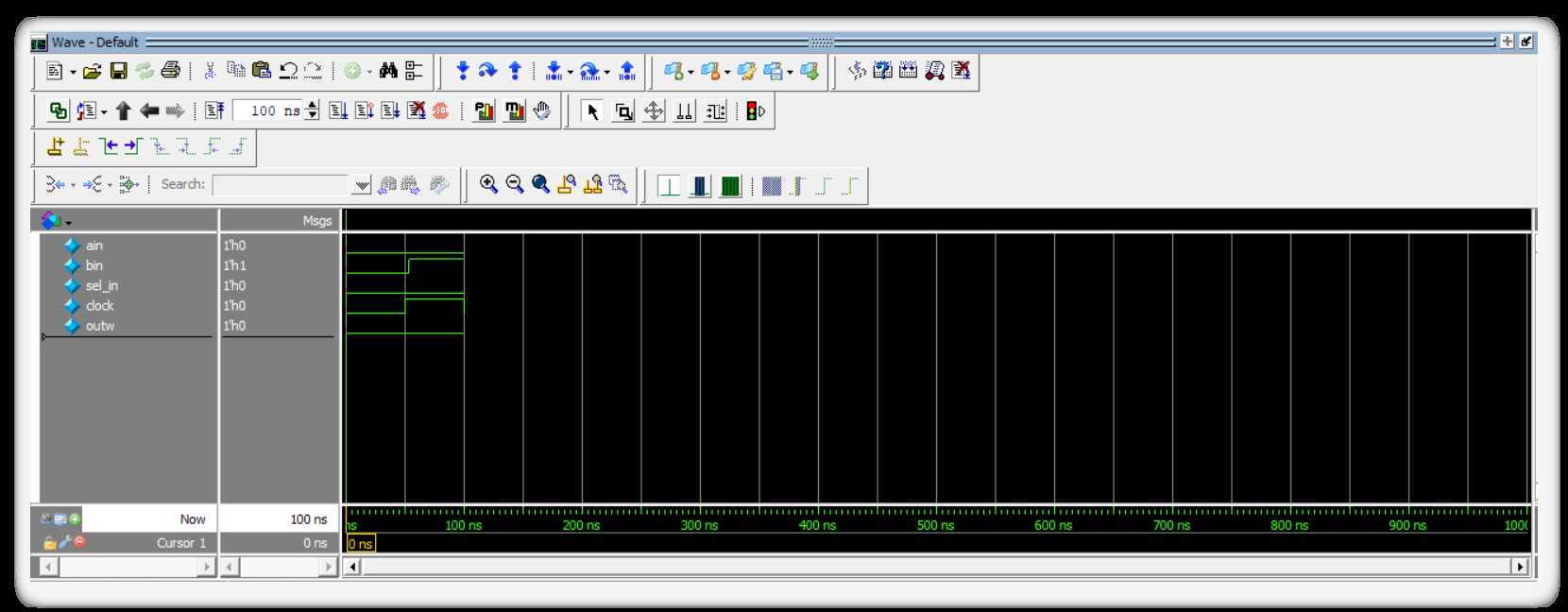

这是初始的波形,显然看着不爽。调整波形的常用按键:

基本上掌握这三个键基本的功能就可以使用了。放大缩小也重要,但是一看就知,这里就不说明了。

基于软件的顺序逻辑,如果想要修改Verilog源文件,就要关闭工程,修改文件,保存文件、保存文件、保存文件,然后再编译。重要的事情说三遍。modelsim的编译是不会提醒文件是否保存的。一定要自己保存,否则,你得到的一直是修改前的文件编译结果。

②基于联合仿真的波形修改

通过几次实验,发现使用重新启动编译的话,如果使用软件操作的话还不如直接重启后在启动联合仿真。比较合理的方法是使用现成的脚本,也就是联合仿真时的.do文件。在控制台再执行一次即可。

3、实验结果

基本了解了modelsim的波形仿真的基本操作。但是对于联合仿真的修改还是比较费时间,毕竟要编译库。不想记住的也可以重启,反正差别不大。联合仿真中会生成可执行工程文件,这个相当于一个快捷方式。这里说明一下。

以上是关于verilog中除法运算在modelsim仿真中只要一个时钟周期就能完成,实际上也是这样吗?的主要内容,如果未能解决你的问题,请参考以下文章