多个axi interconnect可以互联吗?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了多个axi interconnect可以互联吗?相关的知识,希望对你有一定的参考价值。

参考技术A 可以。AXI协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,需要加入一个AXIInterconnect模块,也就是AXI互联矩阵,作用是提供一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制。这个AXIInterconnectIP核最多可以支持16个主设备、16个从设备,也可以互相链接,如果需要更多的接口,可以多加入几个IP核。CPU的快速互联通道(QPI)详解

原文自:http://blog.csdn.net/hipercomer/article/details/27580323

翻译自:http://www.hardwaresecrets.com/article/Everything-You-Need-to-Know-About-The-QuickPath-Interconnect-QPI/610/1

自Intel有CPU开始,便一直采用的是称之为“前端总线(Front Side Bus, FSB)”的外部总线。前端总线是由内存和I/O共享的一条通往CPU的通道。新一代的Intel 处理器将内置内存控制器,所以该处理器将提供两个通道:连接CPU和内存的内存总线(memory bus)以及连接CPU和I/O的I/O总线。这个新增的I/O总线称之为快速互联通道(QuickPath Interconnect, QPI)。本文中,我们将解释其工作原理。

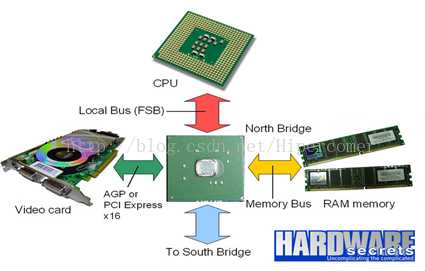

图1 传统Intel处理器架构

图1给出了传统的Intel处理器架构,图2是处理器内置内存控制器的新一代Intel处理器架构。

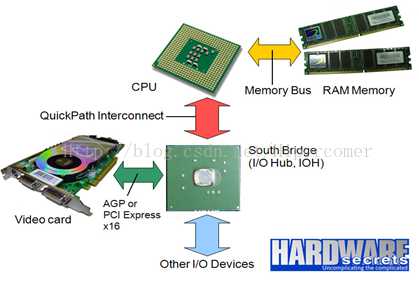

图2 新一代Intel处理器架构

事实上,AMD从2003年开始便在Athlon 64 CPU中采用相似的架构了。现在,所有AMD的CPU都已经内置内存控制器了。他们使用称之为HyperTransport总线来实现I/O通信。尽管HyperTransport和QPI目标相同、工作机制也类似,不过他们并不兼容。

顺便一提的是,技术上将QPI和HyperTransport并不能称之为总线而只是点对点连接。总线是指允许多个部件同时连接的一组导线。点对点连接指的是仅仅连接两个部件。尽管技术上称它为总线不太对,为了简便起见和我们还是这么叫吧。

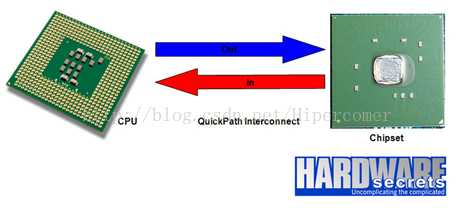

接下来我们谈谈QPI的工作原理,和HyperTransport类似,QPI为CPU和芯片组的连接提供了两个通道(lane),如图3所示。这样做,可以让CPU同时接收(读)和发送(写)I/O数据,而传统的FSB是不能实现这个目标的。

图3 快速互联通道提供分离的输入输出路径

说到芯片组,Intel将推行单芯片解决方案。因为在CPU中内置内存控制器几乎等价于将北桥内置到CPU中。图3中的Chipset的功能和南桥类似,功能上就像是一个“I/O集线器(I/O Hub)”或者用Intel的行话称之为“IOH”。

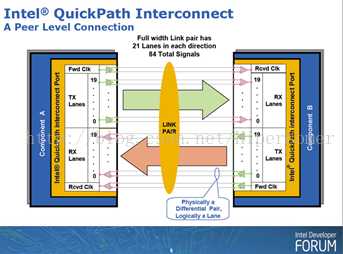

每个通道(lane)一次能传输20个比特位,其中16位为实际数据,4位是冗余纠错码(CRC)。QPI第一个版本的工作频率为3.2GHz并能够在一个时钟周期内传输两个数据(即DDR技术),这使得总线工作频率看起来好像是在6.4GHz(Intel使用GT/s为单位,表示十亿次传输/秒).由于一次可以传输16位,我们可以很容易计算得到一个通道上的数据传输峰值6.4GHzX16bits/8=12.8GB/s。也许有些人说QPI的最大理论峰值为25.6GB/s因为他们考虑两个通道同时提供的带宽。不过我们并不同意这种方法,这就像我们可以说高速公路上限速为130英里每小时因为单向限速为65英里每小时一样毫无意义。

所以和FSB比起来,QPI虽然传输更少的数据但是却可以在更高的频率工作。当前,最快的前端总线频率1600MHz(实际上工作在400MHZ,但是在一个时钟周期内传输四个数据)也能达到12.8GB/s,这和QPI一样快,但是QPI是在每个通道上都提供12.8GB/s。而且FSB要同时传输I/O数据和内存数据,所以QPI可用带宽要更高些。

QPI也比HyperTransport要快。当前HyperTransport能够达到的最大速度为10.4GB/s,但是当前Phenom处理器的只能达到7.2GB/s.所以,Intel Core i7 CPU的外部总线要比AMD的快78%。其他系列的AMD CPU如Athlon, Athlon X2的传输频率更低了,仅能达到4GB/s。

图4 差分对传输

顺着电子传输继续往下走,每个位的传输使用差分对(differential pair),图4所示。所以,每传输一位都要使用两根导线。QPI的两个通道一共使用了84根导线,这几乎是Intel传统CPU中FSB需要的导线数量的一半。所以,第三个有点便是前端总线可以使用更少的导线(第一个优点使将内存和I/O请求分开,第二个有点是将读写路径通道分开)。

QPI使用了和网络架构中很像的分层技术,一共有四层分别是物理层,链路层,路由层和协议层。

接下来我们看看QPI中引入的高级技术。

功耗模式

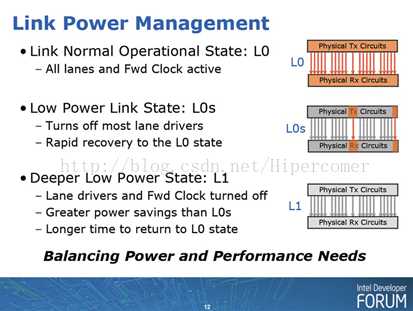

如图5所示,QPI提供以下两种功耗模式,分别称之为L0和L0s和L1. L0指的是QPI全速运行时的模式,在L0s状态时,为了节省能耗,数据线和驱动这些线的电路将被关掉。在L1状态时,所有的东西都会被关闭。当然,L1的唤醒时间将更长。

图5 功耗管理

可靠模式

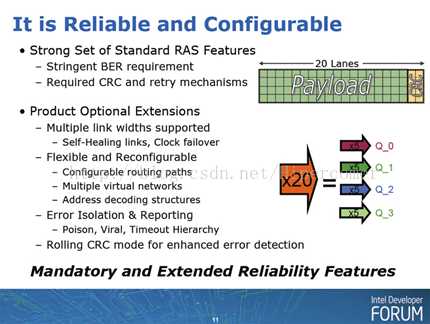

我们提到了QPI的数据路径是20位宽,我们并没有提到的是QPI允许每个通道被设置成4个五位宽的小通道,如图6所示。对于服务器市场环境来说,这种分割方法可以提高可靠性。不过对于桌面环境而言,QPI并不提供这个功能。

当这个功能打开后,如果接收器发现其与发射器之间的连接物理上已经被破坏了,它将关闭已经破坏的部分,然后每次传输更少的位数。这显然会降低数据传输速率,但是至少系统不会崩溃。

图6 可靠模式配置

以上是关于多个axi interconnect可以互联吗?的主要内容,如果未能解决你的问题,请参考以下文章

Linux PCI驱动框架分析:(Peripheral Component Interconnect,外部设备互联)

OSI 7层模型及相应延伸 (开放式系统互联模型Open System Interconnection Reference Model)