VLSI数字信号处理系统——第七章脉动结构设计

Posted 夏风喃喃

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VLSI数字信号处理系统——第七章脉动结构设计相关的知识,希望对你有一定的参考价值。

VLSI数字信号处理系统——第七章脉动结构设计

作者:夏风喃喃

参考:

(1) VLSI数字信号处理系统:设计与实现 (美)Keshab K.Parhi/著

(2) socvista https://wenku.baidu.com/u/socvista?from=wenku

文章目录

一. 引言

脉动阵列:多个相同的处理单元(简称PE)按一定互联规则组成的网络,称为脉动阵列。脉动阵列可以是一维线形、二维三角形、二维矩形、二维六边形、二维二叉树型、三维长方体形等等。

脉动阵列特点:

- 每一个节点,也就是PE,也称为胞元,都是相同的。

- 每个PE只与其相邻的PE进行通信,也就是说PE之间的通信具有局部性,而且通信是规则的。如果通信不是局部的而且不规则,那么网络中各PE的连接关系将会很错乱,硬件上进行布局布线也会遇到困难。

- 每个PE都有其局部的存储器,也就是PE的某些边带有延时,延时在硬件上对应于寄存器。这说明脉动阵列数据储存具有局部性,同时这也是流水运行的必要条件。

由于脉动阵列的以上特点,造成PE之间的高度流水化、规则化,因此系统吞吐率非常大且易于VLSI的实现。工程上为了扩大脉动阵列的用途,会引入一些弛豫,比如允许使用邻近(靠近但不是相邻)互联,使用数据广播操作,以及在系统中使用不同的胞元,尤其是边界上的胞元往往和网络内部胞元不太一样。

二. 脉动阵列设计方法原理

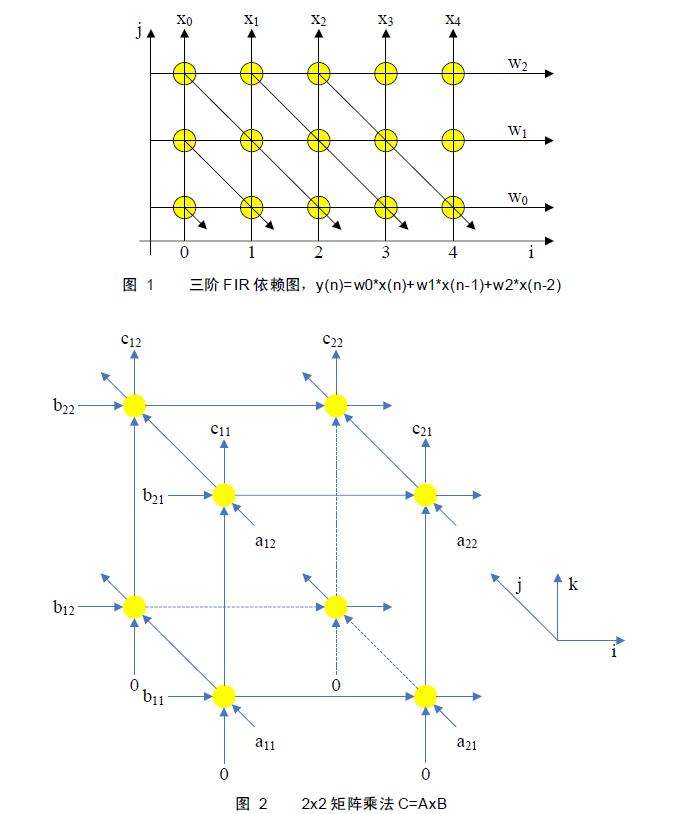

规则迭代算法依赖图:

不是任意的算法都可以用脉动阵列来实现,只有规则的迭代算法,画出该算法的依赖图(DG),才能用投影技术设计出脉动结构。如果依赖图的任一节点沿某个方向的边存在,则称依赖图是规则的,通俗的说,依赖图的所有节点具有相同形式的边。

设计方法步骤:

- 投影矢量 d T = [ d 1 d 2 ] d^T=[d_1\\quad d_2] dT=[d1d2]:位移为d或者d的倍数的两个节点由同一个处理器执行。

- 处理器空间矢量 P T = [ p 1 p 2 ] P^T=[p_1\\quad p_2] PT=[p1p2]:任何标示为 I T = [ i j ] I^T=[i\\quad j] IT=[ij]的节点将被处理器以 P T I P^TI PTI处理。

- 调度矢量 S T = [ s 1 s 2 ] S^T=[s_1\\quad s_2] ST=[s1s2]:任何标示为 I T = [ i j ] I^T=[i\\quad j] IT=[ij]的节点在时间 S T I S^TI STI执行。

- 硬件利用率

H

U

E

=

1

/

∣

S

T

d

∣

HUE=1/\\vert S^Td\\vert

HUE=1/∣STd∣:同样的处理器执行两次任务间隔

∣

S

T

d

∣

\\vert S^Td\\vert

∣STd∣时间单位。

一个问题可选择不同的投影、处理器空间矢量和调度矢量设计出很多脉动结构。这些矢量必须满足下面推导的可行性限制调条件: - 处理器空间矢量 P P P和投影矢量 d d d必须正交, P T d = 0 P^Td=0 PTd=0。

- 如果节点A和B映射到同一个处理器,则它们不能在同一时间执行, S T d ≠ 0 S^Td≠0 STd=0。

- 边映射:如果依赖图中包含边 e e e,则在脉动阵列中引入一条延时为 S T e S^Te STe的边 P T e P^Te PTe。

三. FIR脉动阵列

3.1 设计B1(输入广播,结果移动,权重保持)

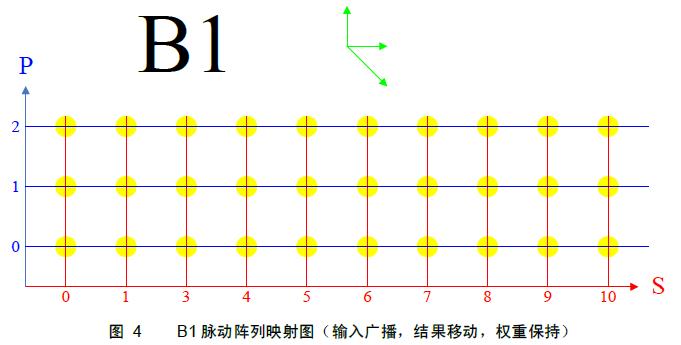

把DG图所在的i-j空间投影到一维脉动阵列空间。一维脉动阵列是一个2维空间,一个维度是PE空间,另一个维度是时间;同理二维脉动阵列是一个3 维空间,其中两个维度形成PE平面网络,另外一个维度是时间。对一维脉动阵列,时间轴不能和PE轴平行;对二维脉动阵列,时间轴不能和PE平面平行,即可行性限制条件。

如图4,蓝色坐标轴P是PE轴,红色坐标轴S是时间轴,图中的水平蓝线和竖直红线清楚的显示了节点(黄色)是如何投影到PE轴和时间轴的,这种投影的物理意义是:所有在同一条竖直红线上的节点在同一个周期被调度执行;所有在同一条水平蓝线上的节点在同一个处理单元被执行。

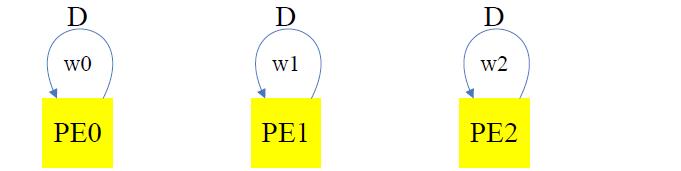

脉动硬件电路构造:

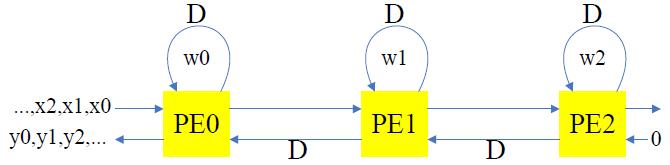

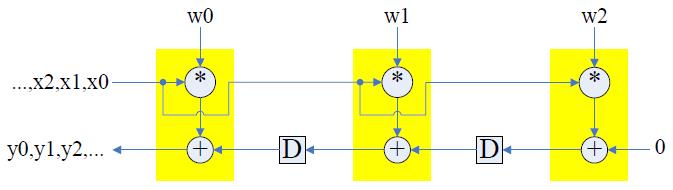

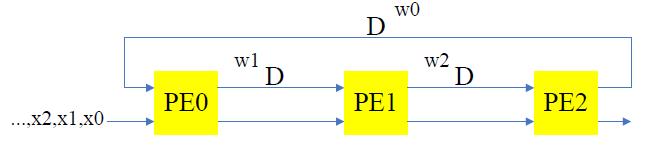

(1)可以看出图4所需的线形脉动网络包含3个PE,在硬件上可以先画出三个PE单元,如下图

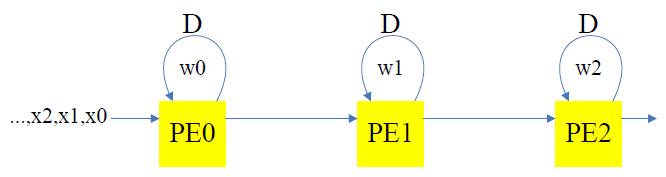

(2)接下来,需要把DG中节点的边映射为各个PE之间的互联关系。对于

[

1

,

0

]

T

[1,0]^T

[1,0]T方向的权值w边(水平向右),权值边连接相邻的两个水平节点,将该边投影到S上,跨越一个周期,将改变投影到P上,位于同一PE,这就表示,权值边在硬件上是同一个PE上延时一个周期的连线,如下图示

而

[

0

,

1

]

T

[0,1]^T

[0,1]T方向的输入x边,投影到S没有跨度,投影到P是从低序号PE到高序号PE的边,反映到硬件上就是

最后,在看

[

1

,

−

1

]

T

[1,-1]^T

[1,−1]T方向的输出y边,投影到S,跨越一个周期,投影到P,从高序号PE到相邻的低序号PE,反映到硬件上就是

(3)得出脉动结构图,结合DG中节点的具体内容,即可画出最终电路。图1节点的内容是一个乘法加法的级联单元,最终电路图如下示

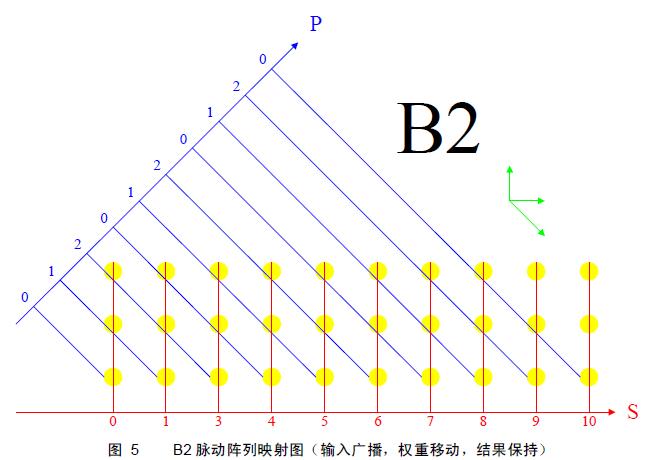

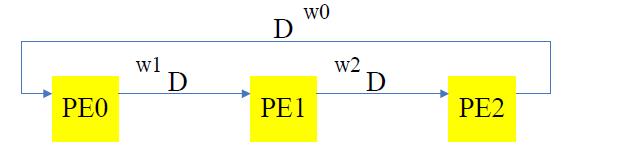

3.2 设计B2(输入广播,权重移动,结果保持)

脉动硬件电路构造:

(1)首先要用矢量来表示脉动空间的两个坐标轴P和S,这里令

S

=

[

1

0

]

T

S=[1\\quad 0]^T

S=[10]T,

P

=

[

1

1

]

T

P=[1\\quad 1]^T

P=[11]T,显然P和S不平行(叉积为0)。任一节点

[

i

j

]

T

[i\\quad j]^T

[ij]T在P轴和S轴的投影,就是点积,即

[

i

j

]

T

[i\\quad j]^T

[ij]T在

S

⋅

[

i

j

]

T

S·[i\\quad j]^T

S⋅[ij]T周期被调度到

P

⋅

[

i

j

]

T

P·[i\\quad j]^T

P⋅[ij]T处理器执行。

可以发现同一周期最多只有3 个节点被映射到P 轴的处理器执行,也就是说只需3个处理器便可以保证构造出功能正确的脉动阵列,画出三个PE单元,如下图 以上是关于VLSI数字信号处理系统——第七章脉动结构设计的主要内容,如果未能解决你的问题,请参考以下文章

(2)在DG中存在三条边,分别是

[

1

,

0

]

T

[1,0]^T

[1,0]T的权值w边、

[

0

,

1

]

T

[0,1]^T

[0,1]T的输入x边以及

[

1

,

−

1

]

T

[1,-1]^T

[1,−1]T的输出y边,如图5 的绿线所示。将

[

1

,

0

]

T

[1,0]^T

[1,0]T的权值w边分别投影到S轴和P轴,有

S

⋅

[

1

0

]

T

=

[

1

0

]

T

⋅

[

1

0

]

T

=

1

S·[1\\quad 0]^T=[1\\quad 0]^T·[1\\quad 0]^T=1

S⋅[10]T=[10]T⋅[10]T=1和

P

⋅

[

1

0

]

T

=

[

1

1

]

T

⋅

[

1

0

]

T

=

1

P·[1\\quad 0]^T=[1\\quad 1]^T·[1\\quad 0]^T=1

P⋅[10]T=[11]T⋅[10]T=1,也就是说权值脉动阵列中是有低序号PE 流向高序号PE且跨越一个周期。

接下来是

[

0

,

1

]

T

[0,1]^T

[0,1]T的输入x边,分别投影到S轴和P轴,有

S

⋅

[

0

1

]

T

=

[

1

0

]

T

⋅

[

0

1

]

T

=

0

S·[0\\quad 1]^T=[1\\quad 0]^T·[0\\quad 1]^T=0

S⋅[01]T=[10]T⋅[01]T=0和

P

⋅

[

0

1

]

T

=

[

1

1

]

T

⋅

[

0

1

]

T

=

1

P·[0\\quad 1]^T=[1\\quad 1]^T·[0\\quad 1]^T=1

P⋅[01]T=[11]T⋅[01]T=1,意味着输入x也是从低序号PE流向高序号PE,但没有时间上的延迟,也就是数据广播结构。

最后是

[

1

,

−

1

]

T

[1,-1]^T

[1,−1]T的输出y边, 分别向S轴和P轴,有

S

⋅

[