7nm高性能智能驾舱芯片算力与架构设计场景分析

Posted 芯擎科技SiEngine

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了7nm高性能智能驾舱芯片算力与架构设计场景分析相关的知识,希望对你有一定的参考价值。

2021年3月19日,由ATC汽车技术平台旗下的ATC会议举办的「2021汽车车载芯片技术峰会」在上海顺利召开。作为业内技术最为密集、讨论话题最为前沿的汽车技术交流会,ATC汽车技术会议特邀合作伙伴芯擎科技产品管理高级总监蒋汉平博士,作为本届芯片峰会的演讲嘉宾分享《7nm高性能智能驾舱芯片算力与架构设计场景分析》。蒋博士系统的阐述了作为高端数字驾舱车规芯片所应具备的五个必选项。

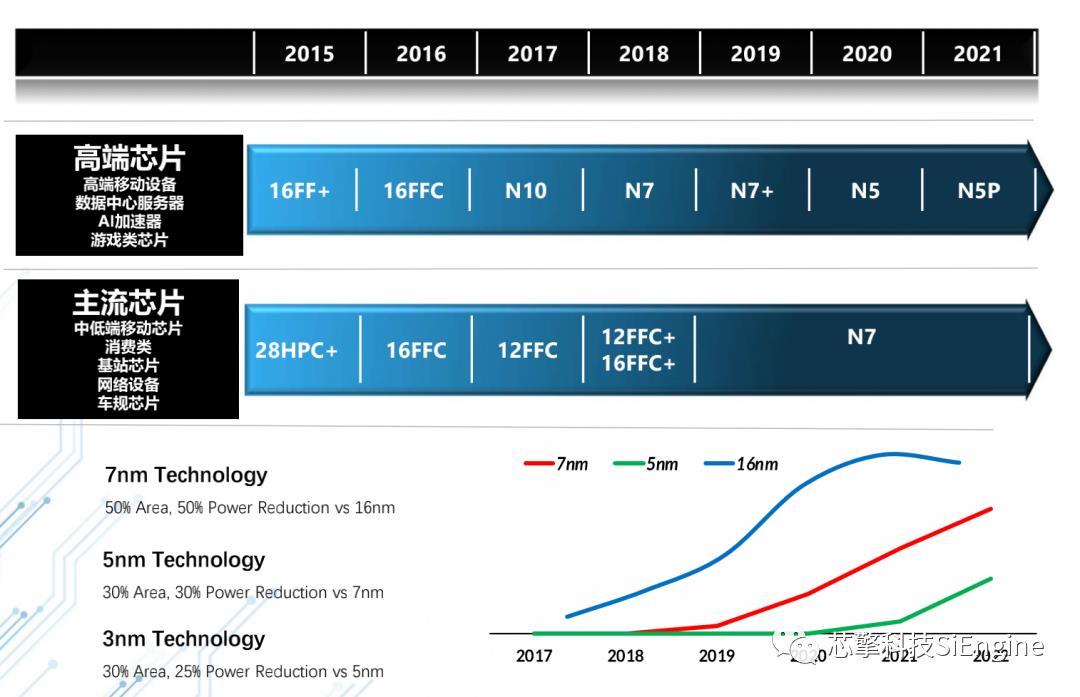

7nm工艺制程是高性能智能驾舱车规芯片的必选项

相对于10+nm, 7nm的工艺节点会带来显著的优点:

芯片集成度更高。单位面积的晶圆上可以放置更多的逻辑门,同时封装面积变小,节约了晶圆成本和封装成本,进一步节约了成品芯片在单板上所占的面积,使得相同大小的电子产品功能更多,速度更快。

芯片耗电量更低。同样大小的逻辑电路做出来,用更先进的工艺会导致耗电量更低,进而导致功耗变低。

响应速度更快。单管开断速度更快,同样的逻辑电路能够跑到的主频更高,性能大幅提升。

针对10+nm的工艺节点,比对了7nm的优势: 相比起10+nm节点工艺,7nm平均晶体管密度接近100MTr/mm2,是10+nm工艺的3.3倍,在同等功耗上提供35~40%的速度提升或者可以降低65%的功耗;同时7nm相对10+nm,提供更高占比的动态功耗(>90%),这样才能真正发挥各个计算单元(CPU、GPU等等)有效算力,同时降低静态功耗,减少漏电效应,提供高效的热管理。所以针对高性能的数字驾舱SOC,7nm车规是必选项性。

蒋博士说,工艺和设计是相辅相成的。代工厂(Fab)和芯片设计公司(fabless)的合作模式需要相向而行:设计公司拿自己设计的芯片来投产,然后进行出厂检测;代工厂进行代工生产和工艺改进,中间会出现各种各样的问题。比如:良率低了到底是设计的时序余量不足,还是工艺波动;性能差了是设计的环路稳定性不够,还是工艺参数设置错误?工艺参数的提取,仿真模型的构建与修改,同一芯片不同工艺下的参数对照,最终都是要Fab和Fabless共同努力的结果。针对不同工艺,芯片设计要做的工作也不尽相同,冗余电路、备份设计都是需要在芯片设计阶段增加的内容, 这些都是先进工艺才会出现并考虑的问题,需要长期合作积累经验才能完成最终的量产,没有捷径可走。

他特别强调:7nm的设计难度更大,对芯片设计公司而言也是机会,为何设计难度大是优点呢?难度高,增加了电子行业的马太效应,强者越强,弱者恒弱。护城河加大,行业壁垒增高,后来者难以攀登, 和10+nm半导体工艺的百花齐放相比,很多在10+nm大放异彩的半导体公司都在7nm制程处遭遇到了苦头。芯擎的工程师团队在10nm及更先进工艺制程上积累的量产经验在业界都是领先的,这样无疑为高性能的智能驾舱芯片的量产提供经验和能力保证。

功能安全和信息安全是车规芯片的必选项

汽车电子系统愈加复杂,由电气、电子系统故障导致的风险也越来越高,区别与移动终端芯片的架构,如何量化评估汽车功能是否安全,如何减少、规避风险,如何做到汽车功能安全和信息安全等问题变得十分突出。

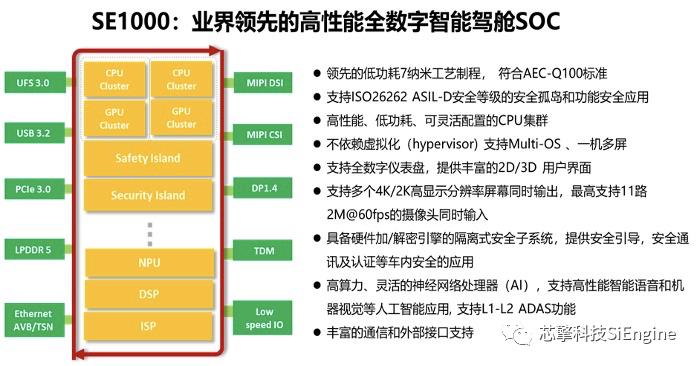

芯擎公司拥有一个专门的功能安全工程师团队,涵盖组织内的所有功能安全项目,我们有一些传统的设计,比如架构设计中某些部分的内存保护和监视器,同时也采取了针对汽车驾驶场景的安全保证措施,而不仅仅是对硬件组件负责,评估系统中元件故障的临界点。比如,根据 ISO26262标准规定,仪表盘的关键数据和代码与娱乐信息系统属于不同功能安全等级,我们芯片上安全岛(Safety island)的安全等级达到ASIL-D, 通过与各个子系统及接口的配合,保护车内仪表盘屏幕显示的特定部分达到ASIL-B,从而实现性能和安全性之间的平衡。

数字驾舱通过MCU/ECU等进行通信,使数字座舱能提供的信息和反馈越来越实时和高效。为保证安全就需要厂商与各大互联网公司和电信企业之前的密切合作来保证云端数据和车身数据的安全。芯擎采用了信息安全岛(Security Island)的设计加强对个人和车辆的数据保护,芯片支持SM2/SM3/SM4国密算法。

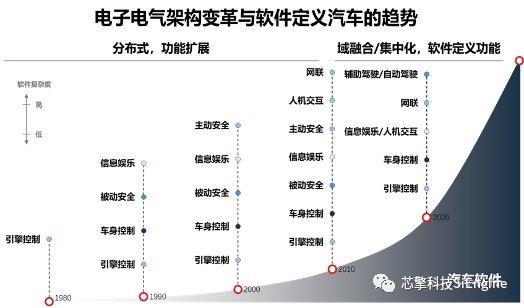

软硬件解耦是电子电气架构演进和软件定义汽车的必选项

进入2020年汽车的变革呈现出加速激变的现象,整个行业面临着新的挑战,自动驾驶,智能网联,软件定义汽车,应对这个挑战主要需要三个方面的准备:

电子电气架构

芯片

软件生态

汽车软件复杂度的发展趋势,基本上呈现出指数增长的趋势,这个趋势其实可以反映出汽车对芯片计算能力的需求趋势,也反映出汽车电子电子系统的变化趋势。第一个阶段是分布式,功能扩展阶段,对新功能的需求持续做加法,但是一直做加法会遇到瓶颈,这种模式难以为继;第二个阶段,也就是域融合/集中化阶段,逐渐由软件来定义功能,整个过程是计算逐渐集中化和算力迅速增长的过程。分布式架构的软硬件是耦合在一起的,由不同供应商提供,升级很难,中央计算架构下软硬件分离,便于更新升级,集中化架构处理跨域功能主要由中央计算单元处理,架构和管理要简单很多。

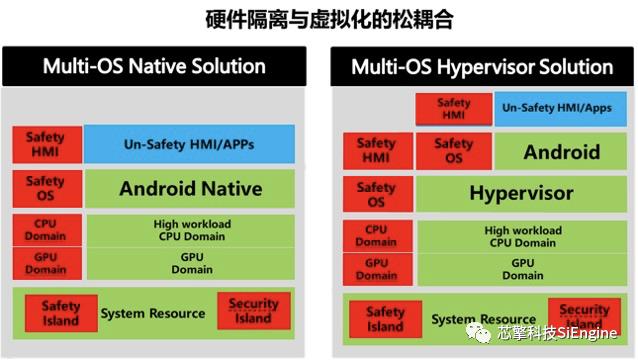

高性能的数字驾舱芯片采用异构计算架构,系统计算资源多样化,至少包括CPU/GPU/ISP/DPU/NPU/DSP等等,还包括大量的车内高速接口,虚拟机管理的概念被引入智能座舱操作系统,但是Hypervisor在车内软硬件适配过程中还是一个新生事物,缺乏丰富开发经验的软件人员和成熟高效的硬件适配方案,不完全依托Hypervisor实现不同功能安全等级OS共存成为快速推进软件一体化聚合的关键。

芯擎科技的架构师根据功能安全不同要求将主要计算引擎分成算力大小不同的域,在单一芯片架构上形成了硬件隔离方案,不同的硬件域可以分别支持实时性要求高,具有功能安全的OS和计算密集型的OS;随着Hypervisor方案的成熟,后期可以平滑过渡到在算力较大的域上支持Hypervisor,从而差异化分布不同要求的OS,在这个演进过程中,芯片架构和软件架构完全相同,通过简单明晰的配置就可以规避Hypervisor成熟过程中引入的不确定性,提升生态适配能力与量产时间。

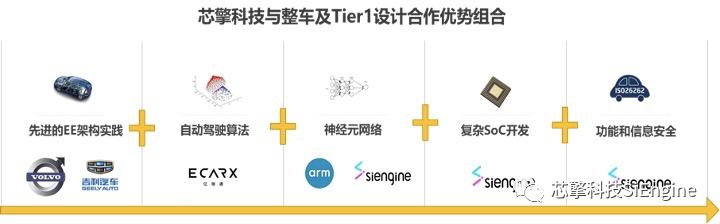

车企引领需求导入是提升芯片量产时间的必选项

此前智能座舱的各功能都需要不同专用芯片实现,如此一来不仅提升了车企产品研发的复杂度和研发投入,后期想要在已有系统上进一步扩展功能,也比较困难。目前,智能座舱已成为各路玩家的新战场,无论是新势力造车力量和传统车企已经主动打破边界,由被动的接受通用芯片和生态提供的解决方案,转变到亲自下场制定芯片的规格和量产车型。智能座舱在国内车企的参与下快速渗透,他们积极寻找智能网联、自动驾驶的转型升级;同时意图将对数据的闭环控制和算法的闭环优化完全掌控在自己手上,所以真正“完美”的数字驾舱方案一定是与整车紧密耦合的,这个与目前互联网大厂自己制定芯片规格,并搭建数据服务平台如出一辙,那些仅仅借某一领域的能力结合生态系统去驾驭数字驾舱和自动驾驶的芯片设计公司,很难高效的适配快速的技术演进与需求膨胀。

蒋博士从芯擎数字驾舱芯片规格制定和架构设计过程中,明显感到车企比如吉利集团和亿咖通发挥的巨大作用:吉利集团提供了目前和未来先进的电子电气架构及整车生态,芯擎芯片在规格指定时就针对未来几年的量产车型的关键应用进行SOC架构设计;在工程阶段,所有的参考设计、软硬件系统架构、成本模型都按照指定车型进行计划;在量产阶段,直接将已经量产的生态系统平移到新的平台上,所有的研发和生产路径都围绕芯片量产上车这个环节展开,数据和算法按照车企的整体规划进行定制和管理,不存在所谓生态系统里“大海捞针”,这样需求的准确性和时效性得到了最大程度的保障。这也是芯擎公司对即将量产的数字驾舱芯片信心十足的关键所在!

精准高效的算力匹配是支持电子电气架构变革的必选项

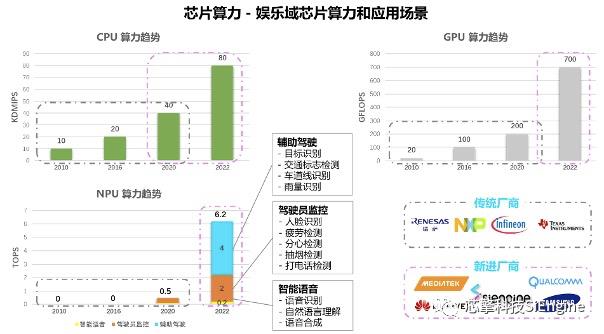

芯片是电子电气架构变革的基石,为了配合域融合/中央计算的趋势,芯片算力的变化趋势和预埋能力提升也很明显,而且呈现出加速增长的趋势。

过去,车内娱乐芯片市场的传统厂商由瑞萨、恩智浦、TI、英飞凌等汽车芯片巨头垄断。芯擎科技作为高端国产车载芯片设计公司,强势入局智能驾舱市场,蒋博士初步揭示了即将量产并提供参考设计的SE1000场景规格。

SE1000是采用业界领先的7纳米工艺制程设计的新一代高性能、低功耗车规级智能座舱芯片,赋能日益丰富的车载信息娱乐系统。高性能定制CPU集群,通过面向异构计算而精心设计的SOC系统,可以为用户提供卓越的性能体验。内置高性能嵌入式AI神经网络处理单元,提供更多个性化的智能语音、机器视觉及辅助自动驾驶体验。新一代多核心的图形处理单元,可以动态根据负载进行资源分配;一机多屏多系统,支持多个高分辨率屏幕同时输出;内置高性能音频信号处理单元及丰富的音频接口,为用户提供丰富超凡的音视频娱乐体验。具备高安全等级的“安全岛”设计,满足ISO26262车规认证,确保汽车功能安全;专业的硬件加/解密引擎为车载应用提供了安全信保证。同时,提供丰富的高性能通信及外围接口支持能力。

图注:从左往右第三位系湖北芯擎科技有限公司产品管理高级总监 蒋汉平博士

作为本届汽车车载芯片应用技术峰会的重要环节,蒋汉平博士受邀作为访谈嘉宾参与本届的圆桌论坛,现场与多位业内领袖以及汽车领域从业者进行深度交流,并展开了精彩的头脑碰撞,共同探讨汽车芯片行业发展的热点难点技术问题,他认为,目前芯片行业处于变革时间,国内的芯片设计企业应该尽快的抓住行业的契机,把握好方向,发展重点行业,解决芯片“卡脖子”问题,进而缩小与先进国家的差距,完成中国芯片设计公司的使命与责任。

以上是关于7nm高性能智能驾舱芯片算力与架构设计场景分析的主要内容,如果未能解决你的问题,请参考以下文章

独家重磅!华为开发者大会前瞻:鲲鹏产业链的3点超预期和2个进度突破