[架构之路-20]:目标系统 - 硬件平台 - 嵌入式系统硬件电路基础:架构设计流程总线外设基本电路编码

Posted 文火冰糖的硅基工坊

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了[架构之路-20]:目标系统 - 硬件平台 - 嵌入式系统硬件电路基础:架构设计流程总线外设基本电路编码相关的知识,希望对你有一定的参考价值。

目录

前言:

本文对嵌入式系统硬件的基础知识进行快速概览,但并不深入硬件细节。

第1章 嵌入式系统软硬件架构概览

1.1 什么是嵌入式系统

1.2 嵌入式系统发展历程

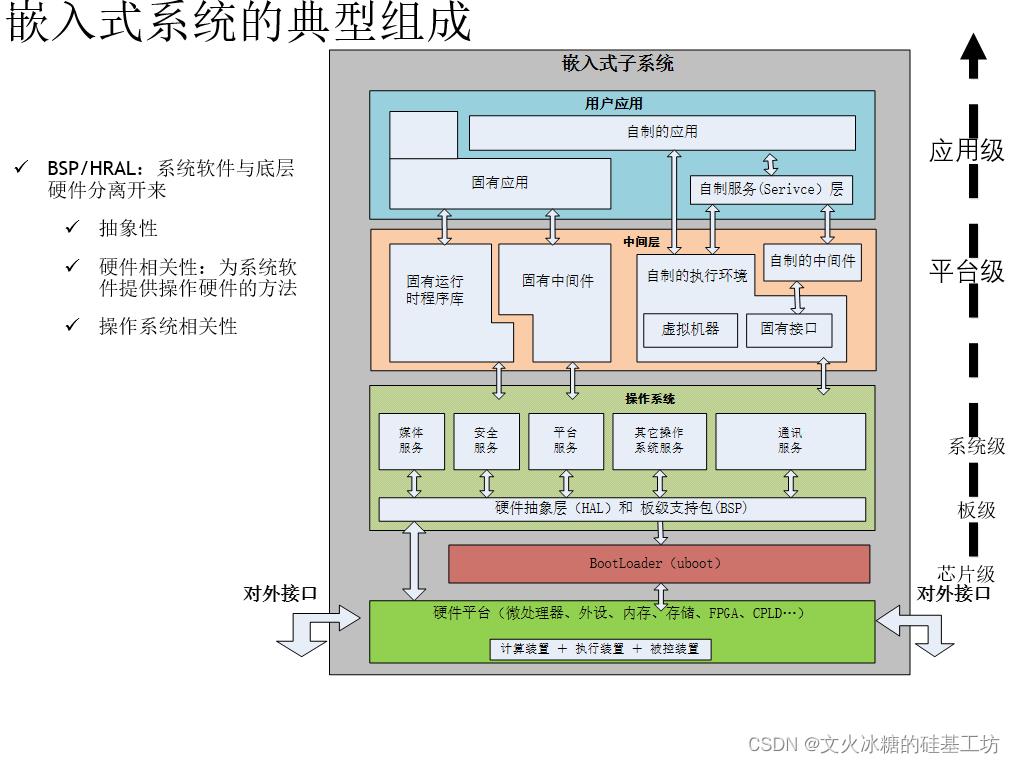

1.3 嵌入式系统软件+硬件架构

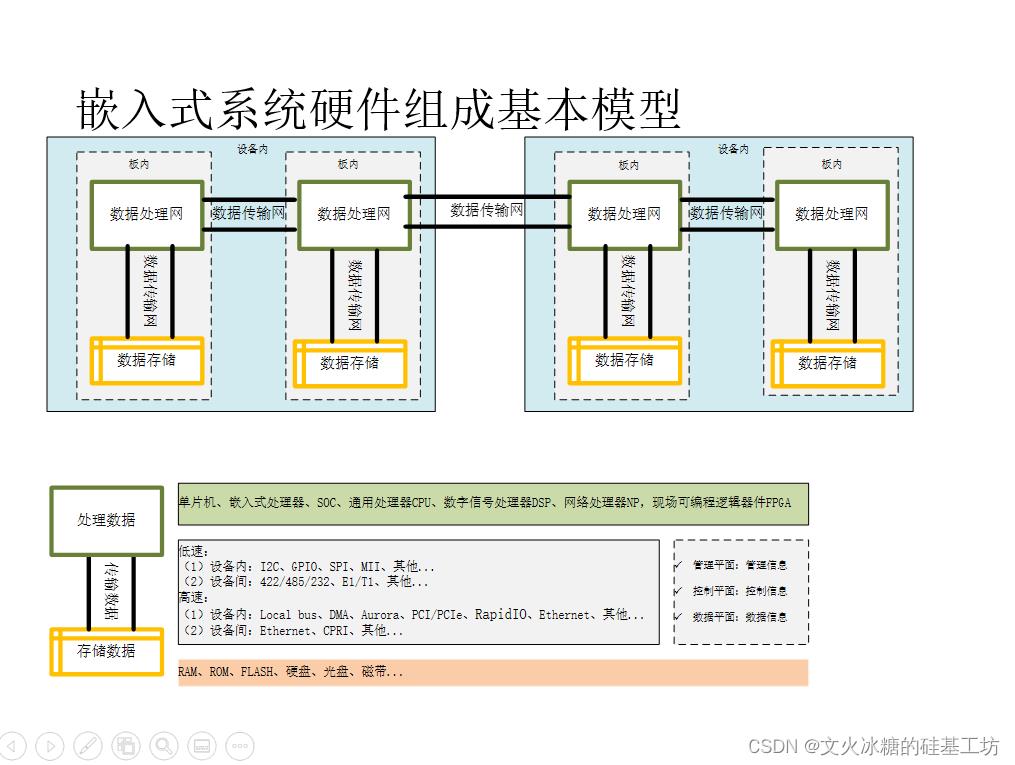

1.4 嵌入式系统的模型

1.5 嵌入式系统的硬件设备树

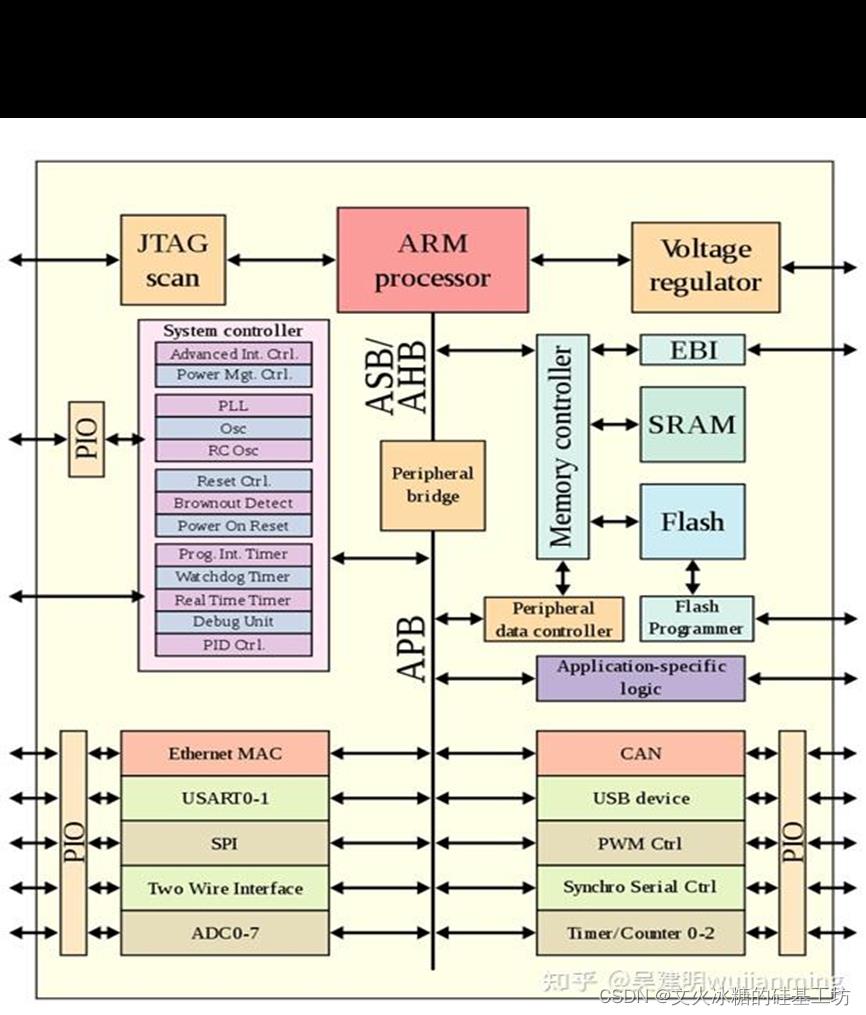

1.6 嵌入式SOC芯片内部架构

第2章 硬件电路设计基础

2.1 嵌入式硬件电路设计流程

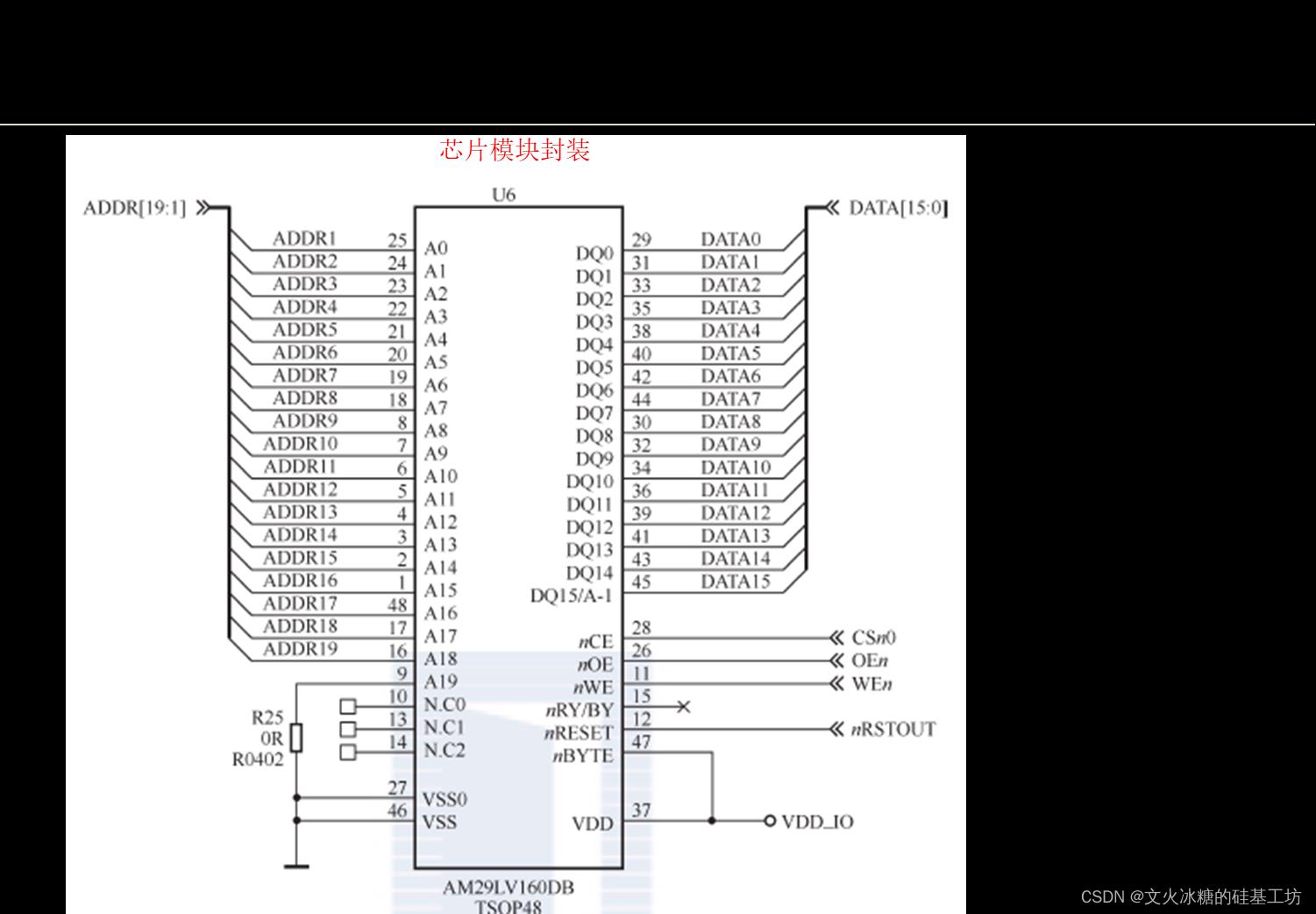

2.2 原理图设计

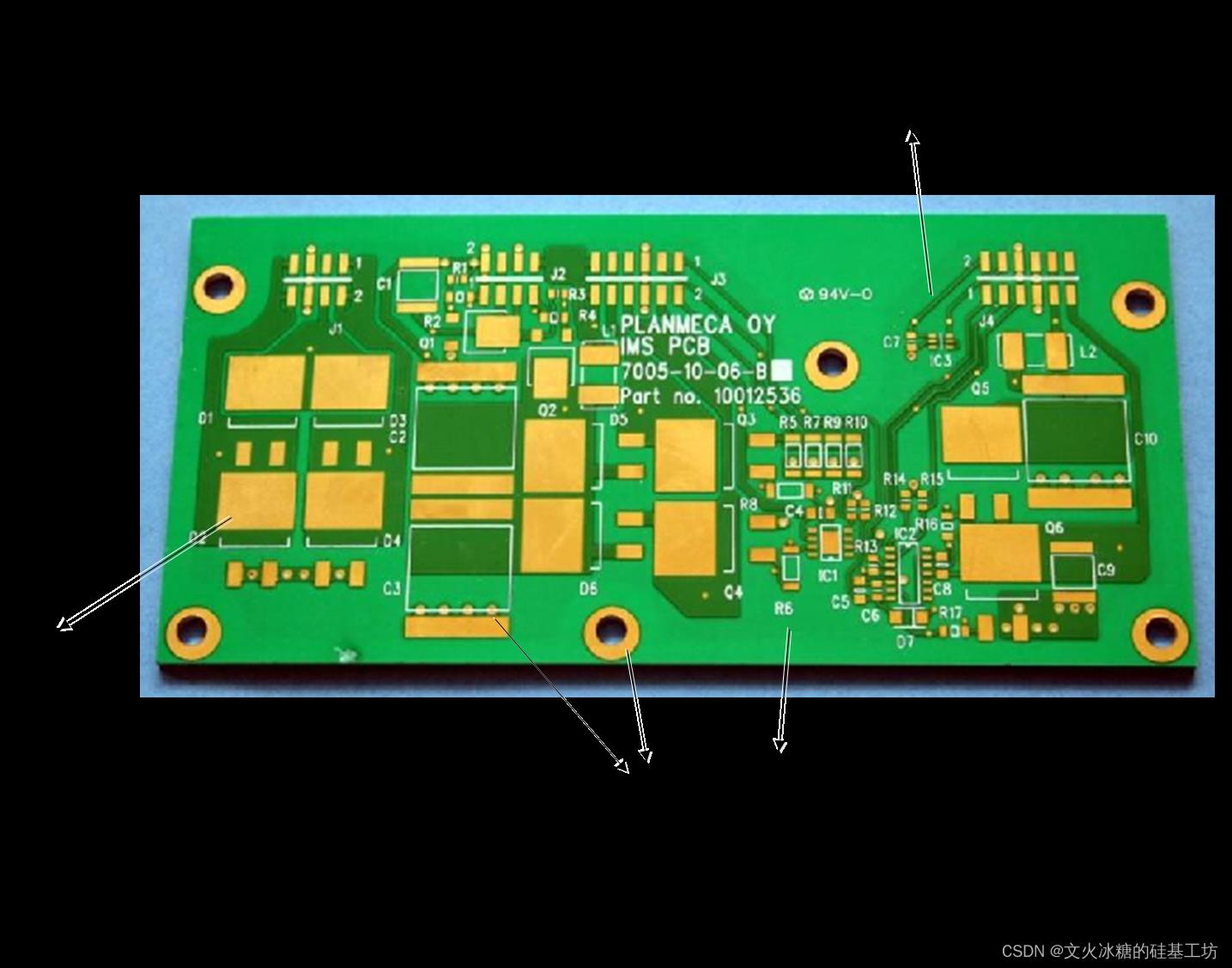

2.3 PCB设计

2.4 PCB生产与焊接

2.5 CPLD编程

2.6 FPGA编程

第3章 嵌入式系统硬件基础电路

3.1 逻辑电路

3.2 组合电路

3.3 时序电路:基本架构

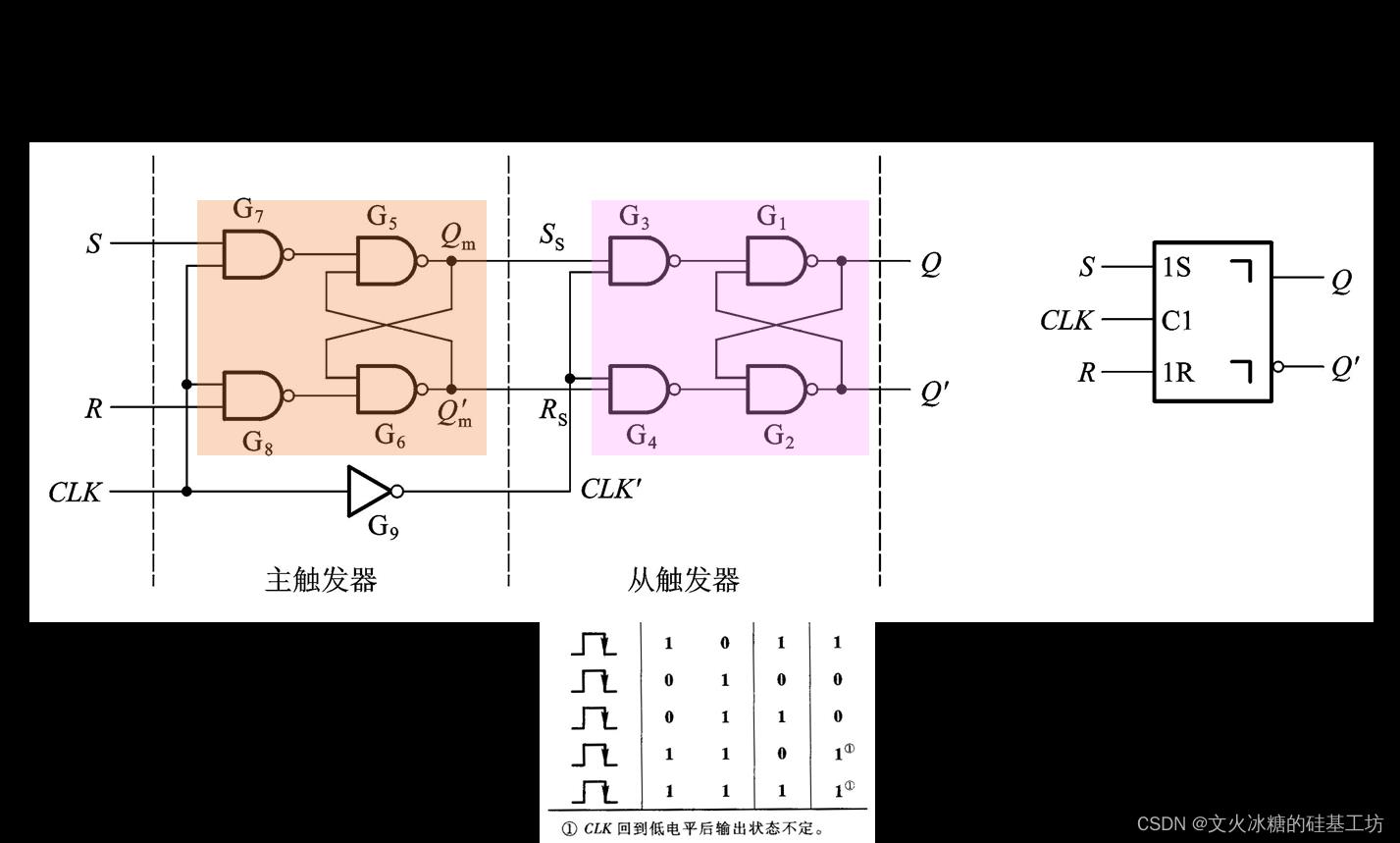

3.4 时序电路:触发器电路

3.5 时序电路: RS触发器电路

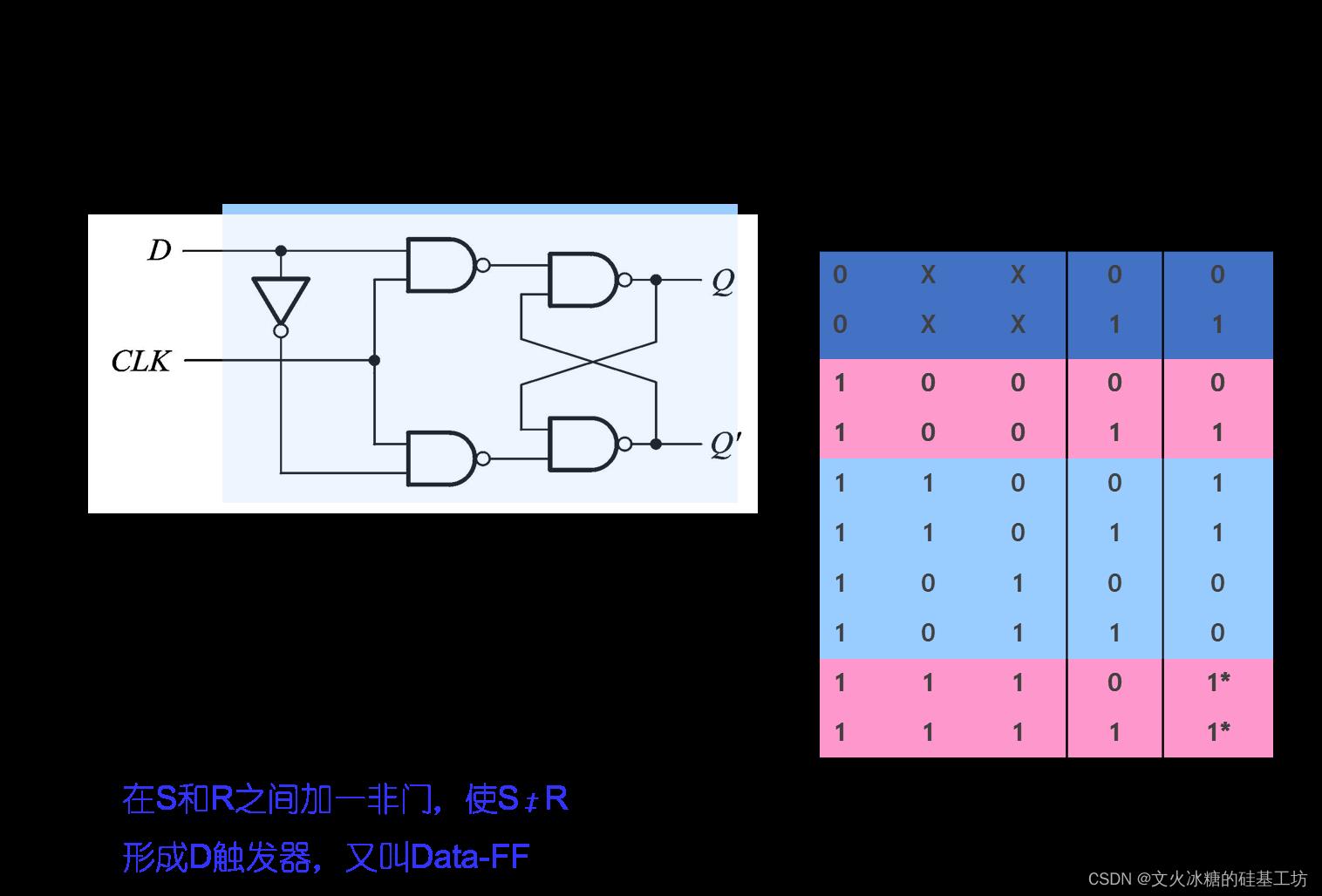

3.6 时序电路:D触发器电路

3.7 三态门电路

3.8 PLD内部结构

3.9 PLA门阵列

3.10 CPLD内部结构

3.11 FPGA内部结构

第4章 嵌入式系统的硬件组成

4.1 嵌入式处理器

(2)微处理器体系机构

(3)RISC处理器结构

(4)SOC 芯片内部架构

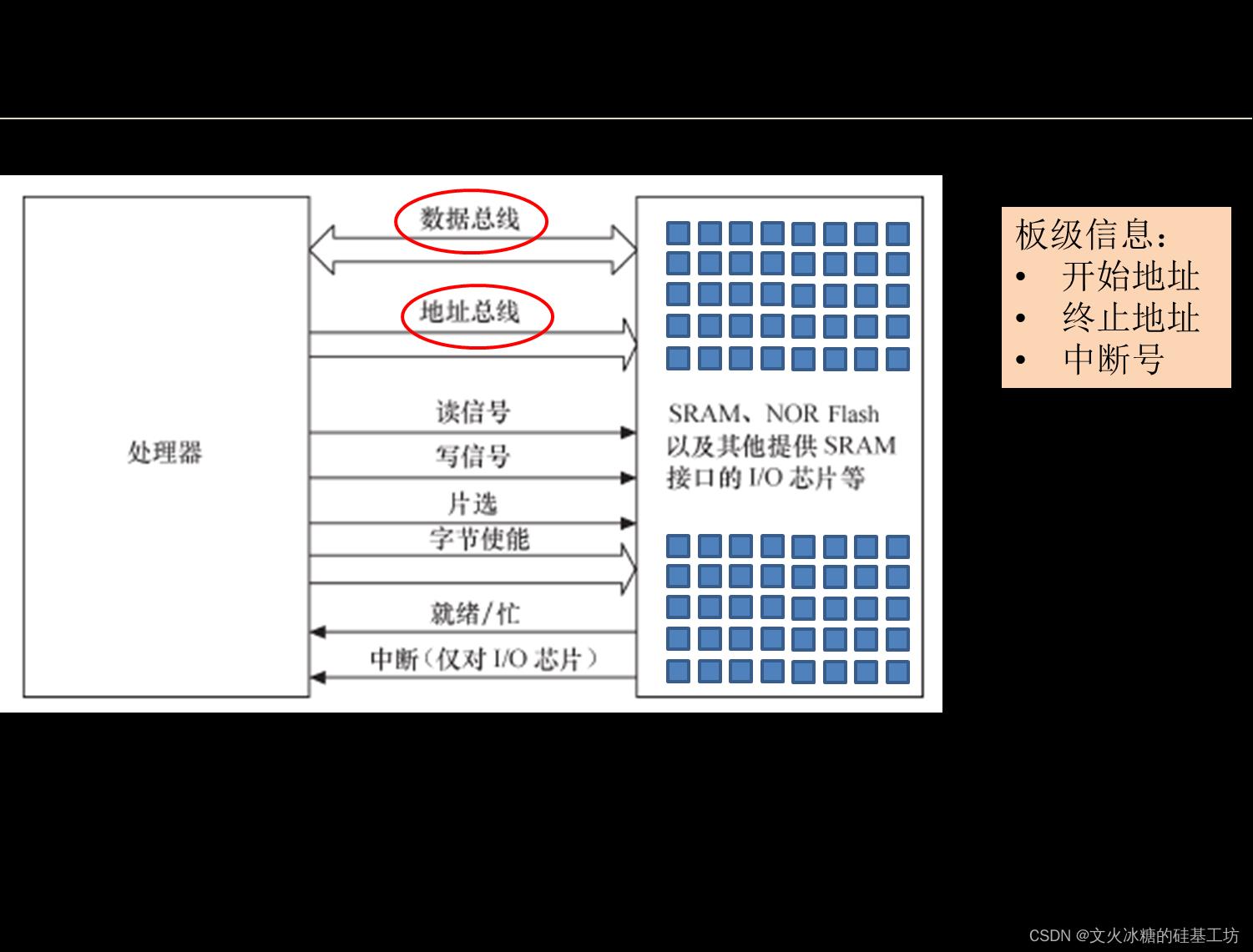

4.2 并行总线

(1)Local bus

(2)PCI总线

4.3 地址空间

4.4 内存架构

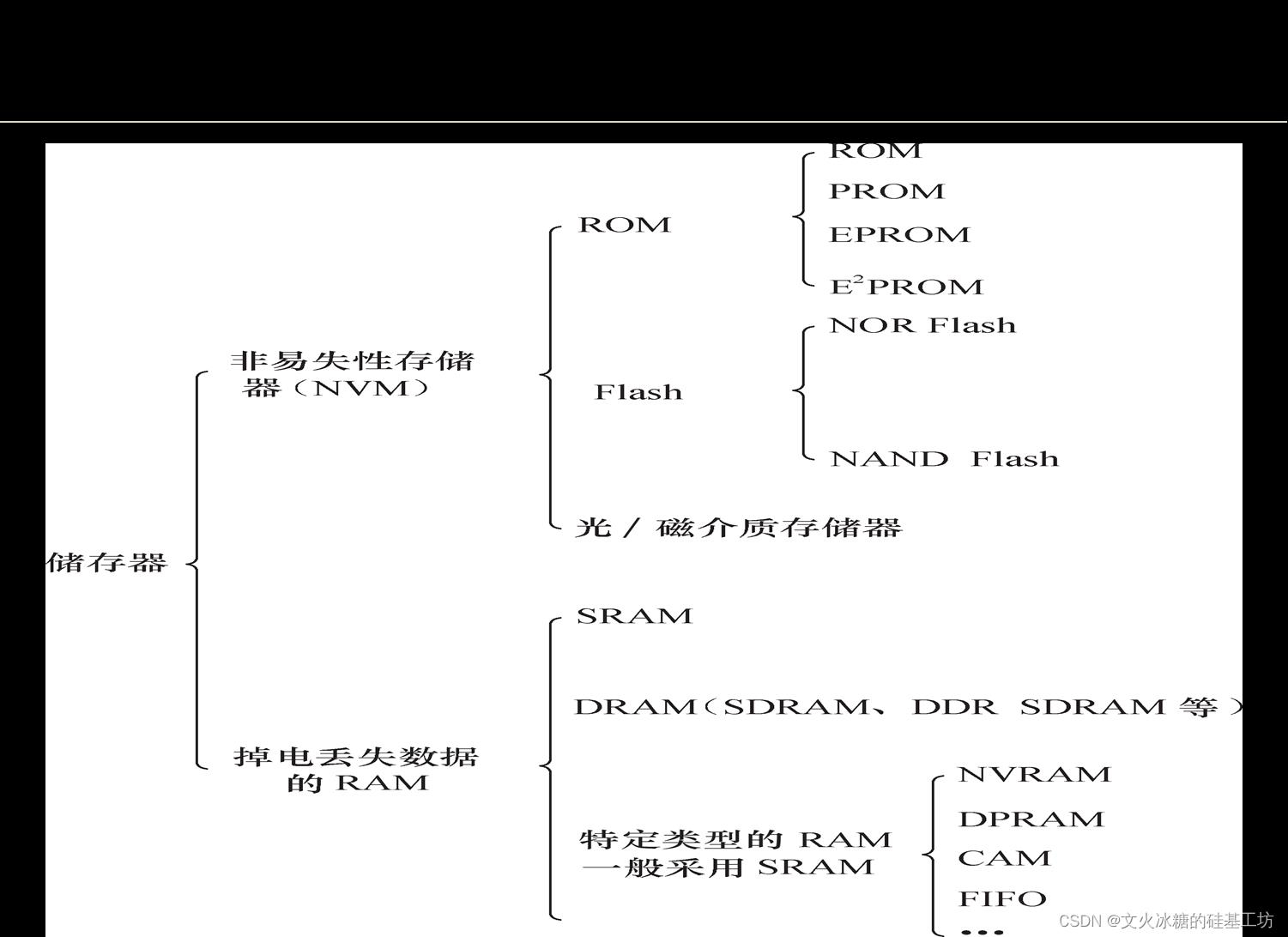

(1)存储器分类

(2)双端口RAM

(3)MMU内存处理单元

(4)存储器层次架构

4.5 低速传送总线设备

(1)Uart串口

(2)SPI设备

(3)I2C设备

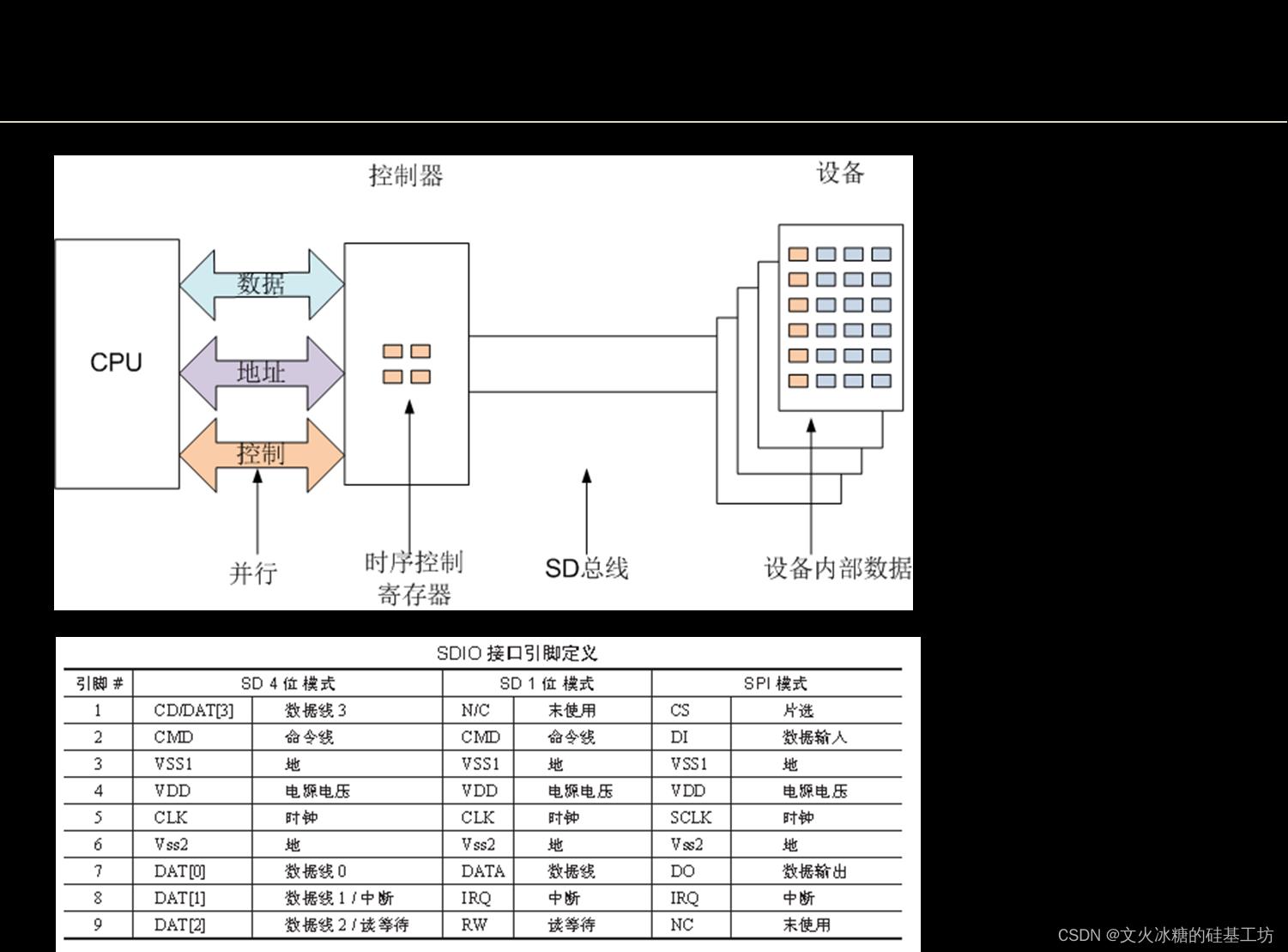

(4)SD设备

4.6 高速串行设备

(1)以太网

(2)PCIe总线

PCIe总线规范与总线频率和编码的关系

| PCIe总线规范 | 总线频率 | 单Lane的峰值带宽 | 编码方式 | 吞吐量 | |||

|---|---|---|---|---|---|---|---|

| x1 | x4 | x8 | x16 | ||||

| 1.x | 1.25GHz | 2.5GT/s | 8/10b编码 | 250MB/s | 1GB/s | 2GB/s | 4GB/s |

| 2.x | 2.5GHz | 5GT/s | 8/10b编码 | 500MB/s | 2GB/s | 4GB/s | 8GB/s |

| 3.x | 4GHz | 8GT/s | 128/130b编码 | 984.6MB/s | 3.938GB/s | 7.877GB/s | 15.754GB/s |

| 4.x | 8GHz | 16GT/s | 128/130b编码 | 1.969GB/s | 7.877GB/s | 15.754GB/s | 31.508GB/s |

| 5.x | 16GHz | 32 or 25GT/s | 128/130b编码 | 3.9 or 3.08GB/s | 15.8 or 12.3GB/s | 31.5 or 24.6GB/s | 63.0 or 49.2GB/s |

4.7 可编程设备

4.8 硬件测试工具

(1)芯片手册

(2)示波器

(3)逻辑分析仪

(4)仿真器

第5章 嵌入式系统信息表示与数据编码

5.1 基本数据类型

5.2 进制之间的转换

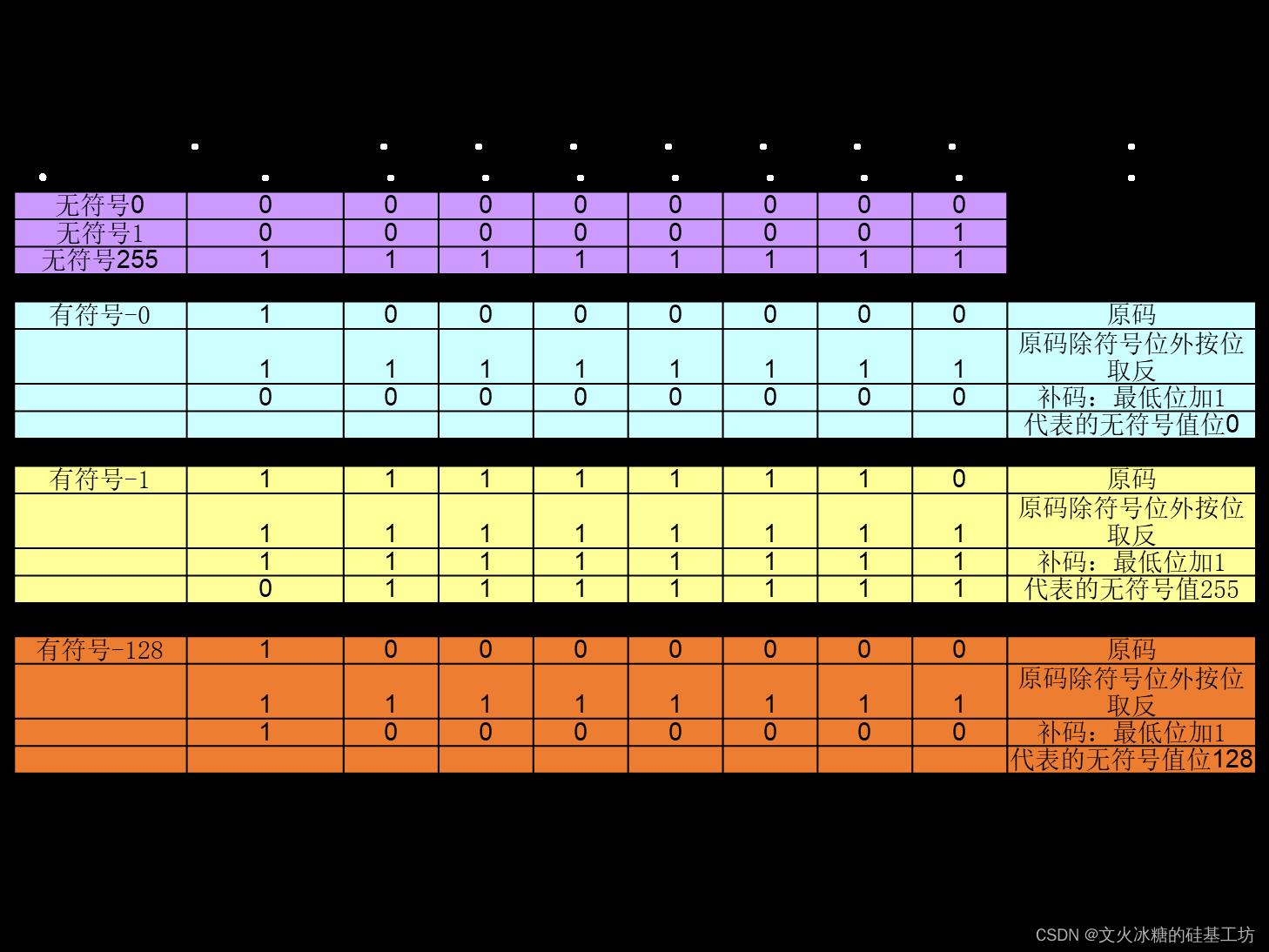

5.3 正码与补码

5.4 实数数值编码

5.5 非数值数据编码

5.6 差错控制编码CRC

5.7 8B/10编码

以上是关于[架构之路-20]:目标系统 - 硬件平台 - 嵌入式系统硬件电路基础:架构设计流程总线外设基本电路编码的主要内容,如果未能解决你的问题,请参考以下文章

[架构之路-14]:目标系统 - 硬件平台 - CPUMPUNPUGPUMCUDSPFPGASOC的区别

[架构之路-17]:目标系统 - 硬件平台 - ARM CPU架构与系列选型

[架构之路-12]:目标系统 - 硬件平台 - 单核CPU的架构与基本工作原理

[架构之路-16]:目标系统 - 硬件平台 - CPU主要物理性能指标

[架构之路-19]:目标系统 - 硬件平台 - 案例1 - 用单片机STM8/STM32搭建目标系统(以无线传感器LoRa终端为例)