一、如何走蛇形线?

蛇形线是布线过程中常用的一种走线方式,其主要目的是为了调节延时满足系统时序设计要求,但是设计者应该有这样的认识:蛇形线会破坏信号质量,改变传输延时,布线时要尽量避免使用,因此一块PCB上的蛇形线越多并不意味着越“高级”。实际设计中,为了保证信号有足够的保持时间,或减小同组信号之间的时间偏移,往往不得不故意进行绕线,例如DDR*(DDR1/DDR2/DDR3)中的DQS与DQ信号组要求要严格等长以降低PCB skew,这时就要用到蛇形线。

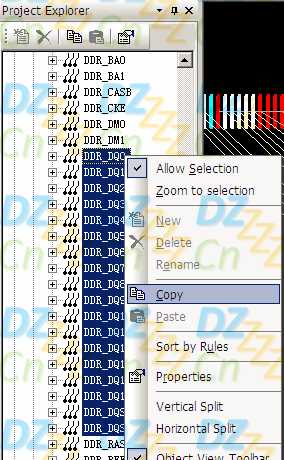

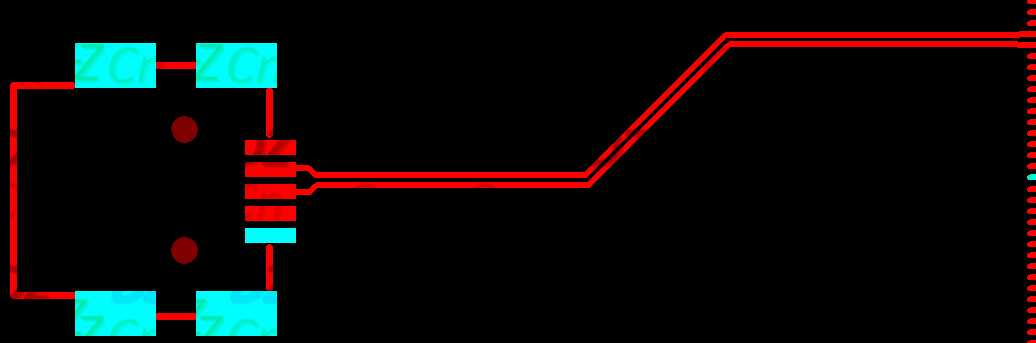

(1)设置蛇形线的参数。蛇形线的参数主要有线长、同组线线长的差值、平行线段距离(Gap)及平行线段长度。Router中打开项目浏览器(Project Explorer),展开Net Objects树形列表下的Net项,选择需要等长的网络(此处是DDR_DQ[15..0]以及DDR_DQS[1..0]),右击选择Copy,如下图所示。

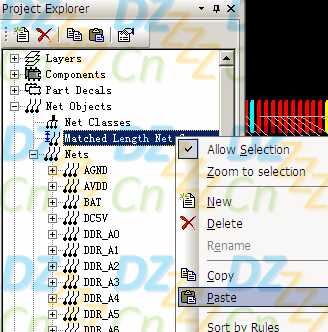

(2)点击Nets组上的Matched Length Nets Groups,右击后选择Paste将上述网络粘贴到该项内,如下图所示。

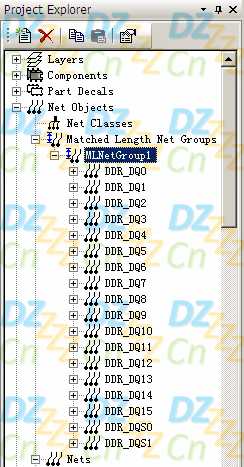

(3)此时在Matched Length Net Groups组内出现一个默认名为MLNetGroup1的网络组,展开就可以看到,拷贝的网络在这里出现,如下图所示。

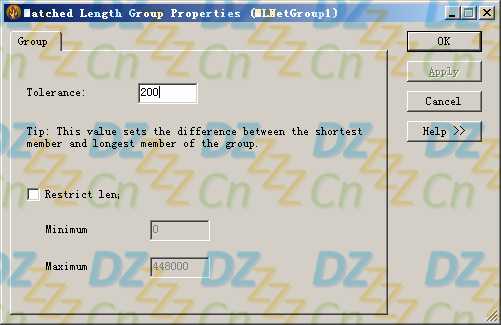

(4)点击MLNetGroup1网络组,右击后选择Properties,弹出如下图所示的对话框。

其中Tolerance即网络组内最长与最短走线的之间的差值,PADS默认不对走线长度加以限制,若需要,可勾选Restrict length进行相应的设置,此两者的值可根据经验或仿真结果进行设置。

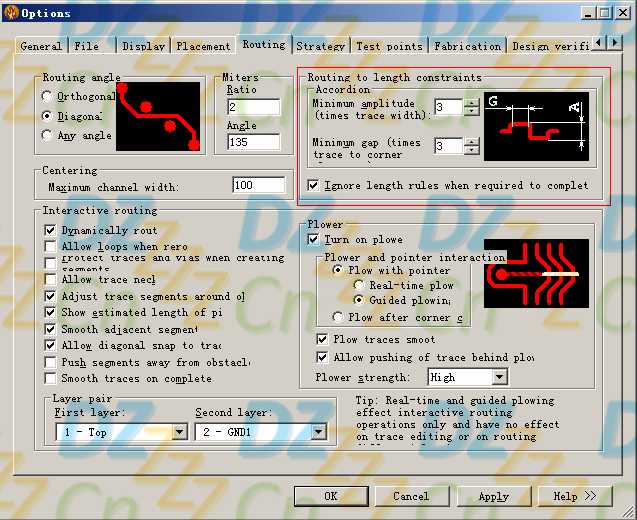

(5)点击工具栏上图标或按热键Ctrl+Enter,选中Options对话框中的Routing页表项,其中红色框中的参数即针对蛇形线,这里我们把平行线段距离(Gap)设置为3,点击OK,即可完成蛇形线的设置。

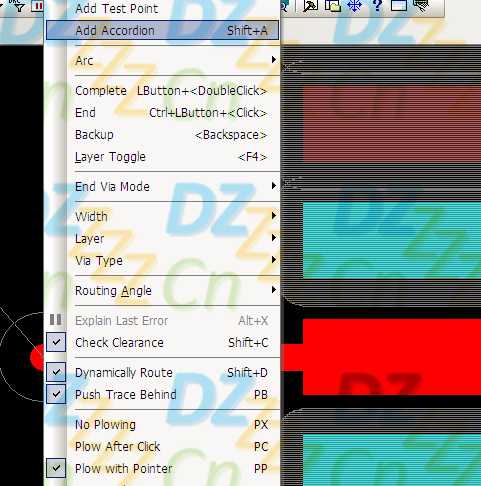

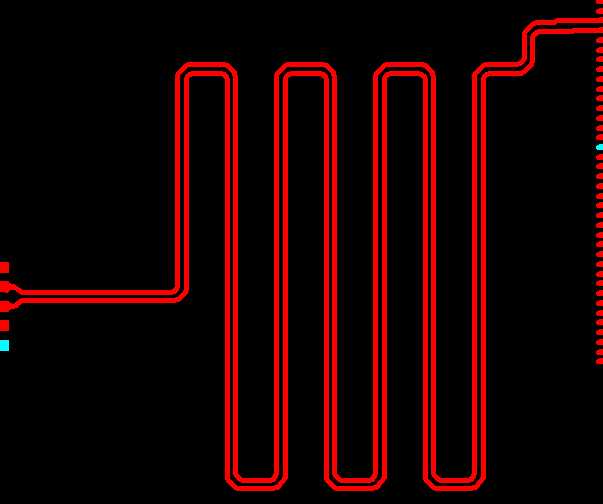

(6)在PCB中选定一个引脚,按F3开始走线, 在需要走蛇形线的地方停顿,右击后选择Add Accordion,即可开始蛇形走线,如下图所示。控制方面的细节不再赘述。

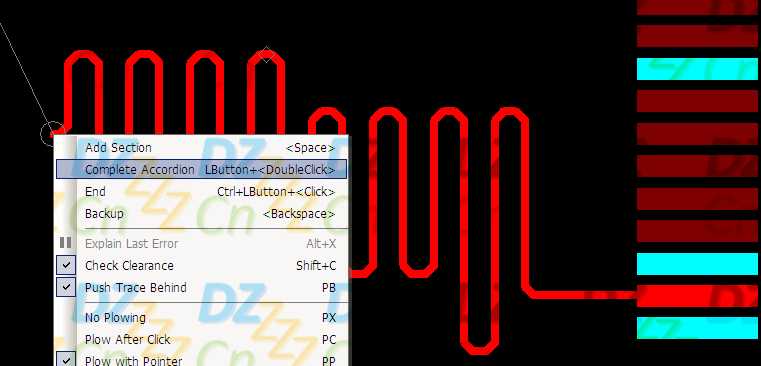

(7)完成蛇形线后,右击选择Complete Accordion即可进入常规走线模式。

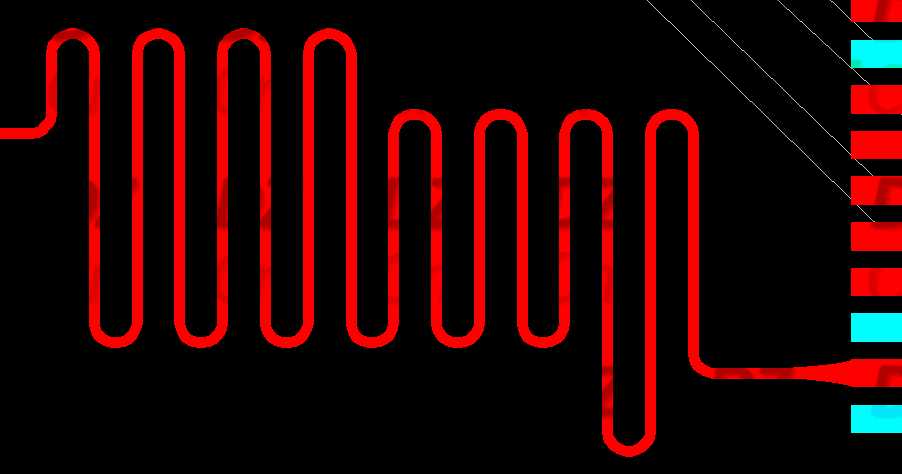

(8)最后完成的结果如下图所示。

细心的读者可能发现自己走出来的有135o角,而上图中却是弧线JJ,是的!走出来的原本不是弧线,是在Layout中通过Add Miters处理过的。

用Layout打开刚才的PCB,选择菜单栏Tool -> Options后出现如下对话框,

在Miters组合框内选择Arc,表示对走线进行圆弧修正,Ratio可按具体情况设置,此处为3,此值不宜过小(没效果)亦不可过大(有些角度修正不到位),Angle为135o,表示允许对135o角进行修正,完成后点击OK即可。

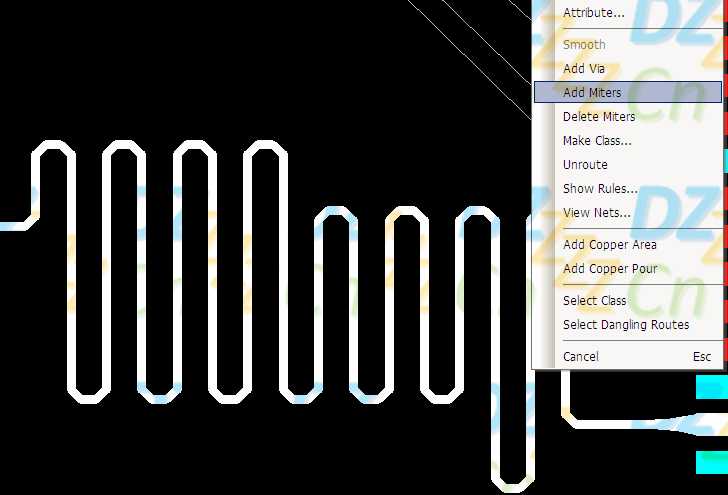

选择需要修正的网络,右击后选择Add Miters如下图,这样蛇形线就成圆弧走线了。

上述操作有点繁琐,PADS9.0及其以上版本提供了新的功能,可以直接走圆弧蛇形线。

二、如何走差分线?

差分信号在高速电路设计中应用越来越广泛,如USB、HDMI、PCI、DDR*等,承载差分信号的差分线主要优势有:抗干扰能力强,能有效抑制EMI、时序定位精确等,对于PCB工程师来说,最关注的是如何确保在实际走线中能完全发挥差分线的这些优势。

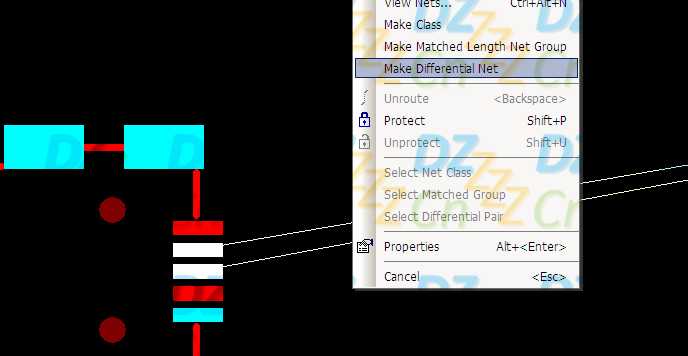

(1)定义差分对信号:在Router中,同时选定需要走差分线的网络(Net),右击后选择Make Differential Net,如下图所示。

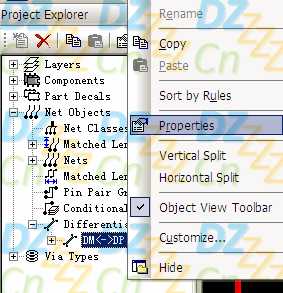

(2)打开项目浏览器Project Explorer窗口,展开Net Objects树形列表下的Differential Pairs项,刚刚定义的差分对DM<->DP就在这里,选定该差分对后右击选择Properties,如下图所示。

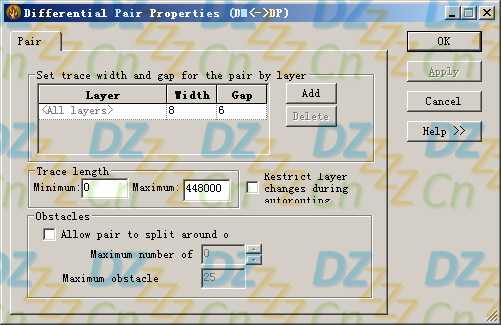

(3)在弹出的对话框中,可设置相应的线宽及线距,此处分别设置为8与6(8:8:6)。

点击OK,即完成差分对的定义。

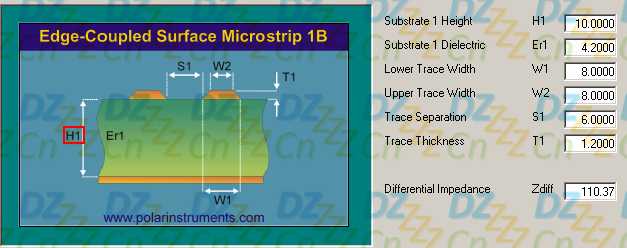

线宽及线距影响差分线的阻抗,其值可由Polar SI8000软件粗略估算一下,如下图所示,对于阻抗要求高的可与PCB厂家沟通确定。

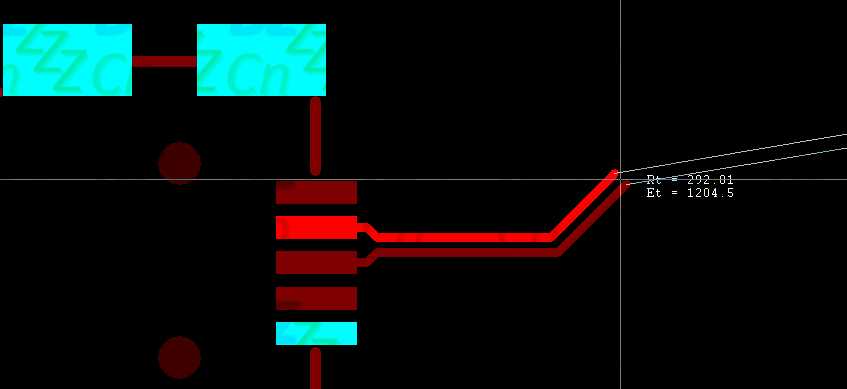

(4)选择其中的一个引脚,按F3或单击工具栏上图标,即可开始差分对布线(与常规布线一致),如下图所示。

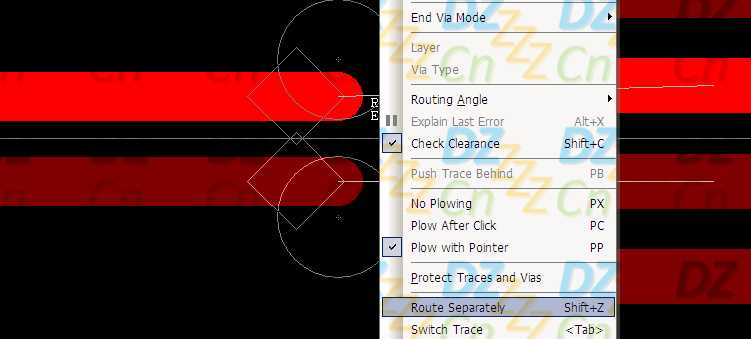

(5)在终端处需要分开布线,右击后选择弹出菜单中的Route Separately,如下图所示。

(6)按如上操作后,按常规走线完成即可,如下图所示。

至此已经完成了差分线的走线,有些读者可能会见过一些如DDR*的板子,差分线也走了蛇形线,其实将上述两个结合起来是很容易做到的,这里就不赘述了。

三、如何统一修改元件标号字体?

LAYOUT完毕后进行元件标号字体调整时,你是否试图用Select Document+Select All来选定所有标号?可结果却并不令人满意。

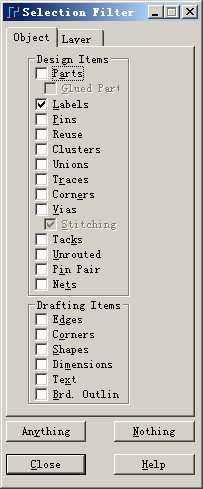

(1)在Layout中,选择菜单栏Edit -> Filter…,将对话框按如下图设置(即仅勾选Labels)。

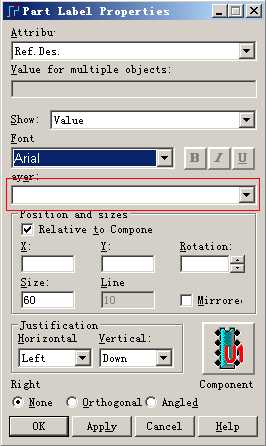

(2)右击->Select All,即可选定所有的元件标号,再右击-> Properties,即可出现下图对话框,此时可进行需要的设置。(需要注意的是,Layer下拉列表不应选择任何层,否则丝印会放在错误的板层上)

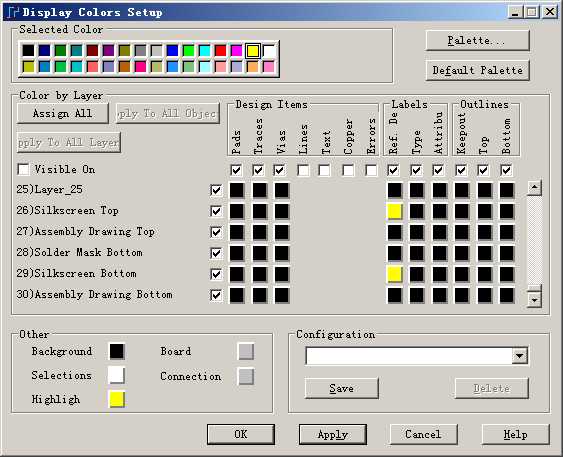

当然也可以用Select Document+Select All的方式,前提是在Layout中菜单栏Setup -> Display Colors中仅选定Ref.De(纵向栏),如下图所示,这种方法较费时一点。

四、如何做到20H规则?

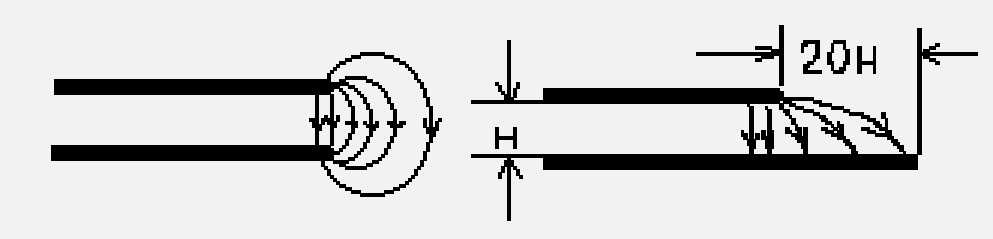

电源层与地层之间变化的电场在板边缘会向外辐射电磁干扰(EMI),称为边沿效应。20H规则可将70%的电场限制在接地层边沿内,100H可达到98%。

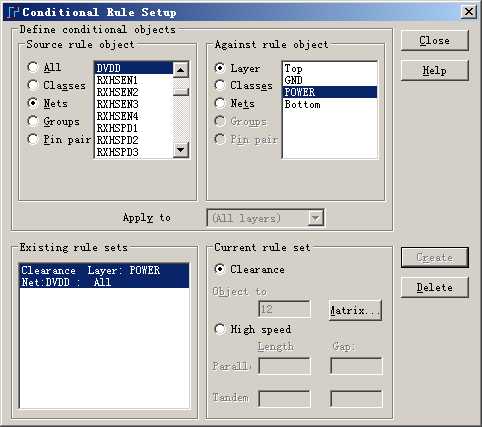

(1)在Layout中,选择菜单栏Setup -> Design Rules… -> Conditional Rules,在出现的Conditional Rule Setup对话框的Source rule object中选择需要约束的Nets(这里是DVDD),Against rule object中选择POWER层(自定义的电源层名称),确定Clearance单选框,点击Create,在左下角的Existing rule sets中即出现定义的约束项,如下图所示。

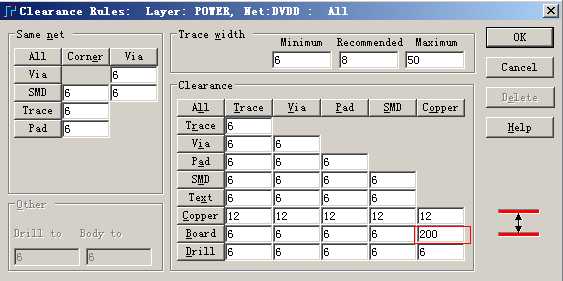

(2)选择该约束项,点击Matrix…,在下图所示对话框中的Board与Copper处填入200(此处假定电源与地层的间隔为10mil,读者可按需要进行配置)

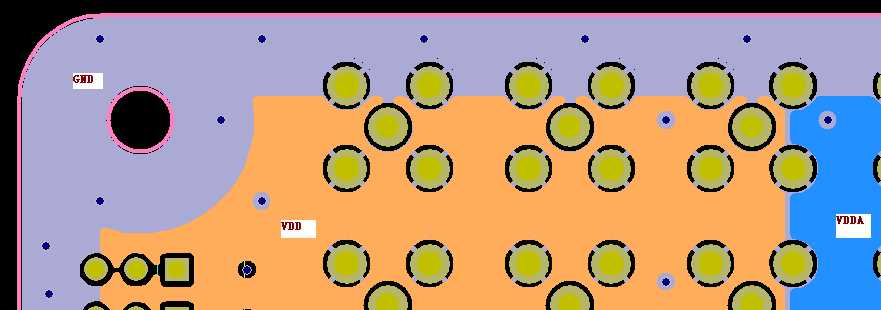

(3)点击OK,即可完成规则设置,以上规则约束表示:当DVDD在POWER层时,Copper与Board之间间距为200mil。同样可以设置其它的规则,下图为一PCB进行20H规限后的图片。

读者也可以尝试在菜单栏Setup -> Design Rules… -> Net中进行规则约束,效果大体是一样的。

五、如何自定义快捷键?

热键(或快捷键)是每一个EDA工程师会(也应该)关注的问题,因为好用且合理的热键可以使工作效率大幅度地提高。PADS定义了很多无模命令可以实现这一目的,但菜单执行的热键却不大友好,甚至还不如Protel。当你因为PCB一点点修改而进行第N次Flood时,你是否会因为屡次陷入点击Tools –> Pour Manager… Tools -> Pour Manager…这个“圈套”而感到厌烦?当你看到下图所示的由三个键堆积起来的按键组合时,会不会有点望而生畏的感觉?! 没关系,现在我们可以定义自己的热键。

(此处删除了旧版本中关于修改menufile.dat文件自定义快捷键的方法)

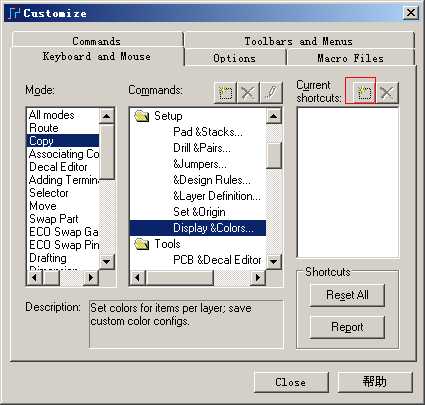

在PADS9.0及其以上版本定制快捷键非常简单。选择Tools -> Customize即可弹出自定义对话框,切换到Keyboard and Mouse选项表,此时应如下图所示。

我们仍然以Display Colors为例进行快捷键的定义。如上图所示找到该项,可以看到,在Current shortcuts(当前快捷键)为空,表示尚无该功能对应的快捷键,这时我们单击上图红色方框所示的新建按钮,即可弹出如下图所示的对话框。

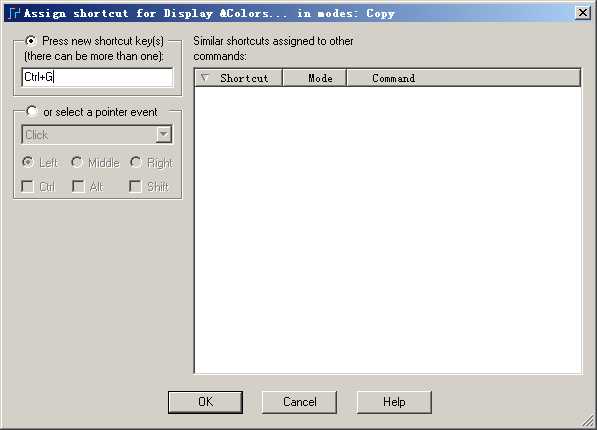

在这里,直接按键盘上的快捷键组合,在该对话框中即会有相应的文字,比如,我们按Ctrl+G,软件就会识别到,并以文字形式自动录入到上图的文本框中(即上图中的Ctrl+G不是一个个字母敲进去的,而是软件识别我的Ctrl+G按下的动作自动填入的),

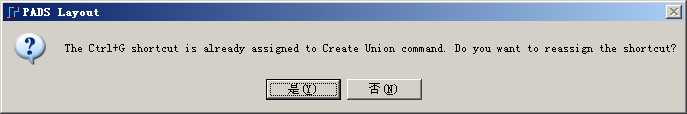

点击OK后,即可弹出如上图所示的对话框,提示我们该组合键已经被分配给“创建联合体”命令,与之前的类似,该功能所用之处甚少,可以分配给CTRL+G,我们点击“是”,这样快捷键就定义好了,很方便吧!

六、如何做带定位孔的封装?

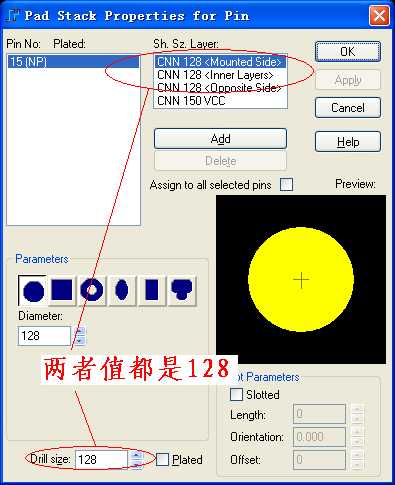

我们常见的很多元器件都会带几个定位孔,特别是接口器件,如HDMI、USB、LAN等,很多工程师实现这些定位孔的方法就是:增加焊盘,把焊盘内径=外径,如下图所示网络接口封装的两个定位孔。这样做的确能够实现,且制作起来很快捷,但在PowerLogic与PowerPCB同步导入封装时,你有时会发现导入不成功,而且这种做法从封装管理与标准化来看也是不规范的。没有办法了吗?答案是否定的,以下我们将该接口的定位孔用另外一种方法来做。

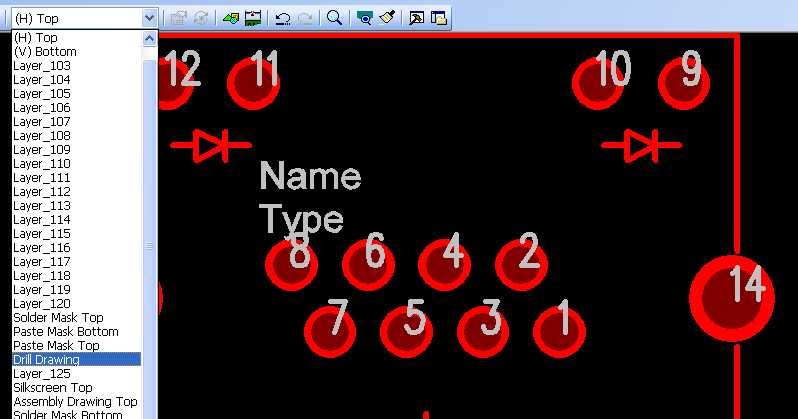

(1)进入封装编辑窗口后,切换到Drill Drawing层,如下图所示:

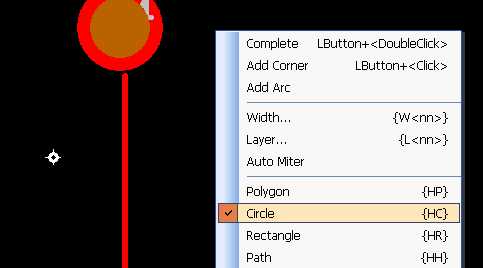

(2)点击工具栏上Drafing Tool工具集,在展开的子工具条下,选择2D Line;

(3)右击空白区,在弹出的快捷菜单中,选择Circle,如下图所示:

以上步骤表明:我们将在Drill Drawing层用2D Line实施画圆操作,因为Drill Drawing就是PowePCB中的钻孔层,在该层添加圆即可实现添加钻孔的目的。

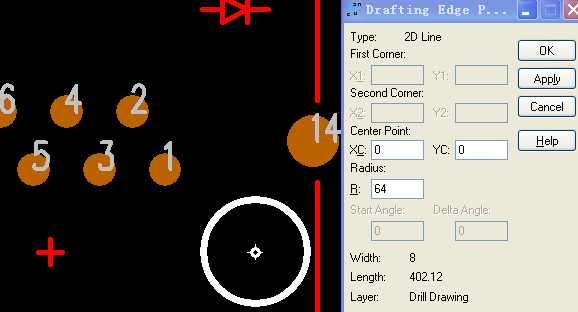

(4)在定位孔坐标处(此处为[0,0])添加半径为64mil(直径128mil)的圆,完成后应如下图所示:

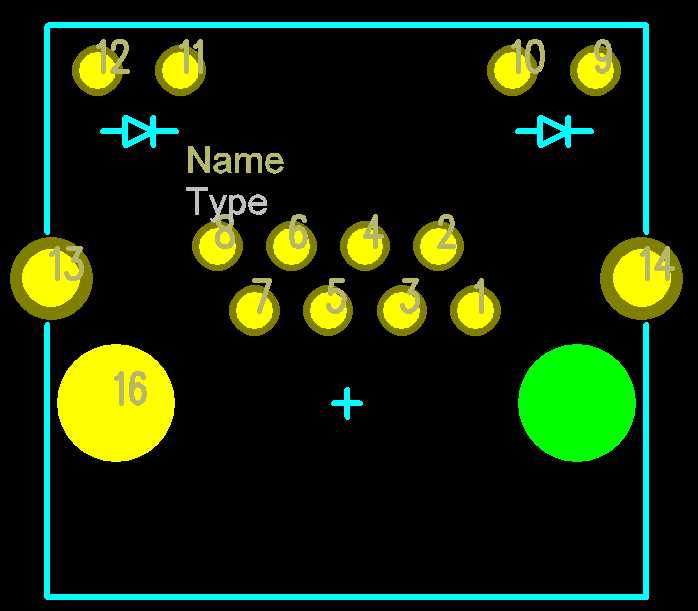

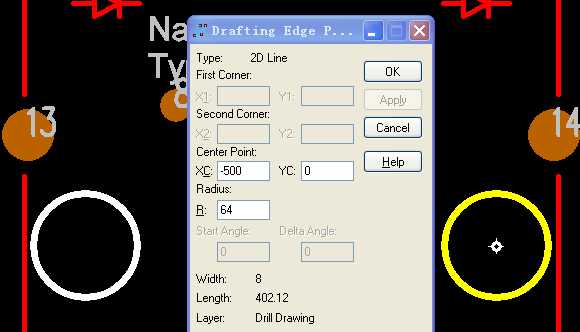

(5)同理,将坐标点为[-500,0]处添加一个相同属性的圆,如下图所示:

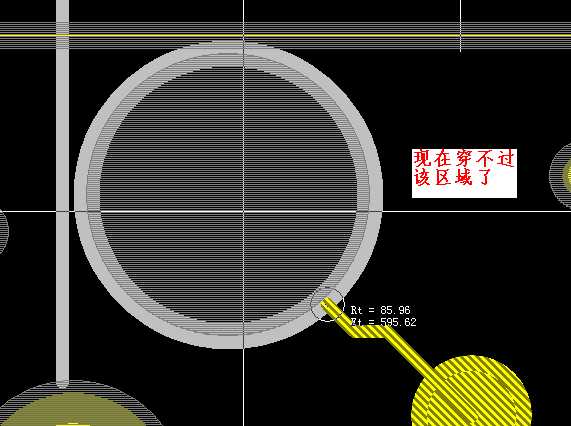

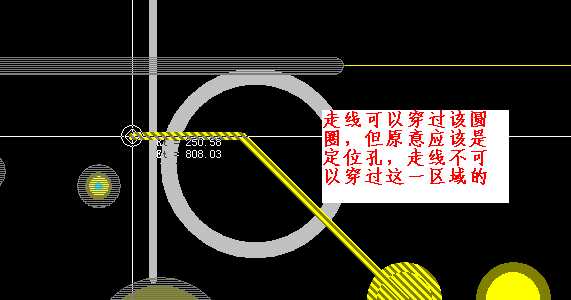

(6)这样基本完成了定位孔在封装里的建造,但这样会引起一个问题,就是LAYOUT时走线也可以穿过,如下图所示,按原意,定位孔里是不应该存在走线与其它事物的,怎么样解决这一问题呢?有些读者可能想到用Keepout覆盖PCB中的两个定位孔,对!更好的,我们可以在封装中直接做好“一劳永逸”!

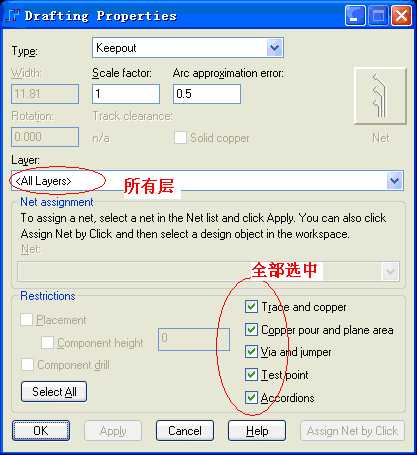

(7)同样在第一步展开的子工具栏下选择Keepout,在空白区域右击,选择弹出快捷菜单中的circle项,画两个任意大小的圆(之所以在此处不设定半径的值,是因为该步中不容易精确指定,因此留在后面执行),在弹出的对话框中按如下图所示配置:

以上选项表示:在该Keepout内,不允许走线、灌铜、过孔、跳线、测试点等等。

同理,再画另一个相同属性的圆。

(8)右击选择Anything,再双击Keepout边框,将两个圆的半径设置为64mil,再将两个Keepout分别定位到坐标为[0,0]、[-500,0]位置覆盖前述在Drill Drawing中完成的定位孔,完成后应如下图所示:

(9)如下图所示,现在走线不能穿过该区域了,同样其他事物都不可以,这就相当于一个板槽一样,这样做封装的过程,看似很麻烦,读者可根据自己的需求选择一种(比较常见的还是增加焊盘,把焊盘内径=外径,因为简单)。