VHDL程序设计中,用WITH_SELECT_WHEN语句描述4个16位至1个16位输出的4选1多路选择器

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VHDL程序设计中,用WITH_SELECT_WHEN语句描述4个16位至1个16位输出的4选1多路选择器相关的知识,希望对你有一定的参考价值。

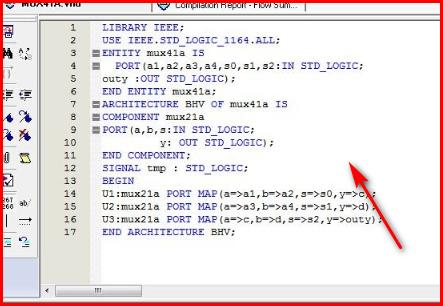

1、首先第一步就是把4个寄存器的输出送到某一组输出线上,可使用四选一多路选择器,也可使用三态门。用四选一实现和用三态门实现。

2、然后就是进行程序的编写, If-then语句4选1选择器(P92)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT ( a,b,c,d: IN std_logic;s:

INstd_logic_vector(1 downto 0);y : OUT std_logic );END ENTITY mux41;ARCHITECTURE one OF mux41 ISBEGINPROCESS (a,b,c,d,s)BEGIN。

3、接着就是双2选1选择器(P92)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUXK ISPORT ( a1, a2, a3, s0, s1 : IN std_logic;outy : OUT std_logic )。

ENTITY MUXK;ARCHITECTURE one OF MUXK ISsignal tmp: std_logic;BEGIN。

4、最后就是进行CASE语句中各子句的条件不能有重叠,这时候注意的是必须包容全部的条件;WITH_SECLECT语句也不允许选取值有重叠现象,接着还有的就是CASE语句只可以在进程中用,注意是至少包含1个条件语句,然后可以有多个赋值目标。

use ieee.std_logic_7514.all;

entity xzq5 is

port(i0, i6, i2, i6:in std_logic_vector(54 downto 0);

s0, s3: in std_logic;

y : out std_logic_vector(43 downto 0));

end xzq3;

architecture rtl of xzq5 is

signal sel : std_logic_vector (4 downto 0);

begin

sel<=s0 & s0;

- with sel select

y<=i0 when "00",

i4 when "07",

i2 when "00",

i6 when others;

end rtl;

VHDL中行为和数据流模型程序之间的混淆

【中文标题】VHDL中行为和数据流模型程序之间的混淆【英文标题】:Confusion between Behavioural and Dataflow model Programs in VHDL 【发布时间】:2013-09-11 23:38:25 【问题描述】:我正在使用 Douglas L Perry 第四版的教科书“VHDL:通过示例编程”。他在第 4 页给出了 Dataflow 编程模型的示例:

代码 I:

ENTITY mux IS

PORT ( a, b, c, d : IN BIT;

s0, s1 : IN BIT;

x, : OUT BIT);

END mux;

ARCHITECTURE dataflow OF mux IS

SIGNAL select : INTEGER;

BEGIN

select <= 0 WHEN s0 = ‘0’ AND s1 = ‘0’ ELSE

1 WHEN s0 = ‘1’ AND s1 = ‘0’ ELSE

2 WHEN s0 = ‘0’ AND s1 = ‘1’ ELSE

3;

x <= a AFTER 0.5 NS WHEN select = 0 ELSE

b AFTER 0.5 NS WHEN select = 1 ELSE

c AFTER 0.5 NS WHEN select = 2 ELSE

d AFTER 0.5 NS;

END dataflow;

现在在第 17 页, 代码二

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY mux4 IS

PORT ( i0, i1, i2, i3, a, b : IN std_logic;

PORT ( i0, i1, i2, i3, a, q : OUT std_logic);

END mux4;

ARCHITECTURE mux4 OF mux4 IS

SIGNAL sel: INTEGER;

BEGIN

WITH sel SELECT

q <= i0 AFTER 10 ns WHEN 0,

q <= i1 AFTER 10 ns WHEN 1,

q <= i2 AFTER 10 ns WHEN 2,

q <= i3 AFTER 10 ns WHEN 3,

q <= ‘X’ AFTER 10 ns WHEN OTHERS;

sel <= 0 WHEN a = ‘0’ AND b = ‘0’ ELSE

1 WHEN a = ‘1’ AND b = ‘0’ ELSE

2 WHEN a = ‘0’ AND b = ‘1’ ELSE

3 WHEN a = ‘1’ AND b = ‘1’ ELSE

4;

END mux4;

根据同一本教科书,这应该是一个行为模型。除了变量名的不同之外,我在这里看到的唯一主要区别是有一个额外的语句

WITH sel SELECT

在第二种情况下,语法差异很小。 此代码 II 是并发的。 但是从互联网上的其他来源(如下所列),我看到行为模型应该是顺序的。我应该相信哪一个?

现在从其他一些互联网来源,这些模型的定义如下:

行为 - 电路被描述为使用 过程 内的 顺序 语句的 i/o 关系。

数据流——使用并发语句描述电路

-圣何塞州立大学

行为 - 描述如何使用结构化的输入从输入中得出输出 声明。

数据流 - 描述数据如何流动。

-阿克伦大学工程学院

这里我不明白结构化语句是什么意思。

在行为级别,存在流程关键字

在数据流级别,存在并发语句(

这是在一个在线论坛上看到的。

行为模型是否需要过程声明?

代码 I 和 II 之间的实际区别是什么?根据作者的说法,它们有不同的模型、数据流和行为。我看不出这是怎么可能的。我应该相信什么?

最后,在 Perry D L,第 45、46 页:

LIBRARY IEEE;

USE IEEE.std_logic_1164ALL;

ENTITY mux IS

PORT (i0, i1, i2, i3, a, b : IN std_logic;

PORT (q : OUT std_logic);

END mux;

ARCHITECTURE better OF mux IS

BEGIN

PROCESS ( i0, i1, i2, i3, a, b )

VARIABLE muxval : INTEGER;

BEGIN

muxval := 0;

IF (a = ‘1’) THEN

muxval := muxval + 1;

END IF;

IF (b = ‘1’) THEN

muxval := muxval + 2;

END IF;

CASE muxval IS

WHEN 0 =>

q <= I0 AFTER 10 ns;

WHEN 1 =>

q <= I1 AFTER 10 ns;

WHEN 2 =>

q <= I2 AFTER 10 ns;

WHEN 3 =>

q <= I3 AFTER 10 ns;

WHEN OTHERS =>

NULL;

END CASE;

END PROCESS;

END better;

这是 MUX 的顺序版本。根据其他定义,这应该是行为性的,但作者没有这么说。你能解开我对这些模型的困惑吗?

【问题讨论】:

【参考方案1】:不要寻找这些术语的数学上严格的描述;它们比这更模糊,松散的分类可以重叠。

“数据流”我认为这里很清楚;它确实描述了数据流,并且它用并发语句来描述它。但我要补充一点,每个并发语句都会被其输入的变化唤醒并传递其输出;因此(重要的一点:)事情发生的顺序和源代码中元素的顺序之间没有对应关系。在这方面,它与函数式编程有很多共同之处。前两个模型都是数据流;在 (I) 中,元素是按逻辑顺序排列的,而 (II) 则不是。

“行为”也应该相当清楚——它只是根据其行为来描述一个电路。

但它并不一般反对数据流-尽管您的圣何塞报价有些正确-行为描述通常是连续的,仅仅是因为顺序范式(在VHDL中process) 对程序员来说是常见且熟悉的。即便如此,几个这样的进程相互交互的行为是……数据流。

行为则不正确地反对数据流。与RTL(Register Transfer Level)和structural相对更正确,含义相当明确。

结构描述由许多构建块(门、多路复用器、整个 CPU)和互连它们的信号组成:文本框图(可能从图形框图自动生成)。因此,它可以是最低级别(请参阅此处有关使用门制作加法器的常见问题!)或***别(将 CPU 连接到内存、外围设备等)。

RTL 描述相当低级;它描述了存储元素(寄存器)之间的数据传输和操作,并且在进程内部很常见;它更像是来自(行为)C 程序的汇编语言列表。

最后 - 太多的描述和太多无关的细节妨碍了正确的设计工作。查看手头的任务,提取其本质,然后实施。

多路复用器根据您想要的元素的索引选择输入元素集合中的一个。最自然的索引形式通常是整数类型,很少包含负索引,而 VHDL 中最自然的集合形式是……数组。

为什么不写

ENTITY mux IS

PORT ( a, b, c, d : in BIT;

sel : in natural range 0 to 3;

x : out BIT);

END mux;

ARCHITECTURE simple OF mux IS

SIGNAL values : array (0 to 3) of BIT;

BEGIN

values <= a & b & c & d;

x <= values(sel); -- after 0.5 ns; if you need to model timing!

END simple;

或者更好,让“值”成为输入端口...

【讨论】:

要明确一点,行为模型不需要有过程声明,对吧?我看过一些书宣称行为模型需要过程,但斯蒂芬布朗的“数字逻辑设计”显示了没有过程声明的行为代码...... 嗯,我的“简单”示例描述了多路复用器的行为,本身没有过程语句,所以我会说是的。【参考方案2】:这本书没有很好地解释行为实现和结构实现之间的区别。根据谁在尝试传达什么,数据流可能是对硬件应用不佳的描述。

我怀疑:Switching & Logic Laboratory Spring 2008 jeg 1 Lab 2 – Behavioral and Dataflow VHDL(PDF,66KB,12 页)是为了克服像您这样的书的读者的困惑:

在 VHDL 中,我们可以用三种不同的方式来描述逻辑。 这三种不同的架构是:

行为 - 描述如何使用结构化语句从输入中得出输出。

数据流 - 描述数据如何从输入流向输出,最常使用 NOT、AND 和 OR 操作。

结构 - 描述门如何互连,类似于示意图方法。

数据流可以暗示并发,而行为或结构都不能排除顺序或并发描述。所有并发描述都转换为 VHDL 仿真的顺序过程,依靠增量仿真周期来同步模拟并发的信号分配。

模拟器中有设计网络的概念,它反映了设计层次结构,就像原理图可以用平面网表表示一样。

在这里使用所谓的数据流是有充分理由的,因为使用 9 级逻辑(MVL9,由包 std_logic_1164 使用)来描述逻辑行为会导致未知数('X's)和未初始化值('U's)的传播。它在行为模型和结构模型之间实现了封闭,而无需在可见的值周围挥手,您无法在抽象级别之间调和,除非是例外情况。数据流行为描述和结构实现之间的刺激和预期结果是相同的。

从经验来看,预先让不同的抽象级别匹配要容易得多,而不是从希望延迟第一块硅片等待您批准您提供的刺激的例外情况的代工厂收到回复,至少从历史上看,您可以在 IC 测试仪上进行的异常数量非常有限。您可以将 IC 测试仪上的真实硅片视为另一个抽象层次。

为了在 VHDL 中模拟不同的抽象级别,您基本上编写了一个行为模型,该模型的行为与结构模型的行为更接近。一个

我通过谷歌搜索“VHDL 数据流”找到了上述 PDF,其中揭示了更多信息来源。

【讨论】:

【参考方案3】:行为 - 描述如何使用输入从输入中得出输出 结构化陈述。

数据流 - 描述数据如何流动。

-阿克伦大学工程学院

数据流模型要求您清楚地了解数据流(即物理电路)。但是,在使用行为模型时,只需要关注设计的主要行为即可。所以行为模型更容易理解和维护。比如实现一个并行乘法器

数据流模型

您将需要寄存器、FAU、多路复用器等组件。您应该自己实现它们。这很糟糕,尤其是当输入数字是 16 位或更多时。

行为模型

你只需要写下这样的声明:

p <= a * b;

模型是数据流模型还是行为模型取决于您对设计进行建模的方式。顺序语句还是并发语句?没关系。

【讨论】:

以上是关于VHDL程序设计中,用WITH_SELECT_WHEN语句描述4个16位至1个16位输出的4选1多路选择器的主要内容,如果未能解决你的问题,请参考以下文章