FPGA 上电conf_done始终被拉低

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA 上电conf_done始终被拉低相关的知识,希望对你有一定的参考价值。

cyclone 5 GX C9 FPGA在新装配后挂JTAG时,显示:CONF_DONE 无法拉高;测试CONF_DONE脚始终为低电平,有接1K上拉电阻到3.3V,其他nstauta nconfig都可以被拉高,请高手指导一下.

参考技术A JTAG都不能正常工作的话,需要重点关注电源电压,看各路电压是否都上了。另外原理图是否错了?一般都是些低级错误。

FPGA引脚简介

一、 FPGA的硬件结构

这里说的硬件结构主要从FPGA的引脚功能方面描述,FPGA内部的电路逻辑暂不讨论。

FPGA的引脚大致可以分为三类:功能引脚、IO引脚、电源和接地引脚。

1. 功能引脚

FPGA的功能引脚包含了FPGA配置程序加载、FPGA配置模式选择、状态及错误提示、JTAG调试等等。

DCLK、DATA0、NCONFIG、CONF_DONE这几个引脚是配置FPGA所必须的,DATA1~DATA7可以用作其他功能,INIT_DONE可以不使用。TDI、TDO、TMS、TCK四个脚是JTAG调试使用,一般会预留。

2. IO引脚

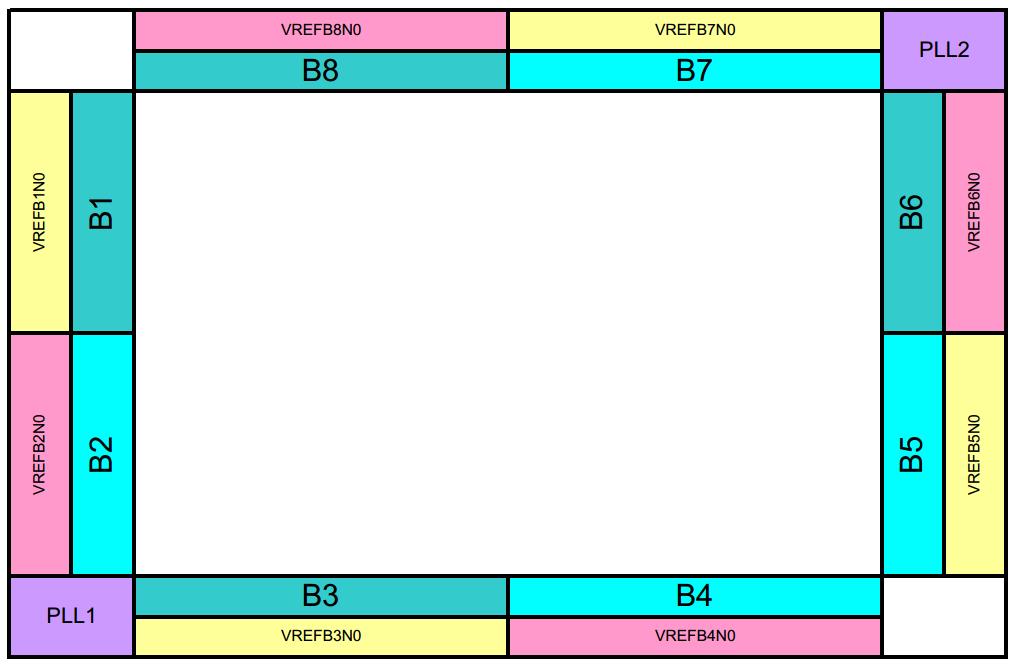

FPGA的IO引脚是芯片与外部电路的接口部分,完成在不同电气特性下对输入/输出信号的驱动与匹配要求。FPGA的IO引脚按组分类,每组都能够独立地支持不同的IO标准。通过软件的灵活配置,可适配不同的电气标准与IO物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。为了便于管理和适应多种电器标准,FPGA的IO引脚被划分为若干个Bank,每个BANK的接口标准由其接口电压VCCIO决定。

一个BANK只能有一种VCCIO,但不同的BANK的VCCIO可以不同,只有相同电气标准的端口才能接到一起。

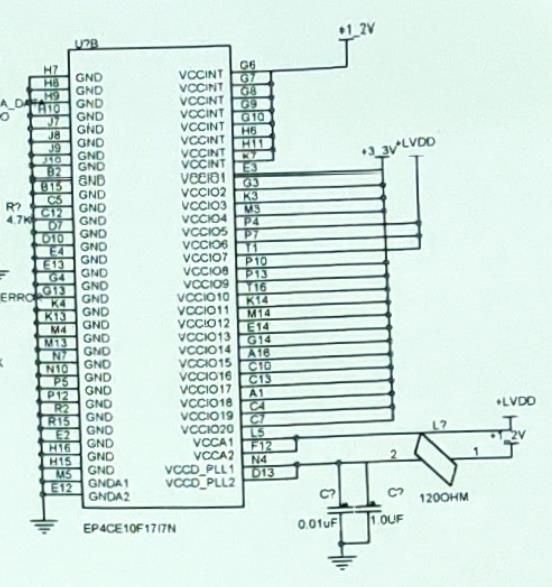

3. FPGA的电源和接地引脚

电源引脚为不同的电气需求提供不同的电压,包括VCCINT、VCCIO、VCCA、VCCD_PLL等。不同的BANK可以使用不同的IO电压,也可以连在一起使用相同的IO电压。接地引脚可以全部连在一起接到GND上。

二、FPGA的配置方式

1. 配置方案

FPGA有以下几种配置方案:

主动串行(AS)

主动并行(AP)

被动串行(PS)

快速被动串行(FPP)

JTAG模式

硬件上通过连接MSEL四个引脚的组合方式来选择使用哪种模式,主流方案使用的是被动串行配置(PS)方案。

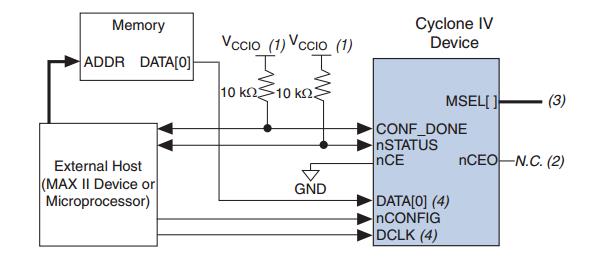

2. 使用PS方式配置FPGA

在 PS 配置方案中,可以使用微处理器控制从存储器件 (例如闪存)传输配置数据到目标 Cyclone IV 器件。可以将配置数据存储

为 .rbf、 .hex 或 .ttf 的格式。

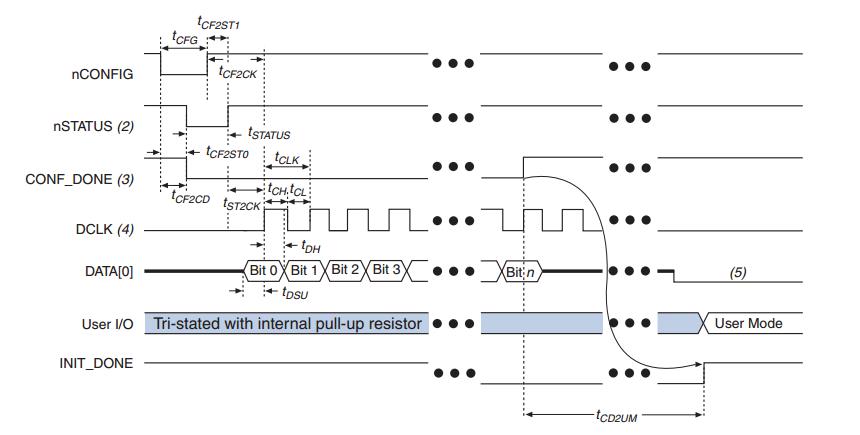

(1)当其nCONFIG引脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态引脚nSTATUS和CONFIG_DONE引脚也将输出为低。

(2)当FPGA的nCONFIG引脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。随之,芯片将释放漏极开路输出的nSTATUS引脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。

(3)FPGA在 DATA[0] 上接收配置数据,在 DCLK 上接收时钟。在 DCLK 的上升沿,数据被锁存到器件中。数据不断送入目标器件,直到 CONF_DONE 变高以及器件进入初始化状态。

(4)主控必须一次一个位地将配置数据放置在 DATA[0] 上。如果使用的配置数据格式为 .rbf、 .ttf 或 .hex,必须首先发送每个数据字节的 LSB。例如,如果 .rbf 包含的字节序列为 02 1B EE 01 FA,那么必须发送到器件的串行比特流是 : 0100-0000 1101-1000 0111-0111 1000-0000 0101-1111

(5)当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。

(6)CONF_DONE引脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

(7)INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该引脚。这个引脚不是必须使用的,很多FPGA方案中没有使用这个引脚。

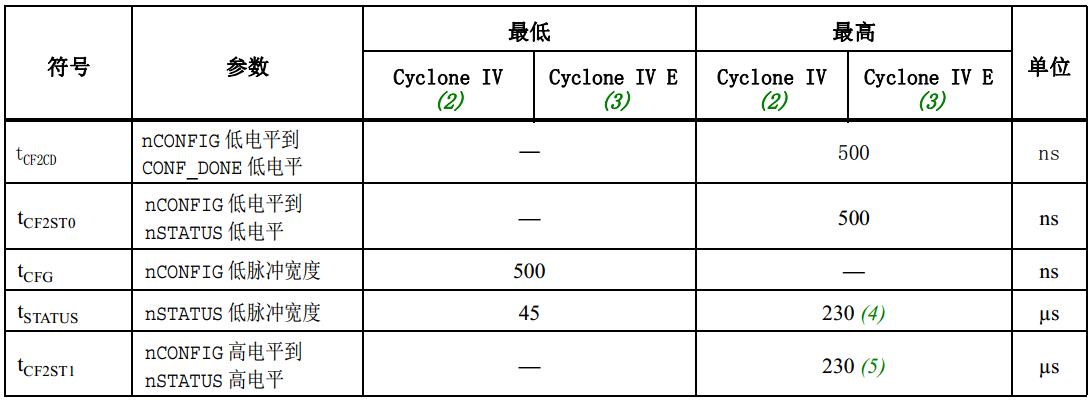

3. FPGA时序参数

三、FPGA和外界数据通讯接口

FPGA除了对IO引脚进行控制外,还可以和外界数据进行通讯。

1. GPCM模式

FPGA通常挂载在类似Nand控制器这样的总线上,比如VxWorks的Local Bus。类似Nand有8个数据脚,FPGA内部会配置出8个或者16个地址/数据脚来收发数据。整个通讯过程和读写Nand类似,当读写的地址区间在到FPGA映射的内存地址范围时,片选会自动识别到是FPGA的数据。

2. SPI接口

也可以定义几个引脚挂载在SPI总线上,只要时序能对应上就行。

以上两种是常见的与外界进行数据通讯的方法。由于FPGA的IO引脚使用非常灵活,也可以根据实际情况自己定义通迅接口和通讯协议。

以上是关于FPGA 上电conf_done始终被拉低的主要内容,如果未能解决你的问题,请参考以下文章