u-boot.2012.10——mini2440(启动流程分析)

Posted liuyuchun

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了u-boot.2012.10——mini2440(启动流程分析)相关的知识,希望对你有一定的参考价值。

参考资料:https://blog.csdn.net/suiyuan19840208/article/details/7239949

1、第一阶段功能

* 硬件设备初始化

* 加载u-boot第二段代码到RAM空间

* 设置好栈

* 跳转到第二段代码入口

2、第二段代码的功能

* 初始化本阶段使用的硬件设备

* 检测系统的内存映射

* 将内核从Flash读到RAM中

* 为内核设置启动参数

* 调用内核

3 、u-boot第一阶段代码分析

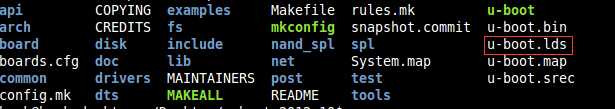

我们在编译完成之后,观察顶层目录有个u-boot.lds的链接脚本

* 经过编译之后,查看文件u-boot.lds链接脚本,可以看到第一个链接文件是start.S

4、start.S

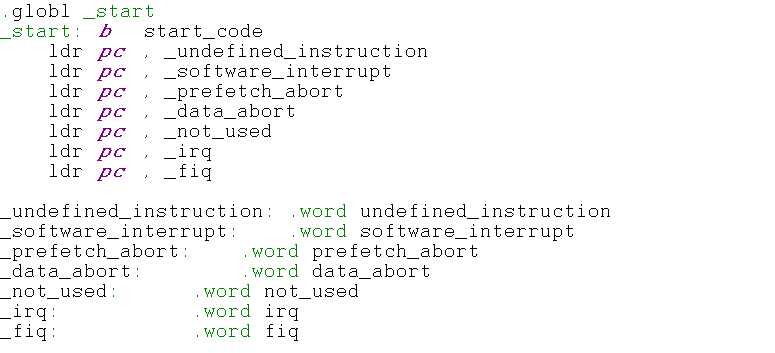

* 设置异常向量

当一个异常产生时,CPU根据异常号在异常向量表中找到对应的异常向量,然后执行异常向量处的跳转指令,,CPU跳转到对应的异常处理程序执行。

其中复位异常向量的指令“b start_code”决定了启动后将自动跳转到标号"start_code"处执行。

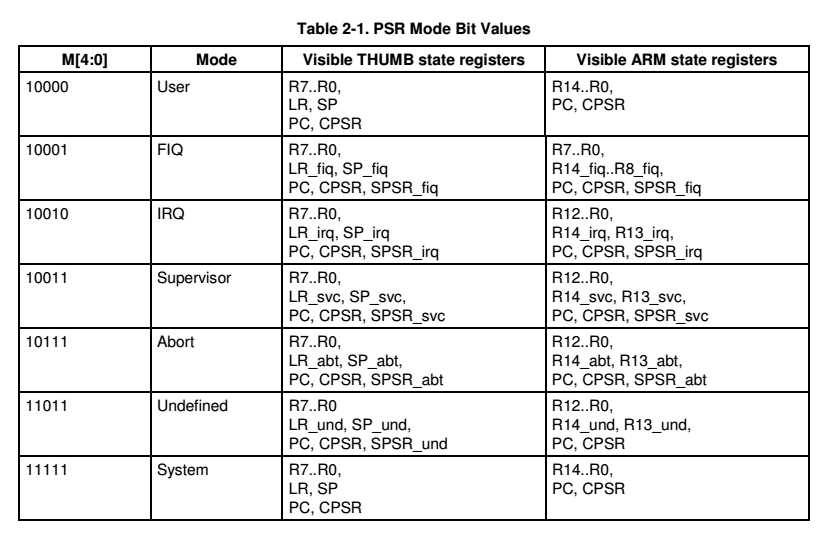

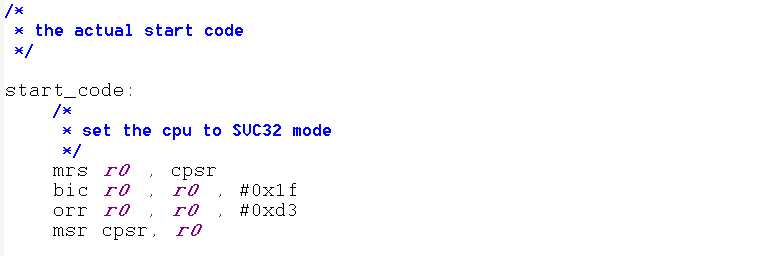

* CPU进入SVC模式

从数据手册上可以看到10011就是设置为管理模式

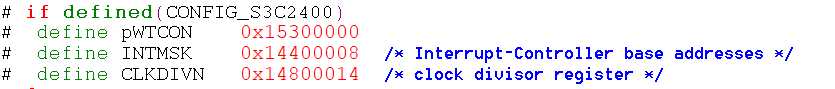

* 设置控制寄存器的地址

* 关闭看门狗

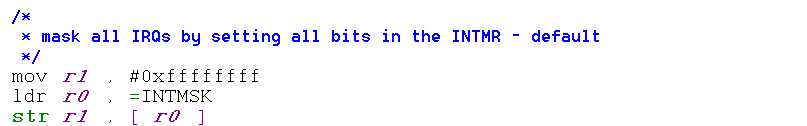

* 屏蔽中断

*设置时钟

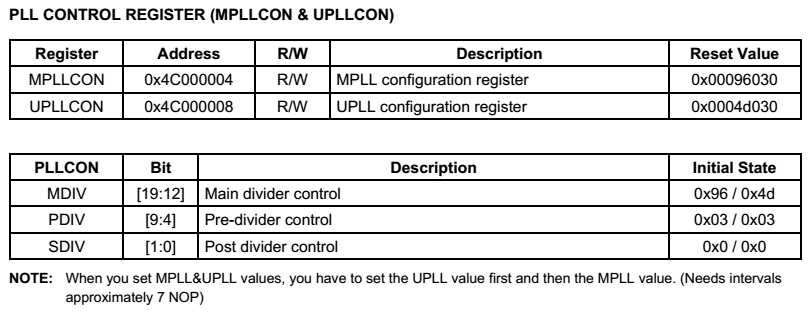

CPU上电几毫秒后,晶振输出稳定,FCLK=Fin(晶振频率),CPU开始执行指令。但实际上,FCLK可以高于Fin,为了提高系统时钟,需要用软件来启用PLL。这就需要设置CLKDIVN,MPLLCON,UPLLCON这3个寄存器。

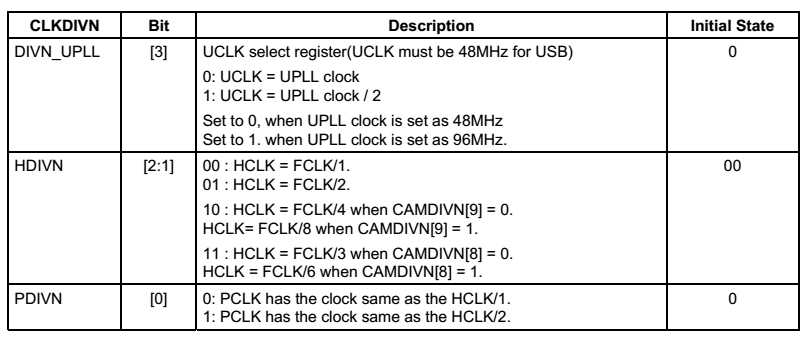

CLKDIVN寄存器,CLKDIVN寄存器用于设置FCLK,HCLK,PCLK三者间的比例

设置CLKDIVN为5,就将HDIVN设置为二进制的10,由于CAMDIVN[9]没有被改变过,取默认值0,因此HCLK = FCLK/4。

PDIVN被设置为1,因此PCLK= HCLK/2。因此分频比FCLK:HCLK:PCLK = 1:4:8 。

FCLK提供给ARM920T的时钟

HCLK 是提供给用于 ARM920T,存储器控制器,中断控制器,LCD 控制器,DMA 和 USB 主机模块的 AHB总线的时钟

PCLK 是提供给用于外设如WDT,IIS,I2C,PWM 定时器,MMC/SD 接口,ADC,UART,GPIO,RTC 和SPI的 APB 总线的时钟

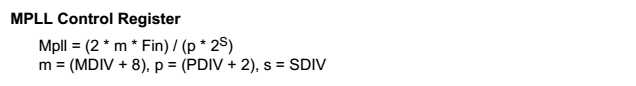

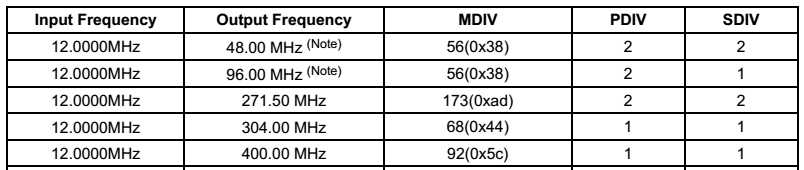

FCLK与Fin的关系如下面公式:

MPLLCON寄存器用于设置FCLK与Fin的倍数。MPLLCON的位[19:12]称为MDIV,位[9:4]称为PDIV,位[1:0]称为SDIV。

MPLLCON与UPLLCON的值可以根据参考:

MPLLCON=(0x7f<<12) | (0x02<<4) | (0x01) = 0x7f021

UPLLCON=(0x38<<12) | (0x02<<4) | (0x02) = 0x38022

以上是关于u-boot.2012.10——mini2440(启动流程分析)的主要内容,如果未能解决你的问题,请参考以下文章

编译U-Boot时command not found的解决方法

[mini2440] 使用 miniTool 给 mini2440 刷机

[Mini2440] 使用 miniTool 给 mini2440 刷机