嵌入式CISC模型机设计

Posted 子墨言良

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了嵌入式CISC模型机设计相关的知识,希望对你有一定的参考价值。

一、 课程设计的题目和内容

题目:设计一台嵌入式CISC模型计算机

采用定长CPU周期、联合控制方式,并运行能完成一定功能的机器语言源程序进行验证,机器语言源程序功能如下:

任意输入5个整数,输出最小负数的绝对值。

二、 系统的总体设计

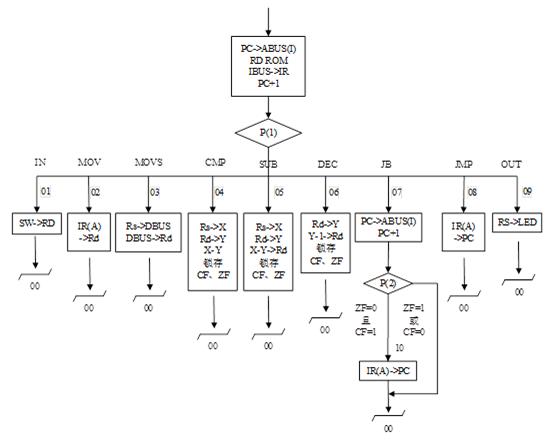

2.1 CISC模型机数据通路框图

CISC模型机数据通路框图如图1所示:

图1:CISC模型机数据通路框图

2.2地址转移逻辑电路及其逻辑表达式

地址转移逻辑电路的逻辑表达式如下:

SE5=1

SE4=NOT((CF AND NOT ZF )AND P2 AND T4);

SE3=NOT(I15 AND P1 AND T4);

SE2=NOT(I14 AND P1 AND T4);

SE1=NOT(I13 AND P1 AND T4);

SE0=NOT(I12 AND P1 AND T4);

三、 指令格式及指令系统

3.1命令格式

下面是系统中采用的9条指令及其格式,其中Rs为源寄存器,存放源操作数;Rd为目的寄存器,存放目的操作数所在的地址;im为立即数,addr为形式地址。

模型机规定数据的为无符号整数,且字长为16位,其格式如下:

(1) 输入指令

输入(IN1)指令采用双字节指令,其格式如下:

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

× × |

Rd |

×××××××× |

(2) MOV指令

MOV指令采用双字节指令,其格式如下:

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

× × |

Rd |

im |

(3) MOVS指令

存值指令,将Rs的值存入到地址[Rd]中。

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

Rs |

Rd |

×××××××× |

(4) 比较(CMP)指令

根据比较结果(Rs-Rd)的值决定跳转。

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

Rs |

Rd |

×××××××× |

(5) 减法(SUB)指令

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

Rs |

Rd |

×××××××× |

(6) 自减(DEC)指令

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

× × |

Rd |

×××××××× |

(7) 条件转移转移指令(JB,小于跳转) 指令

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

× × |

Rd |

addr |

“addr”中的值就是要转移的地址值。

(8) 无条件转移指令(JMP)指令

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

× × |

Rd |

addr |

“addr”中的值就是要转移的地址值。

(9) 输出(OUT1)指令

|

15 14 13 12 |

11 10 |

9 8 |

7-----------0 |

|

操作码 |

Rs |

× × |

×××××××× |

(10)Rs和Rd寄存器地址规定如下:

|

Rs Rd |

选定的寄存器 |

|

0 0 |

R0 |

|

0 1 |

R1 |

|

1 0 |

R2 |

|

1 1 |

R3 |

3.2指令系统

|

指令助记符 |

指令格式 |

功能 |

|||

|

15--12 |

11 10 |

9 8 |

7-----------0 |

||

|

IN Rd |

0001 |

×× |

Rd |

×××××××× |

输入设备→Rd |

|

MOV Rd, im |

0010 |

×× |

Rd |

im |

立即数→Rd |

|

MOVS Rs, [Rd] |

0011 |

Rs |

Rd |

×××××××× |

(Rs)->[Rd] |

|

CMP Rs, Rd |

0100 |

Rs |

Rd |

×××××××× |

(Rs)-(Rd),锁存标志位 |

|

SUB Rs, Rd |

0101 |

Rs |

Rd |

×××××××× |

(Rs)-(Rd)→Rd |

|

DEC Rd |

0110 |

×× |

Rd |

×××××××× |

(Rd)-1->(Rd) |

|

JB addr |

0111 |

×× |

×× |

addr |

若小于,则addr->PC |

|

JMP addr |

1000 |

×× |

×× |

addr |

addr->PC |

|

OUT Rs |

1001 |

Rs |

×× |

×××××××× |

(Rs)→输出设备 |

四、 汇编语言源程序及机器语言源程序

|

地址 (十六进制) |

汇编语言源程序 |

机器语言源程序 (二进制) |

机器语言源程序 (十六进制) |

|

00 |

MOV R1,00H |

0010 00 01 00000000 |

2100 |

|

01 |

MOV R2,05H |

0010 00 10 00000101 |

2205 |

|

02 |

MOV R3,00H |

0001 00 11 00000000 |

1300 |

|

03 |

L1: IN R0 |

0001 00 00 00000000 |

1000 |

|

04 |

DEC R2 |

0110 00 10 00000000 |

6200 |

|

05 |

CMP R2,R3 |

0100 10 11 00000000 |

4B00 |

|

06 |

JB O |

0111 00 00 00001110 |

700E |

|

07 |

CMP R3,R0 |

0100 11 00 00000000 |

4C00 |

|

08 |

JB L1 |

0111 00 00 00000011 |

7003 |

|

09 |

CMP R0,R1 |

0100 00 01 00000000 |

4100 |

|

0A |

JB L2 |

0111 00 00 00001100 |

700C |

|

0B |

JMP L1 |

1000 00 00 00000011 |

8003 |

|

0C |

L2: MOVS R0,R1 |

0011 00 01 00000000 |

3100 |

|

0D |

JMP L1 |

1000 00 00 00000011 |

8003 |

|

0E |

O: SUB R3,R1 |

0101 11 01 00000000 |

5D00 |

|

0F |

OUT R1 |

1001 01 00 00000000 |

9400 |

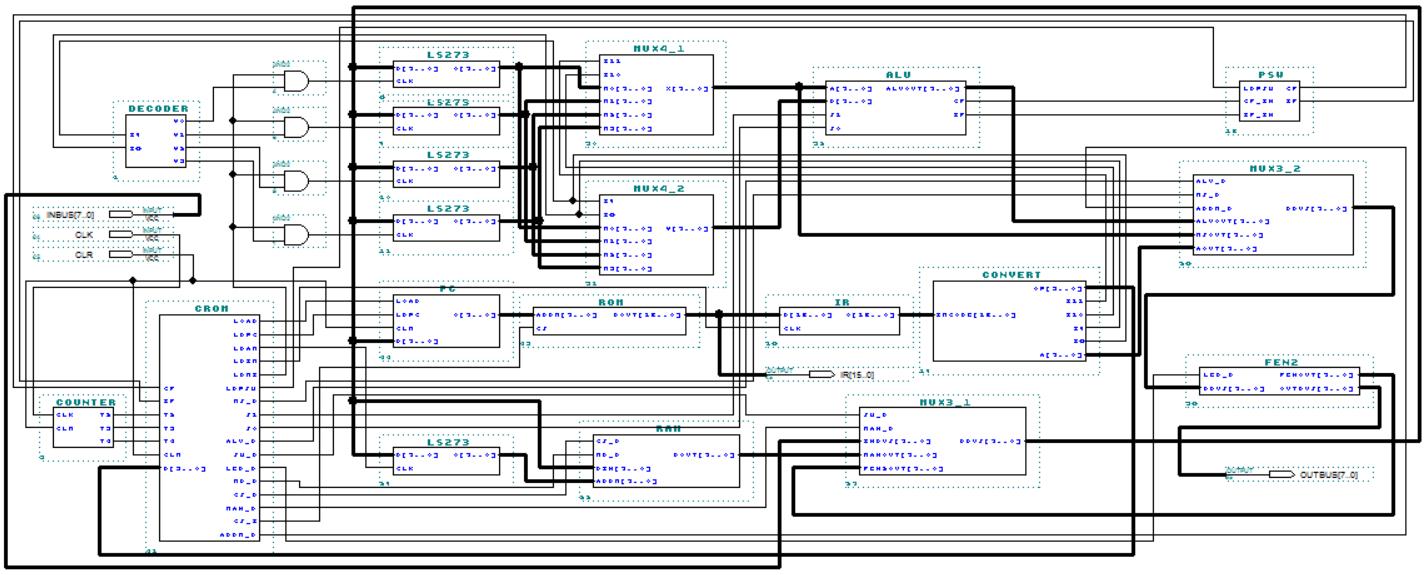

五、 机器指令微程序流程图

六、 微指令格式和微指令分配

按照要求,CISC模型机系统使用的微指令采用全水平型微指令,字长为25位,其中微命令字段为17位,P字段为2位,后继微地址为6位。由微指令格式和微指令的程序流程图编写的微指令代码表如下所示,在微指令的代码表中微命令字段从左边到右边代表微指令的信号依次是:LOAD、LDPC、LDAR、LDIR、LDRI、LDPSW、RS_B、S1、S0、ALU_B、SW_B、LED_B、RD_D、CS_D、RAM_B、CS_I、ADDR_B、P1、P2。

|

微 地 址 |

LOAD |

LDPC |

LDAR |

LDIR |

LDRI |

LD PSW |

RS _B |

S1 |

S0 |

ALU_B |

SW_B |

LED_B |

RD_D |

CS_D |

RAM_B |

CS_ I |

ADDR_B |

P1 |

P2 |

uA5 - uA0 |

|

00 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

000000 |

|

01 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

000000 |

|

02 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

000000 |

|

03 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

000000 |

|

04 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

000000 |

|

05 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

000000 |

|

06 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

000000 |

|

07 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

000000 |

|

08 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

000000 |

|

09 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

000000 |

|

10 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

000000 |

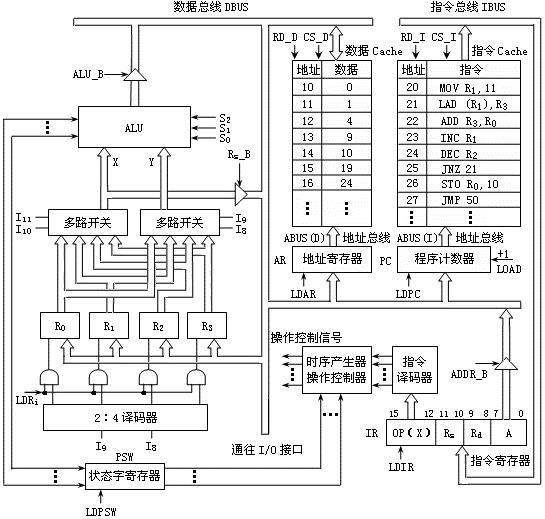

七、 顶层电路设计

CISC模型机顶层电路设计如下:

图2 CISC模型机的顶层电路图

八、 功能仿真波形图及结果分析

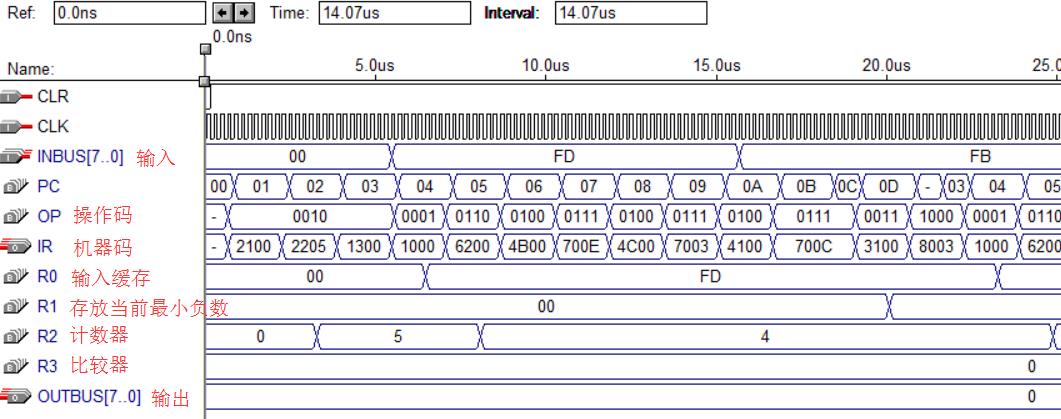

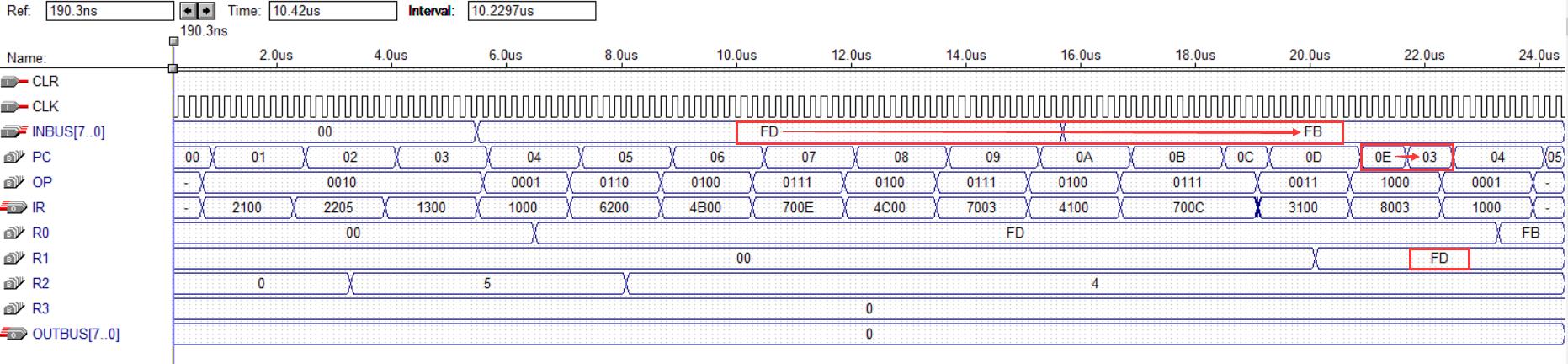

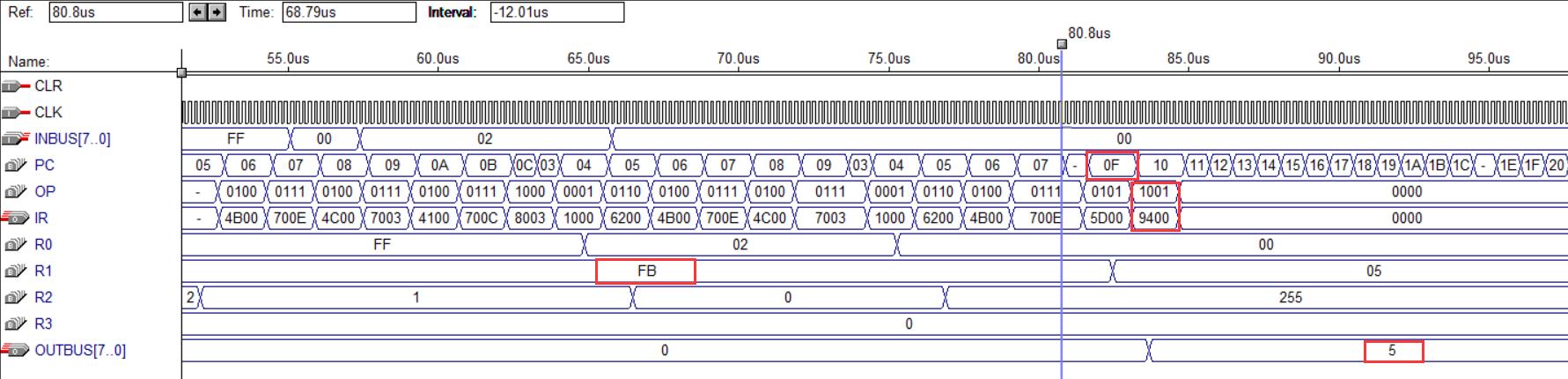

波形图中的INBUS代表输入,在PC为04H时开始输入第一个数;OP为指令的操作码,IR为机器语言源程序编码(十六进制);R0-R3为四个寄存器,R0用作输入缓存,R1用于存放当前最小负数,R2用作计数器,R3用作比较器,值固定为0,可判断循环次数和正负;OUTBUS为输出。

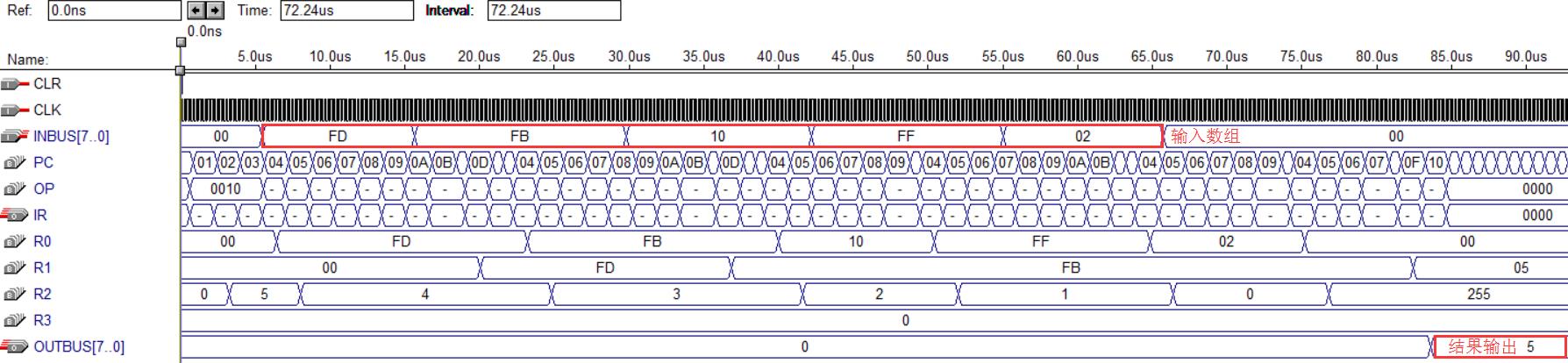

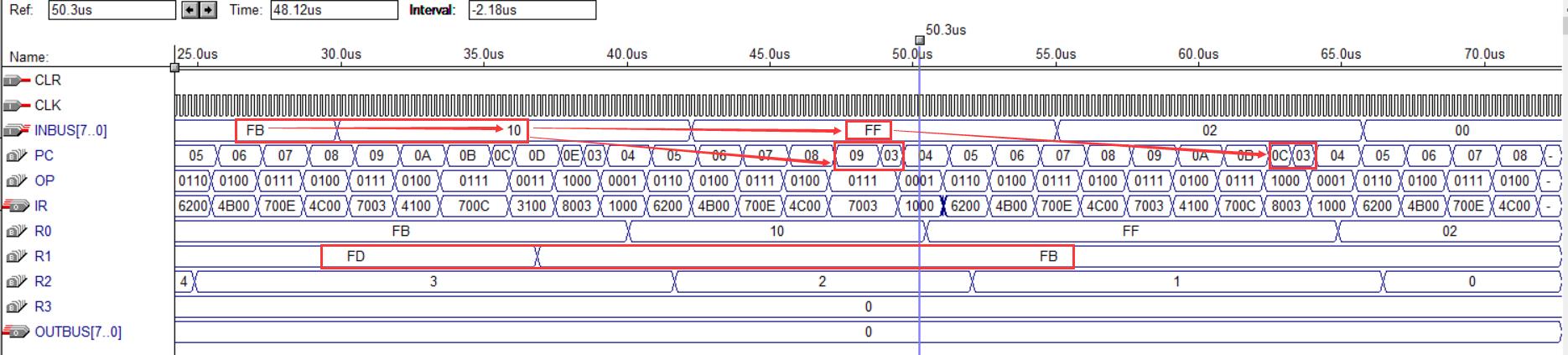

从上图可以看到输入数据和输出结果,输入分别为FDH、FBH、10H、FFH和02H,最后的输出结果为5,即FBH的绝对值。

该图显示了从输入FDH和FBH后程序的执行情况。输入FDH后判定其为负数,将其存入R1中最为当前最小负数。由于该输入既是负数,也是最小负数,所以程序会执行到PC为0EH的地方,然后跳转到PC为03H的地方开始下一次循环。

根据输入前后值的不同,程序的跳转位置亦会不同,如上图中所示陆续输入FBH、10H和FFH后PC跳转的地址不同。首先,输入FBH后,它为负数且小于第一个输入FDH,所以会存入R1中替换原来的最小负数。输入10H后,由于为正数,在比较完正负后,即PC地址为09H的地方,就会跳转到PC地址为03H的地方进行下一次循环,而不会进入下面是否为最小值得比较。而输入FFH后,由于为负数,则先比较正负之后还要比较大小之后才会跳转,即PC地址为0CH的地方,然后跳转到PC地址为03H的地方进行最后一次循环。

如上图所示,在输入FBH之后没有再输入比它小的数,所以R1的内容即最小负数保持为FBH。最后,执行完5此循环之后在PC地址为0FH的地方输出最终结果5,此时指令的操作码和机器地址分别为1001和9400。

九、 问题分析

1、在保存文件时,文件存储路径不能用中文命名,否则会出现错误。在编译或者仿真某文件时,须注意将该文件Set Project to Current File。在编译文件出现错误时,需要耐心检查代码,很可能只是漏下或者多打了个分号。

2、在绘制gdf图时,不能将电路图命名为在图中需要用到的元器件的名称,否则会出现不能导入该元器件的现象。在为仿真图添加节点后,虽然可以重命名该节点,但有时导入错误节点并且重新命名后往往很难排查,画顶层图的时候,得小心谨慎,不然线跟线很容易重合在一起。

3、在校对程序无误时,OUTBUS没有数据输出,很可能是因为ENDTIME设置的时间过短导致程序没运行完而出不来结果。如果发现波形仿真图跟自己设想的不一样,可以通过跟踪PC、ADDR、ALU,按照程序的执行步骤一步一步查看检查,找到错误的原因,可能是逻辑错误、输入时的大意等。也可以找同学互相检查以避免自己的定式思维导致的问题。

4、每进行下一步的时候都得确定上一步准确无误,比如在设计指令格式的时候首先要确保汇编程序无误,或在设计机器语言源程序时之前要确保指令格式正确等等,如果自己不能确定可以找同学互相检查以排查错误。

十、 软件清单

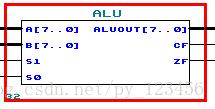

(1) ALU单元

|

S1 |

S0 |

功能 |

|

0 |

0 |

执行减法(SUB) |

|

0 |

1 |

执行比较(CMP) |

|

1 |

0 |

执行自减1(DEC) |

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_SIGNED.ALL;

ENTITY ALU IS

PORT(

A:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

S1,S0:IN STD_LOGIC;

ALUOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

CF,ZF:OUT STD_LOGIC

);

END ALU;

ARCHITECTURE AOF ALU IS

SIGNAL AA,BB,TEMP:STD_LOGIC_VECTOR(8DOWNTO 0);

BEGIN

PROCESS

BEGIN

IF(S1=\'0\' AND S0=\'0\')THEN --执行减法运算

ALUOUT<=A-B;

IF(A<B)THEN

CF<=\'1\'; --借位标志

ZF<=\'0\'; --零标志

ELSIF(A=B)THEN

CF<=\'0\';

ZF<=\'1\';

ELSE

CF<=\'0\';

ZF<=\'0\';

END IF;

ELSIF(S1=\'0\' AND S0=\'1\')THEN --执行比较运算

ALUOUT<=A-B;

IF(A<B)THEN

CF<=\'1\';

ZF<=\'0\';

ELSIF(A=B)THEN

CF<=\'0\';

ZF<=\'1\';

ELSE

CF<=\'0\';

ZF<=\'0\';

END IF;

ELSIF(S1=\'1\' AND S0=\'0\')THEN --执行减1运算

AA<=\'0\'&B;

TEMP<=AA-1;

ALUOUT<=TEMP(7 DOWNTO0);

CF<=TEMP(8);

IF(TEMP="000000000")THEN

ZF<=\'1\';

ELSE

ZF<=\'0\';

END IF;

ELSE

ALUOUT<="00000000";

--CF<=\'0\';

ZF<=\'0\';

END IF;

END PROCESS;

END A;

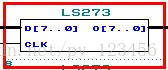

(2) 寄存器单元

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY LS273 IS

PORT(

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CLK:IN STD_LOGIC;

O:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END LS273;

ARCHITECTURE AOF LS273 IS

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK\'EVENT ANDCLK=\'1\')THEN

O<=D;

END IF;

END PROCESS;

END A;

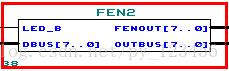

(3) 1:2分配器单元

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY FEN2 IS

PORT(

LED_B:IN STD_LOGIC;

DBUS:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

FENOUT,OUTBUS:OUT STD_LOGIC_VECTOR(7DOWNTO 0)

);

END FEN2;

ARCHITECTURE AOF FEN2 IS

BEGIN

PROCESS

BEGIN

IF(LED_B=\'0\')THEN

OUTBUS<=DBUS;

ELSE

FENOUT<=DBUS;

END IF;

END PROCESS;

END A;

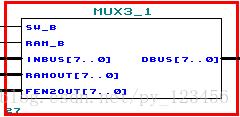

(4) 三选一数据选择单元

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY MUX3_1IS

PORT(

SW_B,RAM_B:IN STD_LOGIC;

INBUS,RAMOUT,FEN2OUT:INSTD_LOGIC_VECTOR(7 DOWNTO 0);

DBUS:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END MUX3_1;

ARCHITECTURE AOF MUX3_1 IS

BEGIN

PROCESS

BEGIN

IF(SW_B=\'1\' AND RAM_B=\'0\') THEN

DBUS<=RAMOUT;

ELSIF(SW_B=\'1\' AND RAM_B=\'1\') THEN

DBUS<=FEN2OUT;

ELSE

DBUS<=INBUS;

END IF;

END PROCESS;

END A;

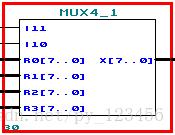

(5) 四选一数据选择单元

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY MUX4_1IS

PORT(

I11,I10:IN STD_LOGIC;

R0,R1,R2,R3:IN STD_LOGIC_VECTOR(7 DOWNTO0);

X:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END MUX4_1;

ARCHITECTURE AOF MUX4_1 IS

BEGIN

PROCESS

BEGIN

IF(I11=\'0\' AND I10=\'0\')THEN

X<=R0;

ELSIF(I11=\'0\' AND I10=\'1\')THEN

X<=R1;

ELSIF(I11=\'1\' AND I10=\'0\')THEN

X<=R2;

ELSE

X<=R3;

END IF;

END PROCESS;

END A;

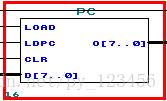

(6) 程序计数单元PC

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY PC IS

PORT(

LOAD,LDPC,CLR:IN STD_LOGIC;

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

O:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END PC;

ARCHITECTURE AOF PC IS

SIGNALQOUT:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(LDPC,CLR,LOAD)

BEGIN

IF(CLR=\'0\')THEN

QOUT<="00000000";

ELSIF(LDPC\'EVENT ANDLDPC=\'1\')THEN

IF(LOAD=\'0\')THEN

QOUT<=D; --BUS->PC

ELSE

QOUT<=QOUT+1; --PC+1

END IF;

END IF;

END PROCESS;

O<=QOUT;

END A;

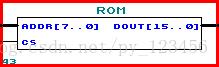

(7) 主存储单元ROM

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ROM IS

PORT(

DOUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

ADDR:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CS:IN STD_LOGIC

);

END ROM;

ARCHITECTURE AOF ROM IS

BEGIN

DOUT<="0010000100000000"WHENADDR="00000000"AND CS=\'0\'ELSE

"0010001000000101"WHENADDR="00000001"AND CS=\'0\'ELSE

"0001001100000000"WHENADDR="00000010"AND CS=\'0\'ELSE

"0001000000000000"WHENADDR="00000011"AND CS=\'0\'ELSE

"0110001000000000"WHENADDR="00000100"AND CS=\'0\'ELSE

"0100101100000000"WHENADDR="00000101"AND CS=\'0\'ELSE

"0111000000001110"WHENADDR="00000110"AND CS=\'0\'ELSE

"0100110000000000"WHENADDR="00000111"AND CS=\'0\'ELSE

"0111000000000011"WHENADDR="00001000"AND CS=\'0\'ELSE

"0100000100000000"WHENADDR="00001001"AND CS=\'0\'ELSE

"0111000000001100"WHENADDR="00001010"AND CS=\'0\'ELSE

"1000000000000011"WHENADDR="00001011"AND CS=\'0\'ELSE

"0011000100000000"WHENADDR="00001100"AND CS=\'0\'ELSE

"1000000000000011"WHENADDR="00001101"AND CS=\'0\'ELSE

"0101110100000000"WHENADDR="00001110"AND CS=\'0\'ELSE

"1001010000000000"WHENADDR="00001111"AND CS=\'0\'ELSE

"00000000";

END A;

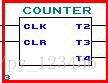

(8) 时序产生器

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNTERIS

PORT(

CLK,CLR:IN STD_LOGIC;

T2,T3,T4:OUT STD_LOGIC

);

END COUNTER;

ARCHITECTURE AOF COUNTER IS

SIGNALX:STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

PROCESS(CLK,CLR)

BEGIN

IF(CLR=\'0\') THEN

T2<=\'0\';

T3<=\'0\';

T4<=\'0\';

X<="00";

ELSIF(CLK\'EVENT AND CLK=\'1\')THEN

X<=X+1;

T2<=(NOT X(1)) AND X(0);

T3<=X(1) AND (NOT X(0));

T4<=X(1) AND X(0);

END IF;

END PROCESS;

END A;

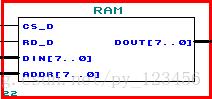

(9) RAM

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY RAM IS

PORT(

CS_D,RD_D:IN STD_LOGIC;

DIN:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

ADDR:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END RAM;

ARCHITECTURE AOF RAM IS

TYPE MEMORY ISARRAY(0 TO 31)OF STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(CS_D)

VARIABLE MEM:MEMORY;

BEGIN

IF(CS_D\'EVENT AND CS_D=\'0\')THEN

IF(RD_D=\'0\')THEN

MEM(CONV_INTEGER(ADDR(4DOWNTO 0))):=DIN;

ELSE

DOUT<=MEM(CONV_INTEGER(ADDR(4DOWNTO 0)));

END IF;

END IF;

END PROCESS;

END A;

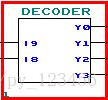

(10) 二四译码器

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY DECODERIS

PORT(

I9,I8:IN STD_LOGIC;

Y0,Y1,Y2,Y3:OUT STD_LOGIC

);

END DECODER;

ARCHITECTURE AOF DECODER IS

BEGIN

PROCESS

BEGIN

IF(I9=\'0\' AND I8=\'0\')THEN

Y0<=\'1\';

以上是关于嵌入式CISC模型机设计的主要内容,如果未能解决你的问题,请参考以下文章