VHDL设计----十进制计数器

Posted warms

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VHDL设计----十进制计数器相关的知识,希望对你有一定的参考价值。

一、异步复位加法计数器

代码:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity CNT10 is port( CLK,RST,EN: in std_logic; DOUT : out std_logic_vector (3 downto 0); COUT : OUT std_logic ); end CNT10; architecture behav of CNT10 is begin process(CLK,RST,EN) variable Q : std_logic_vector (3 downto 0); begin if RST = \'1\' then Q := (others => \'0\'); elsif CLK \'event and CLK = \'1\' then if EN = \'1\' then if Q < 9 then Q := Q + 1; else Q := (others => \'0\'); end if; end if; end if; if Q = "1001" then COUT <= \'1\'; else COUT <= \'0\'; end if; DOUT <= Q; end process; end behav;

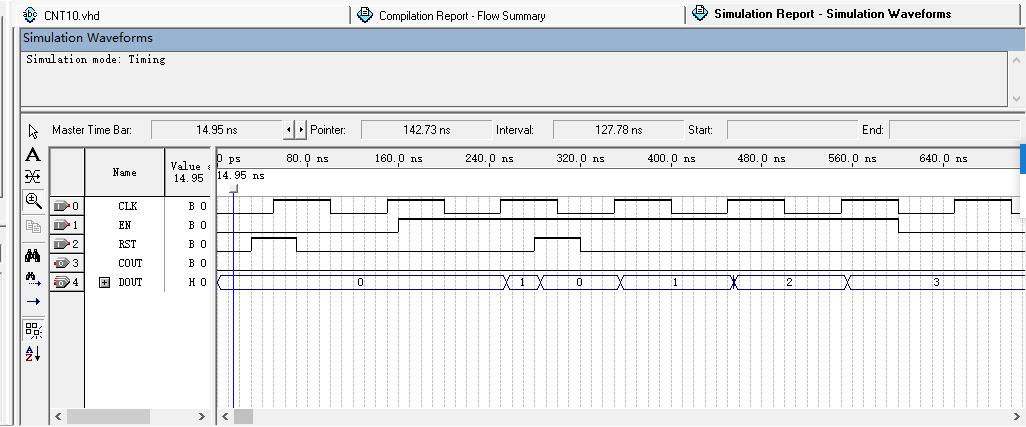

仿真:

RST信号与CLK信号无关,随时可以置零

二、同步复位加法计数器

代码:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity CNT10 is port( CLK,RST,EN: in std_logic; DOUT : out std_logic_vector (3 downto 0); COUT : OUT std_logic ); end CNT10; architecture behav of CNT10 is begin process(CLK,RST,EN) variable Q : std_logic_vector (3 downto 0); begin if CLK \'event and CLK = \'1\' then if RST = \'1\' then Q := (others => \'0\'); else if EN = \'1\' then if Q < 9 then Q := Q + 1; else Q := (others => \'0\'); end if; end if; end if; end if; if Q = "1001" then COUT <= \'1\'; else COUT <= \'0\'; end if; DOUT <= Q; end process; end behav;

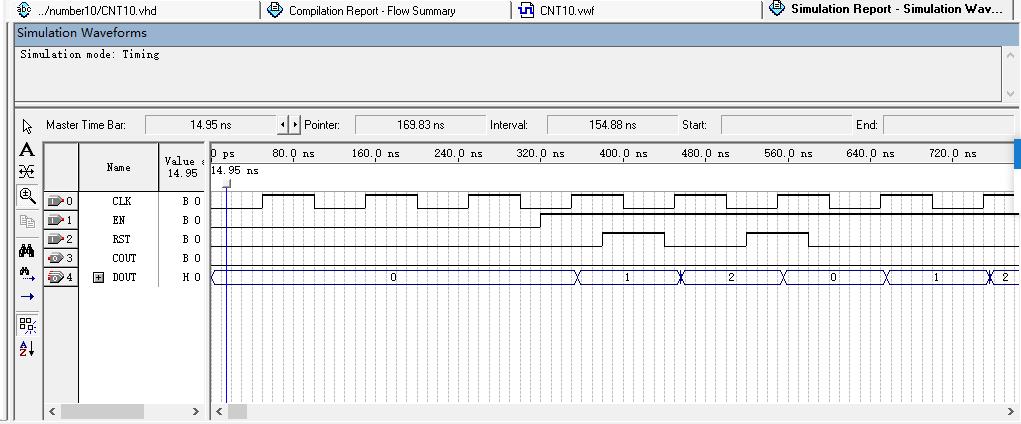

仿真:

RST信号只有等到CLK信号的下一个上升沿到时才能清零

三、总结

所谓“同步”是指与系统时钟同步。同步复位是指当复位信号有效时,并不立刻生效,而是要等到复位信号有效之后系统时钟的有效边沿到达时才会生效;

而异步复位则是立刻生效的,只要复位信号有效,无论系统时钟是怎样的,系统都会立即被复位。

在用VHDL描述复位信号时,在系统时钟有效边沿到达之后才判断同步复位是否有效;而对异步复位的判断则与系统时钟无关。

同步复位: IF clock\'event AND clock=\'1\' THEN IF reset=\'1\' THEN -- 复位系统 ELSE -- 正常运作 END IF; END IF; 异步复位: IF reset=\'1\' THEN -- 复位系统 ELSIF clock\'event AND clock=\'1\' THEN -- 正常运作 END IF;

以上是关于VHDL设计----十进制计数器的主要内容,如果未能解决你的问题,请参考以下文章