buildroot构建项目--- u-boot 2017.11 适配开发板修改 4 ---- 系统启动初始化之三

Posted 游戏进行中

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了buildroot构建项目--- u-boot 2017.11 适配开发板修改 4 ---- 系统启动初始化之三相关的知识,希望对你有一定的参考价值。

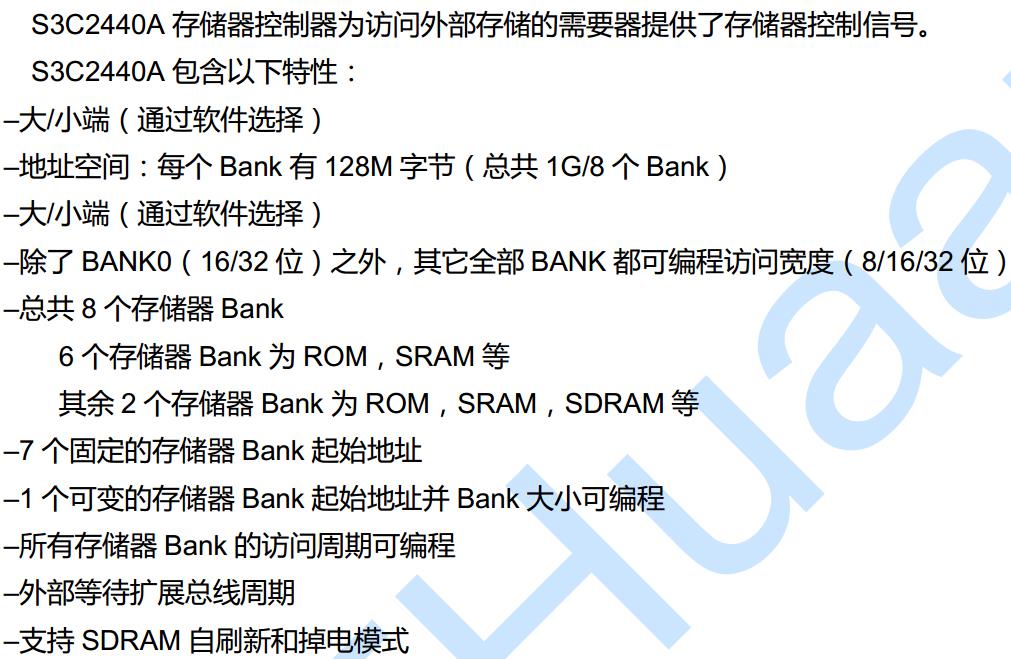

一、内存控制器

在关闭了MMU和caches 之后 就进入lowlevel_init 函数,对内存控制器进行初始化。lowlevel_init.S (board\\samsung\\mini2440)

1.1 内存控制器介绍

前面已经看过这张表格了。从这张表格中可以看处,我们的程序代码,不管使用不使用 NAND Flash 都是从0地址开始启动,只不过使用 Nand flash 需要将前4K代码拷贝进 SRAM中去。

1.2 内存控制器的寄存器

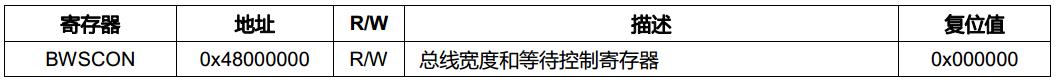

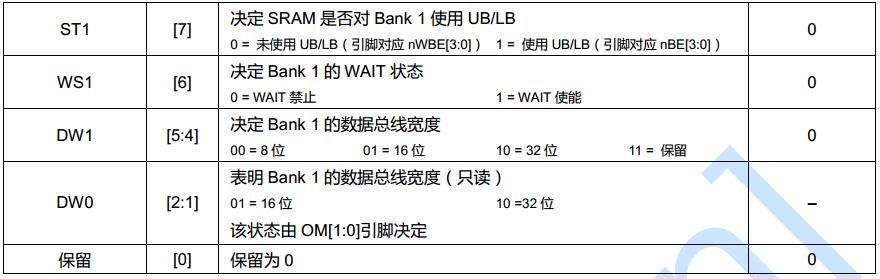

1.2.1 总线宽度和等待控制寄存器

每一个 BANK 对应一个 DW WS ST位

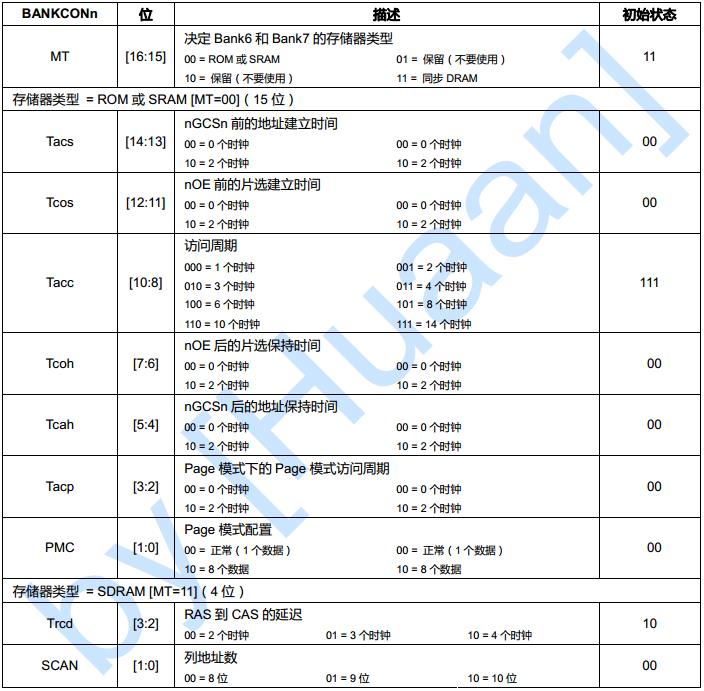

1.2.2 BANK 控制寄存器

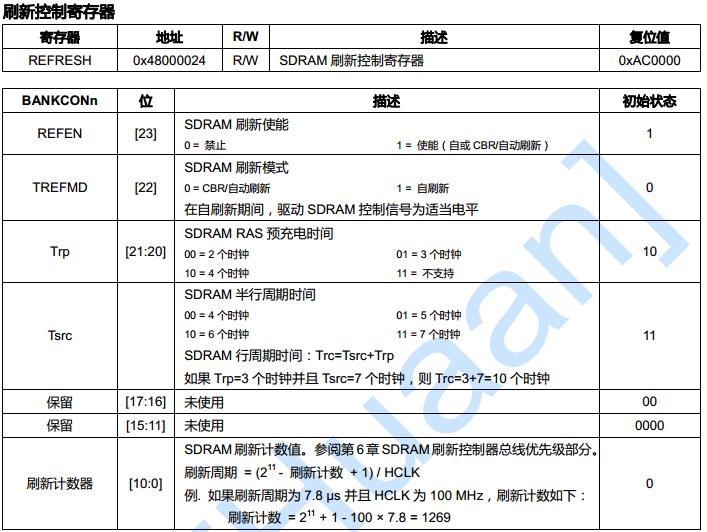

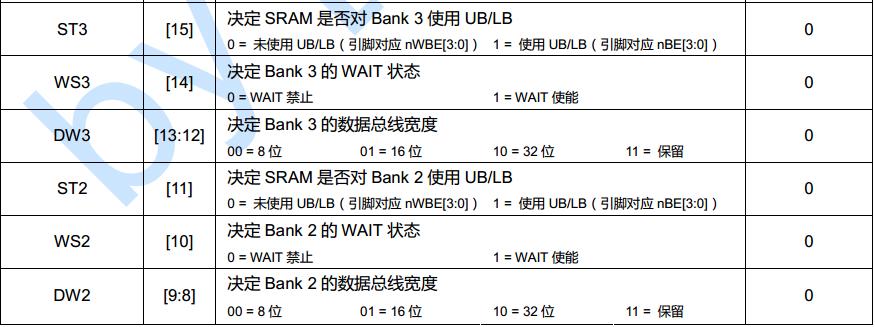

1.2.3 刷新控制寄存器

1.2.4 Bank 大小寄存器

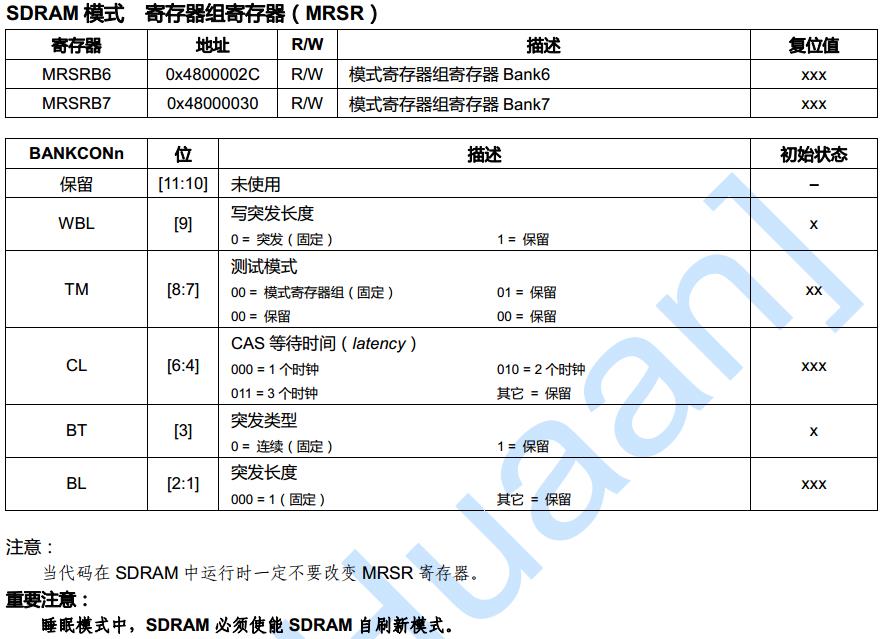

1.2.5 SDRAM模式寄存器

二、代码修改

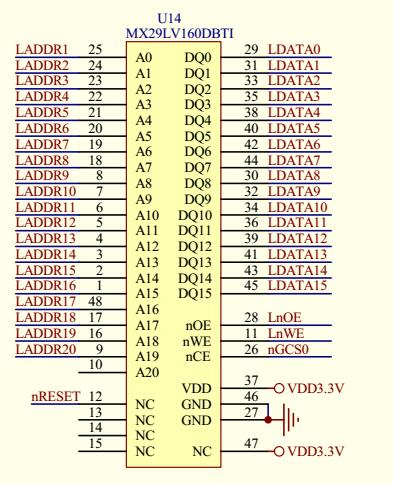

2.1 硬件电路图

JZ2440的硬件电路图如下:

由图中,可以知道 norflash 是16位的。所以我们要设置我们的位宽位 16位

片选信号 nCE 接在 nGCS0 上,则我们的控制寄存器选择 BANKCON0

- nGCS0:norflash,16位位宽

- nGCS1:未接

- nGCS2:未接

- nGCS3:未接,用于外部扩展

- nGCS4:DM9000网卡,16位位宽

- nGCS5:未接,用于外部扩展

- nGCS6:SDRAM,32位位宽

- nGCS7:nGCS7未接

2.1 代码修改

代码修改较少,主要是根据各个芯片手册进行配置

1 /* 2 * Memory Setup stuff - taken from blob memsetup.S 3 * 4 * Copyright (C) 1999 2000 2001 Erik Mouw (J.A.K.Mouw@its.tudelft.nl) and 5 * Jan-Derk Bakker (J.D.Bakker@its.tudelft.nl) 6 * 7 * Modified for the Samsung SMDK2410 by 8 * (C) Copyright 2002 9 * David Mueller, ELSOFT AG, <d.mueller@elsoft.ch> 10 * 11 * SPDX-License-Identifier: GPL-2.0+ 12 */ 13 14 15 #include <config.h> 16 #include <version.h> 17 18 19 /* some parameters for the board */ 20 21 /* 22 * 23 * Taken from linux/arch/arm/boot/compressed/head-s3c2410.S 24 * 25 * Copyright (C) 2002 Samsung Electronics SW.LEE <hitchcar@sec.samsung.com> 26 * 27 */ 28 29 #define BWSCON 0x48000000 30 31 /* BWSCON */ 32 #define DW8 (0x0) /* 8位总线宽度 */ 33 #define DW16 (0x1) /* 16位总线宽度 */ 34 #define DW32 (0x2) /* 32位总线宽度 */ 35 #define WAIT (0x1<<2) /* BANK的 WAIT 状态,当前定义的此位是1,使能 */ 36 #define UBLB (0x1<<3) /* 决定 SRAM 是否对 Bank 7 使用 UB/LB,使能 */ 37 38 /* BWSCON中 BANK0 位宽由OM引脚决定,其余不用设置 */ 39 #define B1_BWSCON (DW32) /* B1 位宽为32位,未用到 */ 40 #define B2_BWSCON (DW16) /* B2 位宽为16位,未用到 */ 41 #define B3_BWSCON (DW16 + WAIT + UBLB) /* B3 位宽为16位,未用到 */ 42 #define B4_BWSCON (DW16) /* B4 位宽为16位,DM9000网卡,16位 */ 43 #define B5_BWSCON (DW16) /* B5 位宽为16位,未用到 */ 44 #define B6_BWSCON (DW32) /* B6 位宽为32位,接SDRAM,32位 */ 45 #define B7_BWSCON (DW32) /* B7 位宽为32位,未用到 */ 46 47 /* BANK0CON,norflash,设为复位默认值即可 */ 48 #define B0_Tacs 0x0 /* 0clk */ 49 #define B0_Tcos 0x0 /* 0clk */ 50 #define B0_Tacc 0x7 /* 14clk */ 51 #define B0_Tcoh 0x0 /* 0clk */ 52 #define B0_Tah 0x0 /* 0clk */ 53 #define B0_Tacp 0x0 54 #define B0_PMC 0x0 /* normal */ 55 56 /* BANK1CON,未定义,设为复位默认值即可 */ 57 #define B1_Tacs 0x0 /* 0clk */ 58 #define B1_Tcos 0x0 /* 0clk */ 59 #define B1_Tacc 0x7 /* 14clk */ 60 #define B1_Tcoh 0x0 /* 0clk */ 61 #define B1_Tah 0x0 /* 0clk */ 62 #define B1_Tacp 0x0 63 #define B1_PMC 0x0 64 65 /* BANK2CON,未定义,设为复位默认值即可 */ 66 #define B2_Tacs 0x0 67 #define B2_Tcos 0x0 68 #define B2_Tacc 0x7 69 #define B2_Tcoh 0x0 70 #define B2_Tah 0x0 71 #define B2_Tacp 0x0 72 #define B2_PMC 0x0 73 74 /* BANK3CON,未定义,设为复位默认值即可 */ 75 #define B3_Tacs 0x0 /* 0clk */ 76 #define B3_Tcos 0x3 /* 4clk */ 77 #define B3_Tacc 0x7 /* 14clk */ 78 #define B3_Tcoh 0x1 /* 1clk */ 79 #define B3_Tah 0x0 /* 0clk */ 80 #define B3_Tacp 0x3 /* 6clk */ 81 #define B3_PMC 0x0 /* normal */ 82 83 /* BANK4CON,DM9000网卡,设为复位默认值即可 */ 84 #define B4_Tacs 0x0 /* 0clk */ 85 #define B4_Tcos 0x0 /* 0clk */ 86 #define B4_Tacc 0x7 /* 14clk */ 87 #define B4_Tcoh 0x1 /* 1clk */ 88 #define B4_Tah 0x0 /* 0clk */ 89 #define B4_Tacp 0x0 90 #define B4_PMC 0x0 /* normal */ 91 92 /* BANK5CON,未定义,设为复位默认值即可 */ 93 #define B5_Tacs 0x0 /* 0clk */ 94 #define B5_Tcos 0x0 /* 0clk */ 95 #define B5_Tacc 0x7 /* 14clk */ 96 #define B5_Tcoh 0x0 /* 0clk */ 97 #define B5_Tah 0x0 /* 0clk */ 98 #define B5_Tacp 0x0 99 #define B5_PMC 0x0 /* normal */ 100 101 /* BANK6CON,SDRAM */ 102 #define B6_MT 0x3 /* 同步SDRAM */ 103 #define B6_Trcd 0x1 /* 3clk */ 104 #define B6_SCAN 0x1 /* 9bit */ 105 106 /* BANK7CON,未定义,设为复位默认值即可 */ 107 #define B7_MT 0x3 /* SDRAM */ 108 #define B7_Trcd 0x1 /* 3clk */ 109 #define B7_SCAN 0x1 /* 9bit */ 110 111 /* REFRESH parameter,刷新寄存器,主要是设置SDRAM */ 112 #define REFEN 0x1 /* Refresh enable */ 113 #define TREFMD 0x0 /* SDRAM 刷新模式 为自刷新 */ 114 #define Trp 0x0 /* SDRAM RAS 预充电时间为2clk */ 115 #define Trc 0x3 /* SDRAM 半行周期时间 7clk */ 116 #define Tchr 0x0 /* 保留位,不需要设置 */ 117 #define REFCNT 0x4f4 /* period=15.6us, HCLK=60Mhz, (2048+1-15.6*60) */ 118 /**************************************/ 119 120 _TEXT_BASE: 121 .word CONFIG_SYS_TEXT_BASE 122 123 .globl lowlevel_init 124 lowlevel_init: 125 /* memory control configuration */ 126 /* make r0 relative the current location so that it */ 127 /* reads SMRDATA out of FLASH rather than memory ! */ 128 ldr r0, =SMRDATA /* 获取SMRDATA的地址 */ 129 ldr r1, _TEXT_BASE /* 获取代码基地址 */ 130 sub r0, r0, r1 /* 计算SMRDATA相对与代码基地址的偏移量 */ 131 ldr r1, =BWSCON /* 总线位宽控制器地址赋值给R1 */ 132 add r2, r0, #13*4 /* r2 = r0 + 52,即将 SMRDATA的结束地址赋值给 r2 */ 133 /* 进入循环,按照预先的设计设定每个BANK的属性。 */ 134 0: 135 ldr r3, [r0], #4 /* 将存储器地址为R0的字数据读入寄存器R3,并将R0+4 */ 136 str r3, [r1], #4 /* 将R3中的字数据写入以R1为地址的存储器中,并将新地址R1+4写入R1。 */ 137 cmp r2, r0 138 bne 0b 139 140 /* everything is fine now */ 141 mov pc, lr 142 143 .ltorg 144 /* the literal pools origin */ 145 146 SMRDATA: 147 .word (0+(B1_BWSCON<<4)+(B2_BWSCON<<8)+(B3_BWSCON<<12)+(B4_BWSCON<<16)+(B5_BWSCON<<20)+(B6_BWSCON<<24)+(B7_BWSCON<<28)) 148 .word ((B0_Tacs<<13)+(B0_Tcos<<11)+(B0_Tacc<<8)+(B0_Tcoh<<6)+(B0_Tah<<4)+(B0_Tacp<<2)+(B0_PMC)) 149 .word ((B1_Tacs<<13)+(B1_Tcos<<11)+(B1_Tacc<<8)+(B1_Tcoh<<6)+(B1_Tah<<4)+(B1_Tacp<<2)+(B1_PMC)) 150 .word ((B2_Tacs<<13)+(B2_Tcos<<11)+(B2_Tacc<<8)+(B2_Tcoh<<6)+(B2_Tah<<4)+(B2_Tacp<<2)+(B2_PMC)) 151 .word ((B3_Tacs<<13)+(B3_Tcos<<11)+(B3_Tacc<<8)+(B3_Tcoh<<6)+(B3_Tah<<4)+(B3_Tacp<<2)+(B3_PMC)) 152 .word ((B4_Tacs<<13)+(B4_Tcos<<11)+(B4_Tacc<<8)+(B4_Tcoh<<6)+(B4_Tah<<4)+(B4_Tacp<<2)+(B4_PMC)) 153 .word ((B5_Tacs<<13)+(B5_Tcos<<11)+(B5_Tacc<<8)+(B5_Tcoh<<6)+(B5_Tah<<4)+(B5_Tacp<<2)+(B5_PMC)) 154 .word ((B6_MT<<15)+(B6_Trcd<<2)+(B6_SCAN)) 155 .word ((B7_MT<<15)+(B7_Trcd<<2)+(B7_SCAN)) 156 .word ((REFEN<<23)+(TREFMD<<22)+(Trp<<20)+(Trc<<18)+(Tchr<<16)+REFCNT) 157 .word 0xb1 /*64M bank大小,使能突发操作,禁止 SDRAM 掉电模式,SCLK 只在访问期间有效*/ 158 .word 0x30 /* MRSRB6,写突发长度是使能,测试模式为模式寄存器组,CAS 等待时间为3clk,突发类型为连续,突发长度为1 */ 159 .word 0x30

以上是关于buildroot构建项目--- u-boot 2017.11 适配开发板修改 4 ---- 系统启动初始化之三的主要内容,如果未能解决你的问题,请参考以下文章

buildroot构建项目--- u-boot 2017.11 适配开发板修改 4 ---- 系统启动初始化之四

buildroot构建项目--- u-boot 2017.11 适配开发板修改 5 ---- 系统启动初始化之五