(筆記) Edge wait & Level wait (verilog)

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了(筆記) Edge wait & Level wait (verilog)相关的知识,希望对你有一定的参考价值。

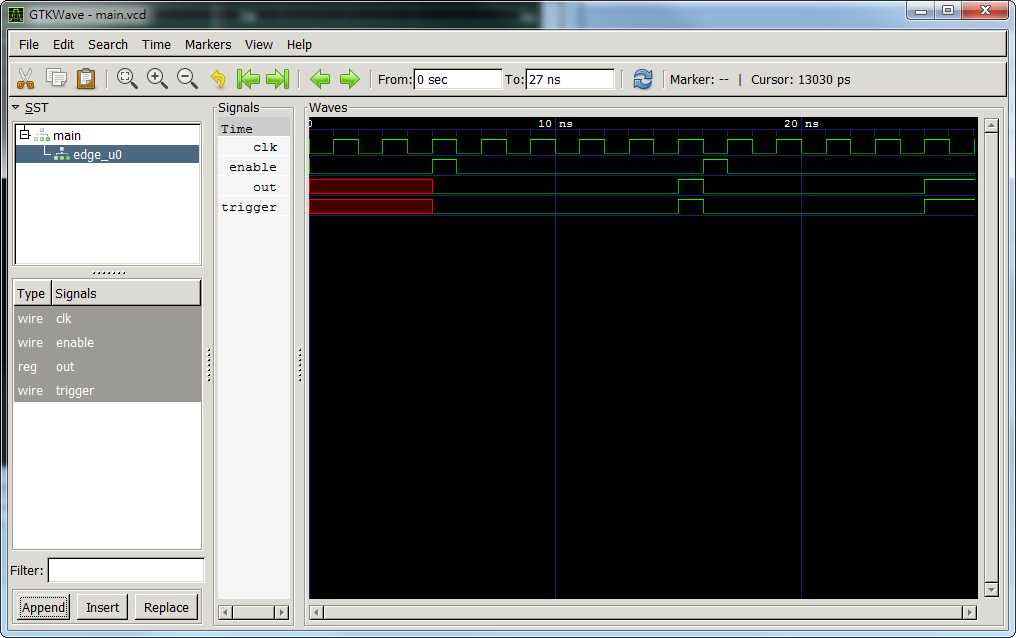

Edge wait : 經過模擬得知他應該是等條件處發後看設定幾個clk之後處理下一件事情。

edge wait verilog code

1 module edge_wait_example(enable, clk, trigger); 2 3 input enable, clk; 4 output trigger; 5 reg out; 6 assign trigger = out; 7 always @ (posedge enable) begin 8 out = 0; 9 // Wait for 5 clock cycles 10 repeat(5) begin @(posedge clk); 11 end 12 out = 1; 13 end 14 15 endmodule

edge wait tb

1 `include "edge_wait_example.v" 2 `timescale 1ns/100ps 3 4 module main(); 5 6 reg enable, clk; 7 wire trigger; 8 9 //Testbench code here 10 initial begin 11 $monitor ("TIME : %g CLK : %b ENABLE : %b TRIGGER : %b", $time, clk,enable,trigger); 12 $dumpfile("main.vcd"); 13 $dumpvars(0, edge_u0); 14 clk = 0; 15 enable = 0; 16 #5 enable = 1; 17 #1 enable = 0; 18 #10 enable = 1; 19 #1 enable = 0; 20 #10 $finish; 21 end 22 23 always #1 clk = ~clk; 24 25 edge_wait_example edge_u0(enable, clk, trigger); 26 27 endmodule

等Enable 發出之後等待 5個clk rising edge,out = H

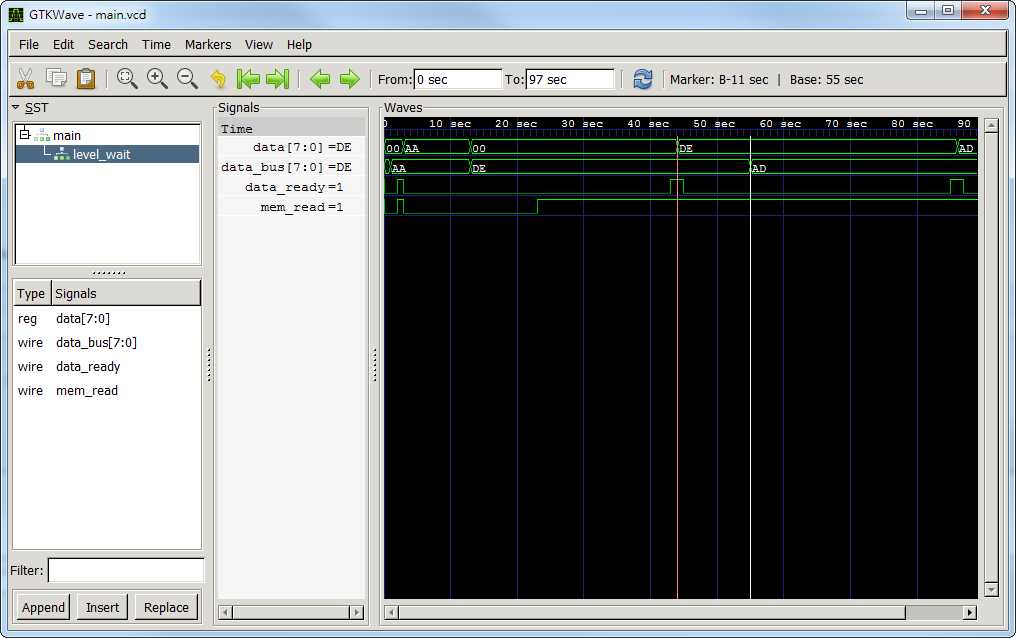

Level wait : 行為是等待level的條件成立,則等待設定時間之後update data 數值

level wait verilog code

1 module wait_example(mem_read, data_ready, data_bus, data); 2 3 input mem_read, data_ready; 4 input[7:0] data_bus; 5 output[7:0] data; 6 7 wire[7:0] data_bus; 8 reg[7:0] data; 9 10 11 always @ (mem_read or data_bus or data_ready) 12 begin 13 data = 8‘h0; 14 while (mem_read == 1‘b1) begin 15 // #1 is very important to avoid infinite loop 16 wait (data_ready == 1) #1 data = data_bus; 17 end 18 end 19 20 endmodule

level wait tb

1 `include "level wait.v" 2 module main; 3 4 reg mem_read, data_ready; 5 reg[7:0] data_bus; 6 wire[7:0] data; 7 8 // Testbench Code here 9 initial begin 10 $monitor ("TIME = %g READ = %b READY = %b DATA = %b", $time, mem_read, data_ready, data); 11 $dumpfile("main.vcd"); 12 $dumpvars(0, level_wait); 13 data_bus = 0; 14 mem_read = 0; 15 data_ready = 0; 16 #1 data_bus = 8‘haa; 17 #1 mem_read = 1; data_ready = 1; 18 #1 mem_read = 0; data_ready = 0; 19 #10 data_bus = 8‘hDE; 20 #10 mem_read = 1; 21 #20 data_ready = 1; 22 #1 mem_read = 1; 23 #1 data_ready = 0; 24 #10 data_bus = 8‘hAD; 25 #10 mem_read = 1; 26 #20 data_ready = 1; 27 #1 mem_read = 1; 28 #1 data_ready = 0; 29 #10 $finish; 30 end 31 32 wait_example level_wait(mem_read, data_ready, data_bus, data); 33 34 endmodule

mem_read = H且data_ready = H,則delay 自己設定的時間update data。

以上是关于(筆記) Edge wait & Level wait (verilog)的主要内容,如果未能解决你的问题,请参考以下文章