(筆記) verilog & simulation

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了(筆記) verilog & simulation相关的知识,希望对你有一定的参考价值。

第一次寫verilog對語法還有些陌生,不過基礎的東西還是要走一遍才會印象深刻。

以4bit counter為題目,首先開始想一個counter是由什麼來組成。

1. clock

2. reset

3. 4bit register

1 module counter( 2 clk, 3 rst, 4 count 5 ); 6 7 input clk; 8 input rst; 9 output [4:0] count; 10 reg[4:0] out; 11 12 assign count = out; 13 14 15 always@(posedge clk or posedge rst)begin 16 17 if(rst == 1) 18 out <= 0; 19 else if(out == 4‘hF) 20 out <= 0; 21 else 22 out <= out + 1; 23 24 end 25 26 endmodule

假設以後有超過1個以上的module需要simulation,所以我的test bench取名為main。

1 `timescale 1ns/100ps 2 `define CYCLE 20 3 4 module main; 5 6 reg clk; 7 reg rst; 8 wire[4:0] count; 9 always #(`CYCLE / 2) clk = ~clk; 10 11 initial begin 12 13 $dumpfile("main.vcd"); 14 $dumpvars(0, mode1); 15 $monitor("clk = %d", clk); 16 #0 clk = 0; 17 #1 rst = 1; 18 #30 rst = 0; 19 20 #1000 $finish; 21 22 end 23 24 counter mode1(clk, rst, count); 25 endmodule

`timescale 1ns/100ps `define CYCLE 20

test bench第1, 2行

timescale顧名思義就是定義時間的刻度,則1ns代表一個delay的單位,100ps是代表在simulation時,是waveform最細的單位。

define感覺用法跟C/C++雷同。

不過我花最多的時間的地方應該是要如何把counter module 裡面的count接出來。

在module內必須先定義一個4bits register來計算counter值,最後在assign給count輸出。

而test bench內要把4bit 的data接出來必須使用同樣大小的wire接出來。

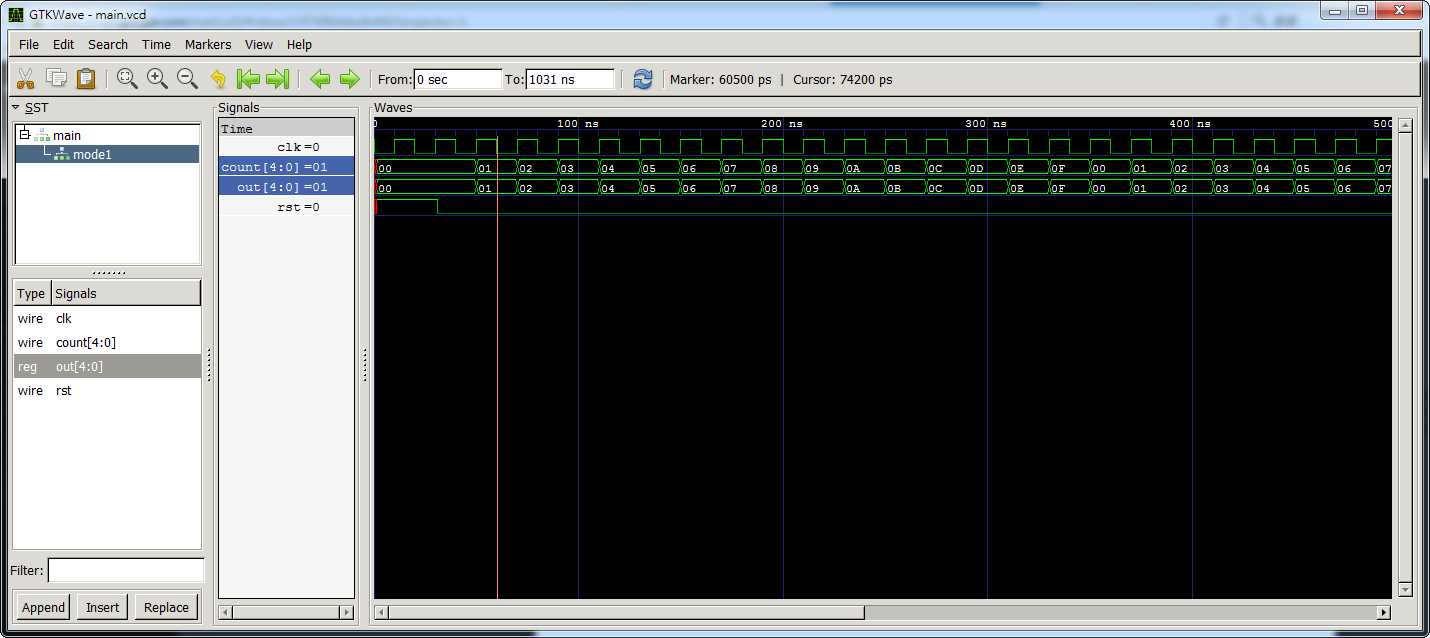

以下是模擬結果。

以上是关于(筆記) verilog & simulation的主要内容,如果未能解决你的问题,请参考以下文章