fpga的引脚如何配置 请问FPGA的引脚如何配置

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了fpga的引脚如何配置 请问FPGA的引脚如何配置相关的知识,希望对你有一定的参考价值。

FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。【FPGA工作原理】

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。FPGA的基本特点主要有:

1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5) FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。当需要修改FPGA功能时,只需换一片EPROM即可。这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。因此,FPGA的使用非常灵活。

【FPGA配置模式】

FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

如何实现快速的时序收敛、降低功耗和成本、优化时钟管理并降低FPGA与PCB并行设计的复杂性等问题,一直是采用FPGA的系统设计工程师需要考虑的关键问题。如今,随着FPGA向更高密度、更大容量、更低功耗和集成更多IP的方向发展,系统设计工程师在从这些优异性能获益的同时,不得不面对由于FPGA前所未有的性能和能力水平而带来的新的设计挑战。

例如,领先FPGA厂商Xilinx最近推出的Virtex-5系列采用65nm工艺,可提供高达33万个逻辑单元、1,200个I/O和大量硬IP块。超大容量和密度使复杂的布线变得更加不可预测,由此带来更严重的时序收敛问题。此外,针对不同应用而集成的更多数量的逻辑功能、DSP、嵌入式处理和接口模块,也让时钟管理和电压分配问题变得更加困难。

幸运地是,FPGA厂商、EDA工具供应商正在通力合作解决65nm FPGA独特的设计挑战。不久以前,Synplicity与Xilinx宣布成立超大容量时序收敛联合工作小组,旨在最大程度帮助地系统设计工程师以更快、更高效的方式应用65nm FPGA器件。设计软件供应商Magma推出的综合工具Blast FPGA能帮助建立优化的布局,加快时序的收敛。

最近FPGA的配置方式已经多元化!

【FPGA主要生产厂商介绍】1、Altera2、Xilinx3、Actel4、Lattice其中Altera和Xilinx主要生产一般用途FPGA,其主要产品采用RAM工艺。Actel主要提供非易失性FPGA,产品主要基于反熔丝工艺和FLASH工艺。 参考技术A 一一回答,从简单到复杂。

首先说IO

standard:这个是用于支持对应不同的电平标准。FPGA

IO口的电压由IO

bank上的VCC引入。一个bank上引入3.3V

TTL电平,那么此时整个bank上输出3.3V的TTL电平。设置这个第一是为了和current

strength一起计算功率。第二个是用于在IO口上加载正确的上拉/下拉电阻。只要你设置完成,Quartus会按照你的电平标准自动布线。

第二是IO

Bank:你在quartus

pin

planner

的top

view下右键然后点击

show

IO

banks,这个时候就会看到FPGA的管脚被几种颜色划分开了。一种颜色下的IO口代表一组bank。你在吧管脚的location约束完成以后。IO

Bank会自动填充完毕的。

第三是Group:Group就是你所输出的信号的名字啦。比如你有一组信号叫cnt。你对cnt的某一根赋值,那么。。这里的Group会自动填充为cnt

。

第四是Reserved:这个是对管脚内部的IO逻辑进行约束的,你在下面可以看到一些值。介绍几个吧。bidrectional:双向,tri-state:三态等等。这个约束的是FPGA在IO端的输入输出区域的逻辑。比如你选择tri-state。那么这个时候,在你IO口前部的IO区,quartus会自动给你生成一个三态门。

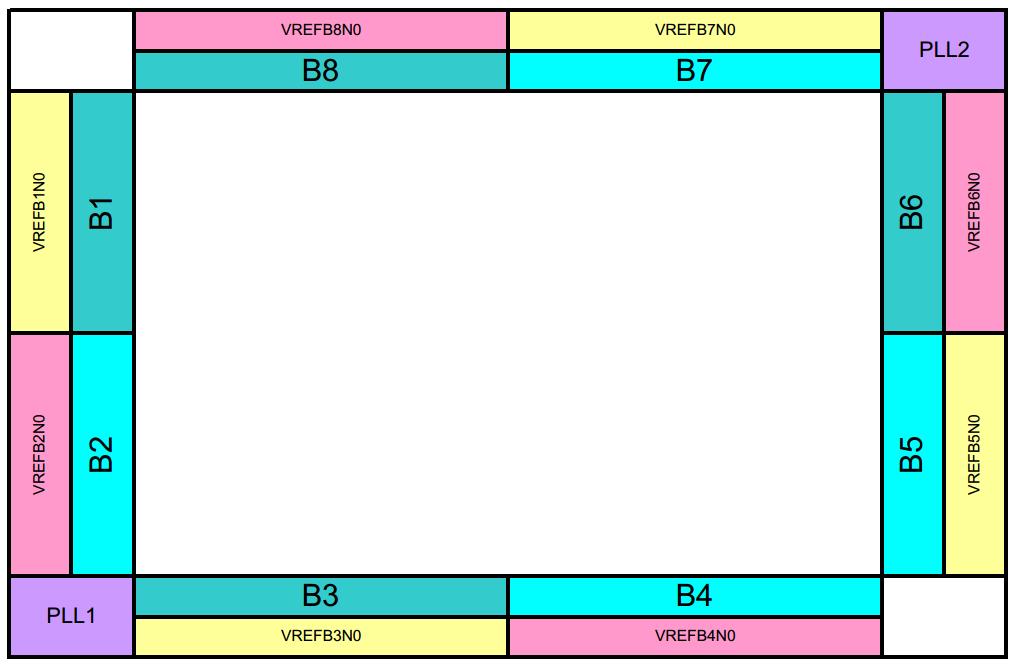

第五个是Vref

Group:这个Group是bank内部的细分区域,因为一个bank可能多达60个脚。为了快速定位,你可以利用这个vref

group来找到某个管脚。(这个是非修改属性)无法修改。

你的理解是正确的,另外,跨越IO

bank的信号没有问题。只是注意跨bank的电平是否一致即可。对于跨IO

bank的延迟对于FPGA而言没有多少延迟。

管脚分配呢,你可以看一下quartus里面pin

planner内部那张

top

view对于每个管脚的说明。大多数管脚是可以当做普通IO使用的。只是有些特殊要求的时候。只可以使用对应的IO,比如差分输入,高时钟输入等等。这个是要参照对应器件的IO

手册来决定的。而且对应的设计大多数的器件生产商都会给出参考设计。里面包括了IO的设计,pcb的设计以及内部程序端口的约束。所以具体问题具体分析。

FPGA引脚简介

一、 FPGA的硬件结构

这里说的硬件结构主要从FPGA的引脚功能方面描述,FPGA内部的电路逻辑暂不讨论。

FPGA的引脚大致可以分为三类:功能引脚、IO引脚、电源和接地引脚。

1. 功能引脚

FPGA的功能引脚包含了FPGA配置程序加载、FPGA配置模式选择、状态及错误提示、JTAG调试等等。

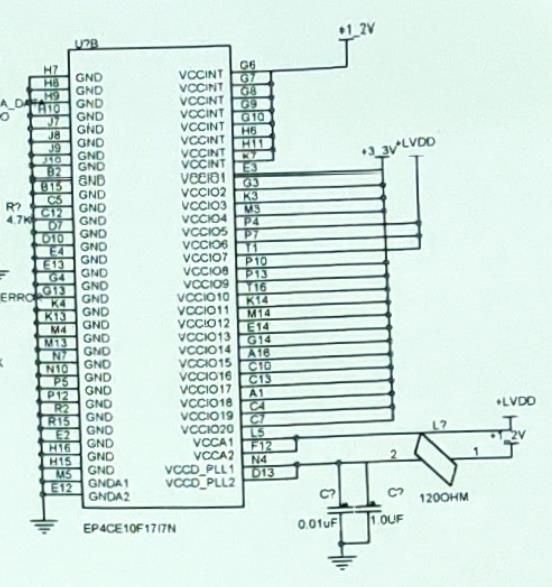

DCLK、DATA0、NCONFIG、CONF_DONE这几个引脚是配置FPGA所必须的,DATA1~DATA7可以用作其他功能,INIT_DONE可以不使用。TDI、TDO、TMS、TCK四个脚是JTAG调试使用,一般会预留。

2. IO引脚

FPGA的IO引脚是芯片与外部电路的接口部分,完成在不同电气特性下对输入/输出信号的驱动与匹配要求。FPGA的IO引脚按组分类,每组都能够独立地支持不同的IO标准。通过软件的灵活配置,可适配不同的电气标准与IO物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。为了便于管理和适应多种电器标准,FPGA的IO引脚被划分为若干个Bank,每个BANK的接口标准由其接口电压VCCIO决定。

一个BANK只能有一种VCCIO,但不同的BANK的VCCIO可以不同,只有相同电气标准的端口才能接到一起。

3. FPGA的电源和接地引脚

电源引脚为不同的电气需求提供不同的电压,包括VCCINT、VCCIO、VCCA、VCCD_PLL等。不同的BANK可以使用不同的IO电压,也可以连在一起使用相同的IO电压。接地引脚可以全部连在一起接到GND上。

二、FPGA的配置方式

1. 配置方案

FPGA有以下几种配置方案:

主动串行(AS)

主动并行(AP)

被动串行(PS)

快速被动串行(FPP)

JTAG模式

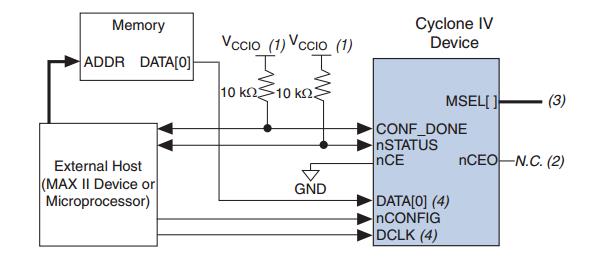

硬件上通过连接MSEL四个引脚的组合方式来选择使用哪种模式,主流方案使用的是被动串行配置(PS)方案。

2. 使用PS方式配置FPGA

在 PS 配置方案中,可以使用微处理器控制从存储器件 (例如闪存)传输配置数据到目标 Cyclone IV 器件。可以将配置数据存储

为 .rbf、 .hex 或 .ttf 的格式。

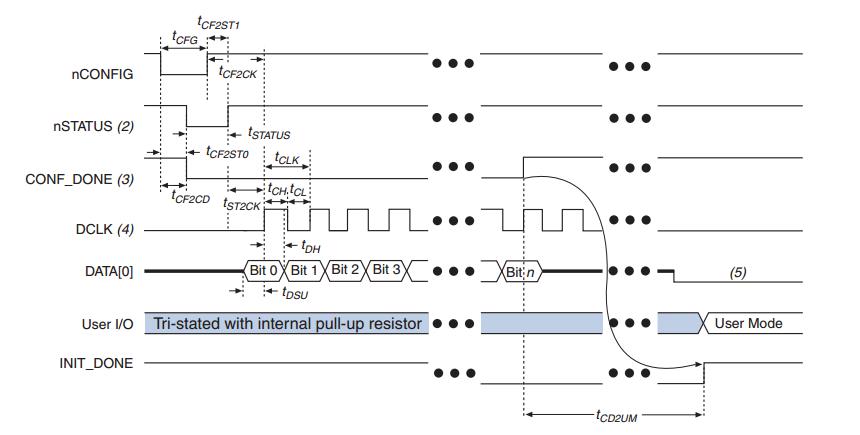

(1)当其nCONFIG引脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态引脚nSTATUS和CONFIG_DONE引脚也将输出为低。

(2)当FPGA的nCONFIG引脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。随之,芯片将释放漏极开路输出的nSTATUS引脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。

(3)FPGA在 DATA[0] 上接收配置数据,在 DCLK 上接收时钟。在 DCLK 的上升沿,数据被锁存到器件中。数据不断送入目标器件,直到 CONF_DONE 变高以及器件进入初始化状态。

(4)主控必须一次一个位地将配置数据放置在 DATA[0] 上。如果使用的配置数据格式为 .rbf、 .ttf 或 .hex,必须首先发送每个数据字节的 LSB。例如,如果 .rbf 包含的字节序列为 02 1B EE 01 FA,那么必须发送到器件的串行比特流是 : 0100-0000 1101-1000 0111-0111 1000-0000 0101-1111

(5)当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。

(6)CONF_DONE引脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

(7)INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该引脚。这个引脚不是必须使用的,很多FPGA方案中没有使用这个引脚。

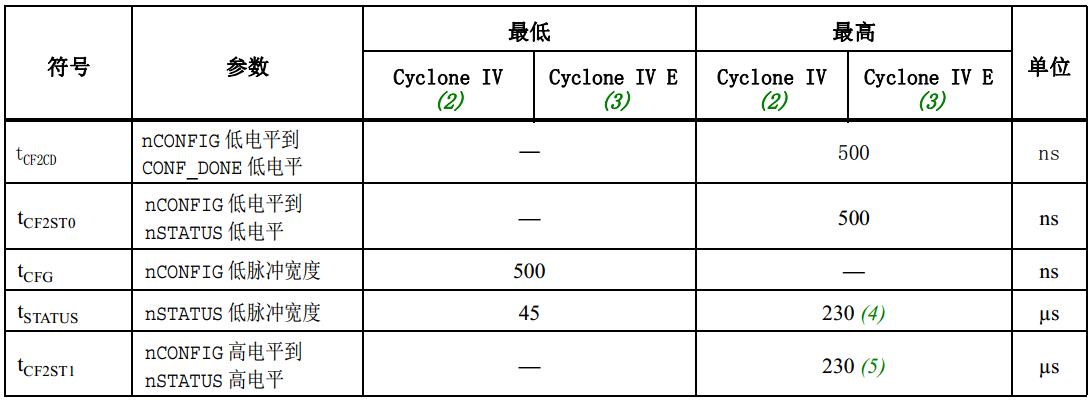

3. FPGA时序参数

三、FPGA和外界数据通讯接口

FPGA除了对IO引脚进行控制外,还可以和外界数据进行通讯。

1. GPCM模式

FPGA通常挂载在类似Nand控制器这样的总线上,比如VxWorks的Local Bus。类似Nand有8个数据脚,FPGA内部会配置出8个或者16个地址/数据脚来收发数据。整个通讯过程和读写Nand类似,当读写的地址区间在到FPGA映射的内存地址范围时,片选会自动识别到是FPGA的数据。

2. SPI接口

也可以定义几个引脚挂载在SPI总线上,只要时序能对应上就行。

以上两种是常见的与外界进行数据通讯的方法。由于FPGA的IO引脚使用非常灵活,也可以根据实际情况自己定义通迅接口和通讯协议。

以上是关于fpga的引脚如何配置 请问FPGA的引脚如何配置的主要内容,如果未能解决你的问题,请参考以下文章