UVM序列篇之二:sequence和item(上)

Posted 那些城市那些年

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了UVM序列篇之二:sequence和item(上)相关的知识,希望对你有一定的参考价值。

无论是自驾item,穿过sequencer交通站,通往终点driver,还是坐上sequence的大巴,一路沿途观光,最终跟随导游停靠到风景点driver,在介绍如何驾驶item和sequence,遵守什么交规,最终可以有序地穿过sequencer抵达driver之前,读者又必要首先认识sequence与item之间的关系。这里的sequence值的是类uvm_sequence,而item指的是uvm_sequence_item,为了文章的简洁,我们称之为sequence和item。对于激励的生成和场景控制,是由sequence来编织的,而对于激励所需要的具体数据和控制要求,则是从item中的成员数据得来的。

Sequence Item

在上一节《新手上路》中,我们已经提出item是基于uvm_object,这表明了它具备UVM核心基类所必要的数据操作方法,例如copy、clone、compare、record等,这里我们不再做赘述。读者需要了解到的是,通常对于一个item,应该有什么用途的数据成员被定义在item中呢?我们可以将它们划分下如下几类:

- 控制类。譬如总线协议上的读写类型、数据长度、传送模式等。

- 负载类。一般即数据总线上的数据包。

- 配置类。这往往是用来控制driver的驱动行为,例如命令driver的发送间隔或者有无错误插入。

- 调试类。用来标记一些额外的信息,用来方便调试,例如该对象的实例序号、创建时间、被driver解析的时间始末等。

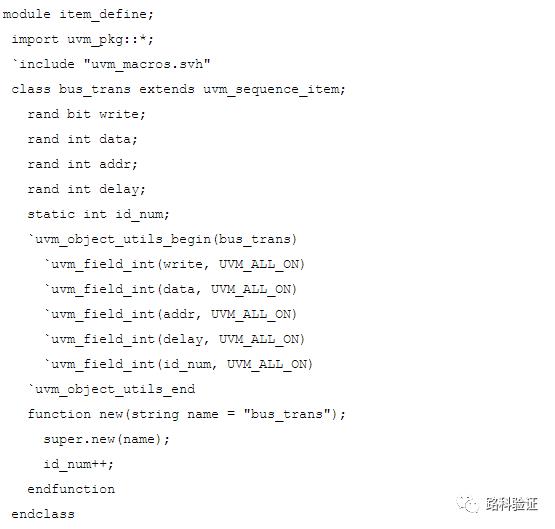

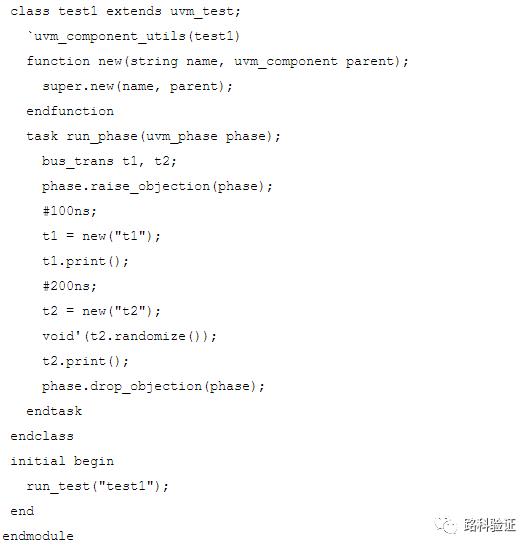

下面的例码是一段item的定义,从这段代码中读者可以看到上面提到的各种用途的数据使用情况:

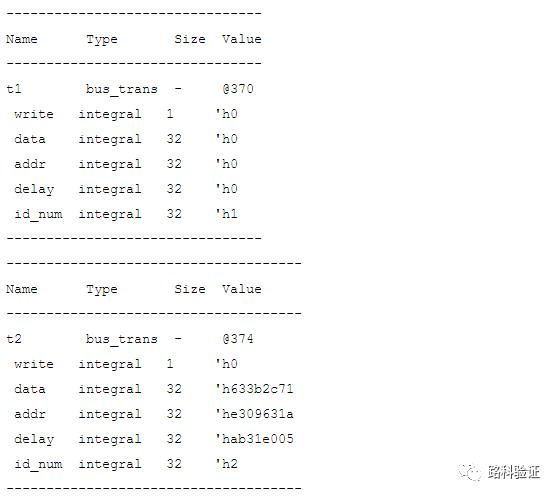

输出结果:

上面的这段代码中,不但给出了一个较为典型的item定义,同时也伴有一些item使用时的特点:

-

如果数据域属于将来需要用来做驱动,那么用户应考虑定义为rand类型,同时按照驱动协议给出合适的constraint。

-

由于item本身的数据属性,为了充分利用UVM域声明的特性,我们建议将必要的数据成员都通过`uvm_field_xxx宏来声明,以便日后的基本函数操作,例如上面的print()函数。

-

读者也注意到了一点,上面的例子中,t1没有随机化而t2随机化了,这种差别在item通往sequencer之前是很明显的。因为UVM要求item的创建和随机化都应该发生在sequence的body()任务中,而不是在sequencer或者driver中。

-

如果按照item对象的生命周期来区分,它的生命应该开始于sequence中的创建,而后经历了随机化和穿越sequencer最终到达driver,直到被driver消化之后,它的生命周期一般来讲才算寿终正寝。之所以要突出这一点,是因为一些用户在实际中,会不恰当地直接操作item对象,直接修改其中的数据,或者将它的句柄发送给其它组件使用,这就无形中修改了item的基因,或者延长了一个item对象的寿命。这种不合适的对象操作方式是用户需要注意的,可以取代的方式则是合理利用copy和clone等方法。

接下来我们需要理清item和sequence,以及sequence群落之间的关系。从简而言,一个sequence包含了一些有序组织起来的item实例,考虑到item在创建后需要被随机化,sequence在声明时也需要预留一些可供外部随机化的变量,这些随机变量一部分是用来通过层级传递来控制item对象中的变量的,一部分也是用来对item对象之间加以组织和时序控制的。为了加以区分几种常见的sequence定义方式,我们在介绍后续的sequence之前,首先将sequence可以分类为:

-

扁平类(flat sequence)。这一类中往往只用来组织更细小的粒度,即item示例的组织。

-

层次类(hierarchical sequence)。这一类则是由更高层的sequence用来组织底层的sequence,进而让这些sequence或者按照顺序的方式,或者按照并行的方式,挂载到同一个sequencer上。

-

虚拟类(virtual sequence)。这一类则是最终控制整个测试场景的方式,鉴于整个环境中往往存在不同种类的sequencer和其对应的sequence,我们需要一个虚拟的sequence来协调顶层的测试场景。之所以称这个方式为virtual sequence,是因为该序列本省并不固定挂载于某一种sequencer类型上,而是它会将其内部的各种不同类型的sequence最终挂载到不同的目标sequencer上面。这也是最大的不同于hierarchical sequence的一点。

我们本文接下来将主要介绍flat sequence和hierarchical sequence,而virtual sequence将保留至本章的最后一节《层次化》中重点为大家阐述virtual sequence和virtual sequencer的典型用法。

谢谢你对路科验证的关注,也欢迎你分享和转发真正的技术价值,你的支持是我们保持前行的动力。

以上是关于UVM序列篇之二:sequence和item(上)的主要内容,如果未能解决你的问题,请参考以下文章

从零开始学习 UVM6.4UVM 激励产生 —— uvm_do 宏详解