UVM中seq.start()和default_sequence执行顺序

Posted 谷公子的备忘录

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了UVM中seq.start()和default_sequence执行顺序相关的知识,希望对你有一定的参考价值。

1. 问题

假如用以下两种方式启动sequence,方法1用sequence的start()方法启动seq1,方法2用UVM的default_sequence机制启动seq2。那么seq1和seq2谁会先启动呢?

// Method1: using build-in start() method of sequence

task run_phase(uvm_phase phase);

super.run_phase(phase);

seq1.start(vsqr);

endtask : run_phase

// Method2: using default sequence

uvm_config_db#(uvm_sequence_base)::set(this,”agent.seqr.run_phase”,”default_sequence”, seq2);答案:seq2会先启动。也就是说进入run_phase之后,会先执行seq2的body()内容,等退出seq2之后,再执行seq1的body()内容,串行执行的。

2. 原理

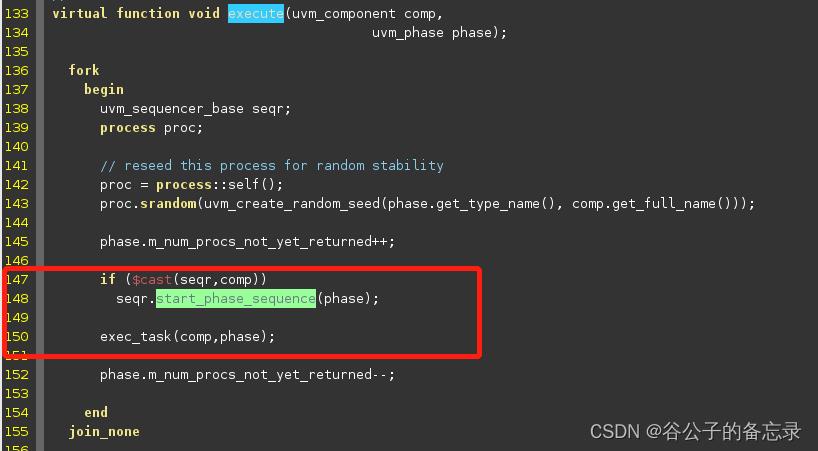

可以打开UVM-1.1d源码下src/base/uvm_task_phase.svh文件。为方便分析,我截图如下。在uvm_task_phase类里execute(xxx)函数的第148行和150行确定了seq1和seq2的执行顺序了。148行会执行default sequence (seq2),150行会执行run_phase()的内容,也就是这时候才会启动seq1.start(vsqr)。

2.1 seqr.start_phase_sequence(phase)解析

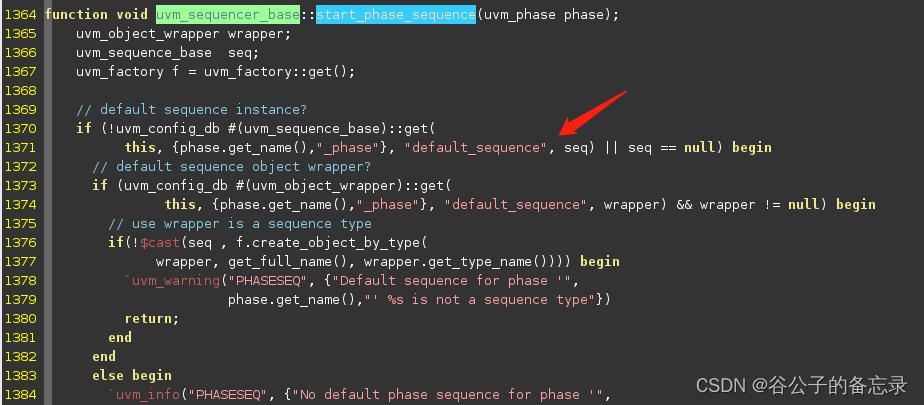

start_phase_sequence(xxx)是定义在uvm_sequencer_base类里的,具体看src/seq/uvm_sequencer_base.svh文件。示意截图如下:

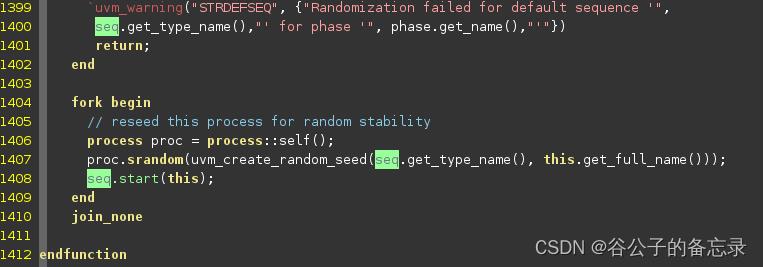

在start_phase_sequence(xxx)函数里会先使用uvm_config_db获取到default sequence,然后在最后会调用seq.start(this)启动它。这就完成了UVM default sequence的启动机制了。

2.2 exec_task(comp,phase)解析

exec_task(xxx)原型在uvm_phase.svh文件里,也就是在uvm_phase类里定义了。之后每个从uvm_phase扩展出来的uvm_common_phase类型和uvm_runtime_phase类型的phase都会override它,在里面添加各自的功能。各自举个例子吧。

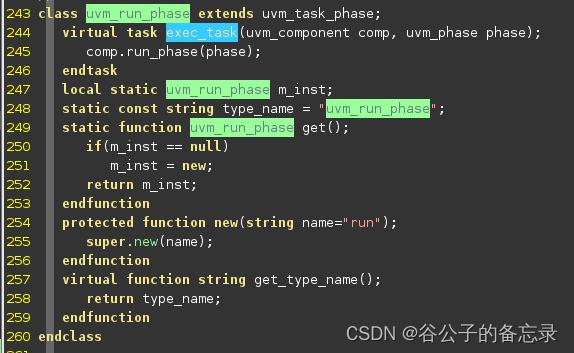

对于uvm_common_phase类型里的uvm_run_phase类,它在exec_task(xxx)里会调用对应uvm_component(comp)的run_phase()方法。文件路径: src/base/uvm_common_phase.svh,截图如下:

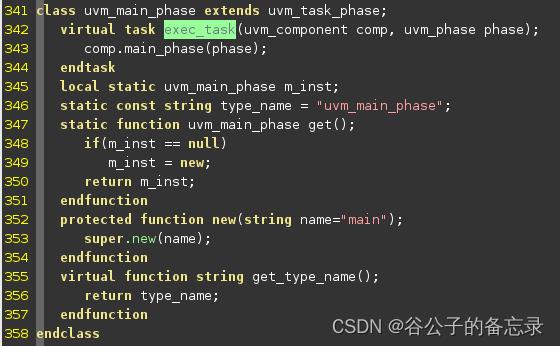

对于uvm_runtime_phase类型里的uvm_main_phase类,它在exec_task(xxx)里会调用也会调用对应uvm_component(comp)的run_phase()方法。文件路径: src/base/uvm_runtime_phase.svh,截图如下:

3. 结论

所以大家结合2.1和2.2小节的解析,就可以知道了,用default sequence启动的方式是会优先于对应phase里其它方式启动sequence,也就是先被调用start(sqr)启动起来。

UVM1.1 和 UVM1.2的不同

参考技术A参考官网

UVM_REG动态地址索引

UVM-1.2时,uvm_reg_block::lock_model()是必备的一步,它用来检查和缓存地址映射,但是一旦lock后,无法再对map做二次修改。

问题在于目前的SoC子系统有动态映射,或者重新映射的功能,因此如果在仿真中UVM寄存器模型只有静态地址映射,那么就无法很好地支持这一点。

UVM-1800.2中,我们可以调用uvm_reg_block::unlock_model先来“解锁”,再uvm_reg_block::unregister()来卸载寄存器,完成这些动作以后,只需要重复添加寄存器的动作,再lock寄存器块就好了。

例如,想在仿真过程中,先建立modelA的地址映射关系,然后在仿真过程中重新建立地址映射。在UVM-1800.2中,我们可以在仿真过程中(不一定是build阶段),unlock_model()和unregister(),接下来再为uvm_reg_block建立新的uvm_reg_map并将其添加和lock_model()。

uvm_event_callback并入uvm_callback

UVM-1.2时,uvm_event_callback虽然也是callback类,但和uvm_callback是分割的,所以在将它添加到uvm_event时,其添加方法与添加其它uvm_callback对象的方式是不同的。

UVM-1800.2中,这一切得到了统一,uvm_event_callback也变为了uvm_callback类,也由此,添加uvm_event_callback对象的方法就变为了添加uvm_callback对象的方法。

sequence的宏得到简化

UVM-1.2时,`uvm_do()和其众多变种让UVM新人无所适从,对于测试用例的阅读也不那么友好。

UVM-1800.2中,只需要`uvm_do()就足够了,因为用户可以为其添加其它参数(如果不使用缺省参数的话)。

以上是关于UVM中seq.start()和default_sequence执行顺序的主要内容,如果未能解决你的问题,请参考以下文章