(数字IC)低功耗设计入门

Posted IC_learner

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了(数字IC)低功耗设计入门相关的知识,希望对你有一定的参考价值。

低功耗设计这个专题整理了好久,有一个月了,有图有证据:

然而最近一直有些烦心事、郁闷事,拖延了一下,虽然现在还是有点烦,但是还是先发表了吧。下面我们就来聊聊低功耗设计吧,由于文章比较长,因此我就不一次性发完,我整理之后再发上去。当然,这里的低功耗设计基本上是入门阶段,也就是大部分从理论角度进行阐述,你也可以说是从书本上说的,但是呢,我可以先给大家剧透一下:不仅仅是从理论上说,我还结合EDA工具进行说明如何进行低功耗设计。废话不多说,下面就来看看这个专题的主要内容:

·低功耗设计的目的

·功耗的构成/类型

·功耗分析与流程——使用EDA工具

·低功耗设计与优化

一、低功耗设计的目的

1.便携性设备等需求

电子产品在我们生活中扮演了极其重要的作用,便携性的电子设备便是其中一种。便携性设备需要电池供电、需要消耗电池的能量。在同等电能提供下,低功耗设计的产品就能够工作更长的时间。时间的就是生命,因此低功耗设计是很重要的。便携性的设备需要低功耗设备,比如说手机,如果充电两小时,通话5分钟,这谁还买你的手机...

2.可靠性与性能的影响

设备消耗电能,会产生热量;消耗的能量越多,产生的热量越多。发热越严重,热噪声越大,就会影响器件的正常工作,导致电路不能正常工作。发热量的增加,可能会使工作在1G下的电路,只能工作在500M,这就影响了速度,这最常见的就是手机的发热了,手机发热之后,便感觉卡卡的。

3.成本的影响

如果不注意进行低功耗设计,那就可能导致后期的成本增加,从而导致整个系统的成本增加。例如,不进行低功耗设计,发热量就可能增加,在封装的时候,就需要考虑怎么给你这个芯片进行散热,从而增加了封装的散热成本。再比如,在进行系统组装的时候,如果那你的芯片功耗过大,就需要考虑在系统外给你进行散热,比如说添加一个风扇,发热很严重的甚至可以给你进行液体降温。这样子就在系统组装上面增加了组装成本。因此在设计初始进行低功耗设计是很重要的。

······

当然,除了上面那三点之外,还有许多要进行低功耗设计原因,这里列出三点,主要是为了说明低功耗设计是以后的数字IC发展趋势之一,我们要注重低功耗设计。

二、功耗的构成/类型

本小节主要一方面介绍一下功耗的构成,一方面介绍一下工艺库中的功耗模型。功耗的构成可以从两个角度来描述,一个是从功耗种类方面,另一个是从系统结构方面。我们在设计过程中,讨论比较多的往往是从功耗角度方面;工艺库中的功耗模型主要是结合工艺库来对功耗种类进行一些具体的、补充式的讲解。下面我们就来看看功耗的工程吧。

1.功耗的构成——按类型分

低功耗按照类型分类呢,其构成主要有动态功耗、静态功耗、浪涌功耗这三种。在这第一小点我主要做一些简要的介绍,在后面的第三小点我将结合工艺库进行介绍。

(1)动态功耗

动态功耗包括:开关功耗或者称为翻转功耗、短路功耗或者称为内部功耗。

①开关功耗

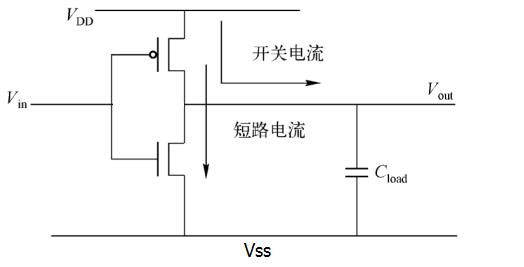

在数字CMOS电路中,对负载电容进行充放电时消耗的功耗,比如对于下面的CMOS非门中:

当Vin = 0时,上面的PMOS导通,下面的NMOS截止;VDD对负载电容Cload进行充电,充电完成后,Vout的电平为高电平。

当Vin = 1时,上面的PMOS截止,下面的NMOS导通,负载电容通过NMOS进行放电,放电完成后,Vout的电平为低电平。

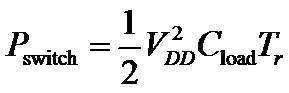

这样一开一闭的变化,电源的充放电,就形成了开关功耗,开关功耗Psitch的计算公式如下所示:

在上式中,VDD为供电电压,Cload为后级电路等效的电容负载大小,Tr为输入信号的翻转率(关于翻转率,我们在后面第三小点会进行介绍)。

一般情况下,信号在一个周期内平均翻转两次,即上升沿一次、下降沿一次,也就是说,Tr = 2f,因此,平均功耗就是:

Pdynamic = Vdd*Vdd*CL*f

我们不必追究这个公式怎么得来,我知道这个功耗在这么计算就可以了,有兴趣的话,也可以深入探讨。

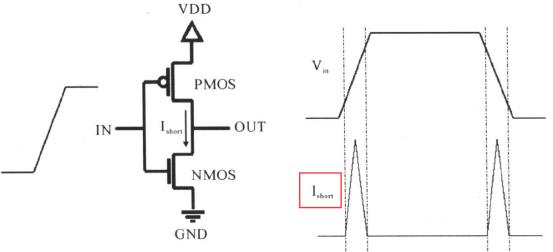

②短路功耗

短路功耗也称为内部功耗,短路功耗是因为在输入信号进行翻转时,信号的翻转不可能瞬时完成,因此PMOS和NMOS不可能总是一个截止另外一个导通,总有那么一段时间是使PMOS和NMOS同时导通,那么从电源VDD到地VSS之间就有了通路,就形成了短路电流,如下面的反相器电路图所示:

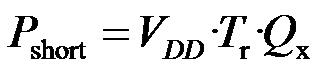

短路功耗Pshort的计算公式如下所示:

上式中,Vdd为供电电压,Tr为翻转率,Qx为一次翻转过程中从电源流到地的电荷量。

由此我们可以找到,动态功耗主要有开关功耗和短路功耗;其中开关功耗在动态功耗中占大部分比例;从上面的两个式子中我们可以看到,动态功耗主要跟电源的供电电压、翻转率、负载电容有关。

(2)静态功耗

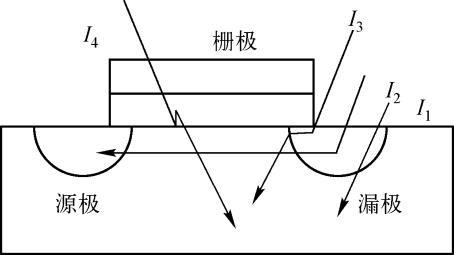

在CMOS电路中,静态功耗主要是漏电流引起的功耗,如下图所示:

漏电流有下面几个部分组成:

·PN结反向电流I1(PN-junction Reverse Current)

·源极和漏极之间的亚阈值漏电流I2(Sub-threshold Current)

·栅极漏电流,包括栅极和漏极之间的感应漏电流I3(Gate Induced Drain Leakage)

·栅极和衬底之间的隧道漏电流I4(Gate Tunneling)

一般情况下,漏电流主要是指栅极泄漏电流和亚阈值电流(进入超深亚微米工艺之后,隧道漏电流成为主要电流之一),因此下面就简单介绍一下这两种电流。

栅极泄漏功耗:在栅极上加信号后(即栅压),从栅到衬底之间存在电容,因此在栅衬之间就会存在有电流,由此就会存在功耗。

亚阈值电流:使栅极电压低于导通阈值,仍会产生从FET漏极到源极的泄漏电流。此电流称为亚阈值泄漏电流。在较狭窄的晶体管中,漏极和源极距离较近的情况下会产生亚阈值泄漏电流。晶体管越窄,泄漏电流越大。要降低亚阈值电流,可以使用高阈值的器件,还可以通过衬底偏置进行增加阈值电压,这些属于低功耗设计,我们在后面的低功耗设计中会进行讲解。

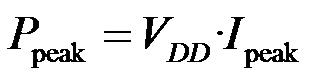

静态功耗的计算公式如下所示,Ileak为泄漏电流(Ipeak应该是Ileak):

静态功耗往往与工艺有关,我们在第三小节中将进一步进行讨论。

(3)浪涌功耗

浪涌功耗是浪涌电流引起的功耗。浪涌电流是指开机或者唤醒的时候,器件流过的最大电流,因此浪涌电流也称为启动电流。一般情况下,浪涌功耗不是我们关注的地方,因此这里只是说明有这个功耗存在。

2.功耗的构成——按结构分

前面按照类型进行功耗分类,这里使用结构进行分类,也就是根据设备的结构或者设备的构成进行分类。(以SoC为例)主要分为:时钟树功耗、处理器功耗、存储器功耗、其他逻辑和IP核功耗、输入输出pad功耗。在不同的应用、设备中,这些功耗的比例不一样,但是时钟树、处理器、存储器占了绝大部分功耗,这是需要说明的。

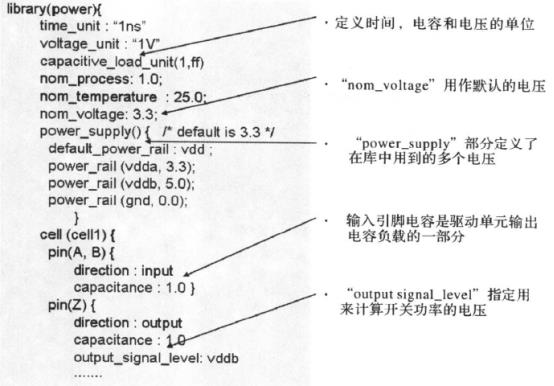

3.工艺库中的功耗模型

前面介绍了功耗的构成,在这一小点中,将结合工艺库进行阐述功耗(的构成),同时结合工艺库举例说明功耗的计算。

(1)工艺库中的功耗信息与计算

①开关功耗计算与相关库信息

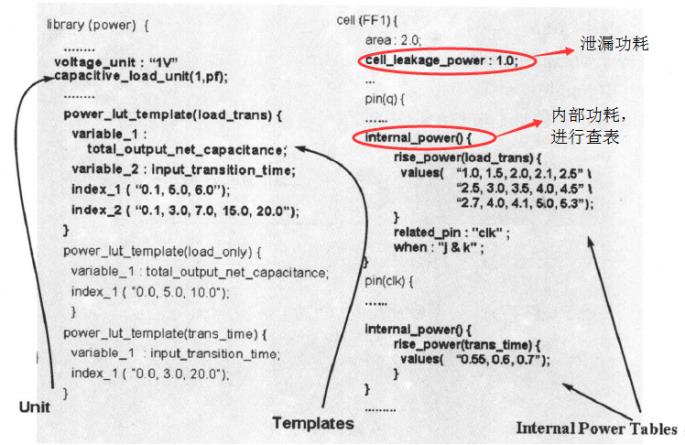

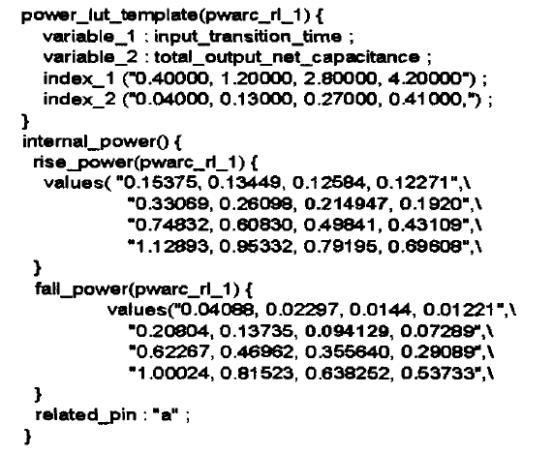

我们从前面知道,开关功耗主要就是对输出电容的充放电引起的,工艺库中有开关功耗有关的信息,如下所示:

开关功耗可以用开关能量和翻转率来表示:P=E·Tr=C·v^2·T2,即开关能量E=CV^2。翻转率我们后面会进行说明,至于放在后面介绍翻转率,一个是即介绍即用,另外一个就是帮大家功耗的组成。

②内部功耗/短路功耗与相关库信息

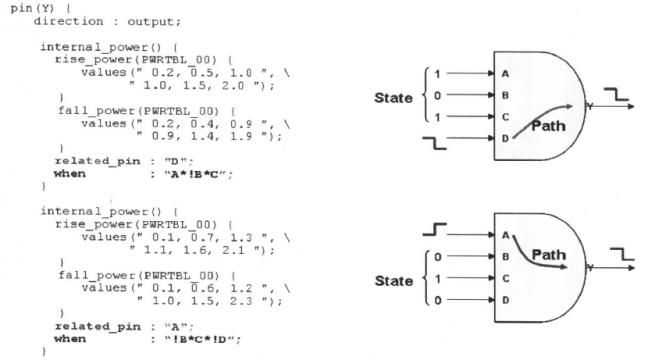

内部功耗前面我们也介绍了一些,这里再啰嗦一下,短路功耗/内部功耗是单元(比如说反相器单元)的输入从0到1或者从1到0的转换过程中,单元内部P管和N管同时导通那个瞬间的功耗,这不是因为单元损坏而产生的短路功耗 。工艺库中包含了单元的短路功耗,短路功耗由特性描述工具预先处理,存放在工艺库的功耗查找表里。也就是说,我们可以通过工艺库中内部功耗的相关参数,从而得到内部功耗。工艺库中内部功耗信息如下所示:

单元的内部功耗与其转换时间和输出电容负载有关,根据输入转换时间和输出电容的大小,在工艺库中进行查表,得到上升功耗和下降功耗,然后再根据下面的公式进行计算得到总的内部功耗:

Pi=(上升功耗+下降功耗)·0.5·Tr

需要补充一下,工艺库中比较精确的功耗模型,功耗与状态有关,与路径也有关,即state dependent path dependent,SDPD。

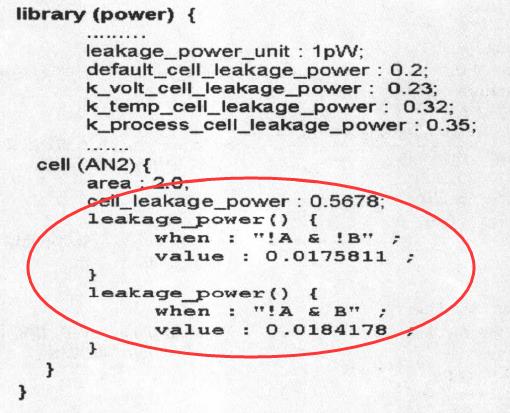

③静态功耗/漏电功耗与相关库信息

静态功耗/漏电功耗也是由特性工具预先处理,存放在工艺库里面。工艺库中的静态功耗信息如下所示:

静态功耗跟单元的状态有关,也就是输入(或者说单元)在不同的状态下,对于的功耗不一样,通过状态进行查表,就可以得到相应的静态功耗了。

(2)计算举例

①翻转率

前面我们一直说翻转率,那么翻转率到底是什么呢?这里我们就来给大家介绍一下。

翻转率(Toggle rate,Tr):单位时间内信号(包括时钟、数据等等信号)的翻转次数。如下图所示:

信号在40ns时间内跳转了4次,翻转率为:Tr = 4/4ns = 0.1GHz

②动态功耗计算举例

从前面中我们知道,在计算动态功耗的时候,我们才用到翻转率。其中开关功耗的表达式为:

内部功耗的表达式为:

Pi=(上升功耗+下降功耗)·0.5·Tr

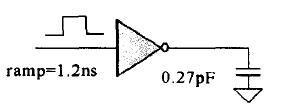

现在我们使用翻转率和工艺库的功耗信息来计算一下电路的动态功耗,电路如下图所示:

工艺库信息如下所示:

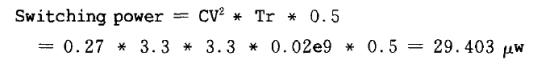

·动态功耗中的开关功耗计算:

根据公式,我们可以直接计算出开关功耗为:29.403uw

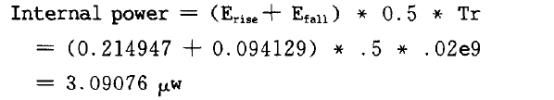

·动态功耗中的短路功耗/内部功耗:

Pi=(上升功耗+下降功耗)·0.5·Tr

根据公式,我们先要查找工艺库得到上升(沿)功耗和下降(沿)功耗。输入转换时间为1.20000,输出电容负载为0.270000,因此对于的上升功耗和下降功耗分别为:0.214947和0.094129。因此总的内部功耗为:

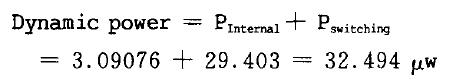

·于是得到总的动态功耗为:

③其他事项

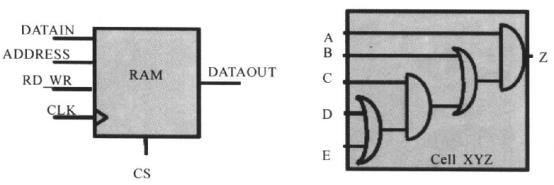

·单元的功耗可能与状态和路径有关,下图中:

左图是RAM单元,在读状态和写状态时,功率是不同的。此外,单元的功耗在不同的操作模式下也有不同的值。

右图表示了输入到输出的不同路径,路径不一样,功耗也是不一样的。

·工艺库有状态和路径不同时的功耗描述,即SDPD描述,如下图所示:

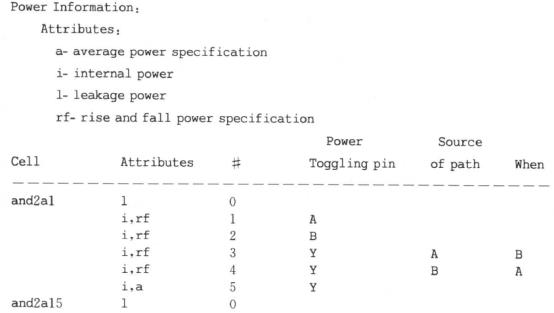

我们也可以在EDA工具中使用report_lib slow -power 命令列出库中的功耗信息:

第一讲先整理到这里。

以上是关于(数字IC)低功耗设计入门的主要内容,如果未能解决你的问题,请参考以下文章

(数字IC)低功耗设计入门——物理级低功耗设计&to be continued?

数字后端低功耗 - 多种低功耗技术及其在IC后端布局中的应用

收录近500篇文章|学习路线|基础知识|接口|总线|脚本语言|芯片求职|安全|EDA|工具|低功耗设计|Verilog|低功耗|STA|设计|验证|FPGA|架构|AMBA|书籍|