VHDL顶层原理图里输出信号仿真时出现Node missing source是啥意思?好像是输出信号里的定义有点问题

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VHDL顶层原理图里输出信号仿真时出现Node missing source是啥意思?好像是输出信号里的定义有点问题相关的知识,希望对你有一定的参考价值。

那该怎么解决呢

参考技术AVHDL:一种硬件描述语言,可以在不同设计层次上描述硬件电路

仿真:一种对描述进行验证的方法,也称逻辑模拟

原理图:一种用图形来描述电路结构的方法,原理图中包含有电路所用元件和元件之间的连线等信息 参考技术B 失踪源节点本回答被提问者采纳

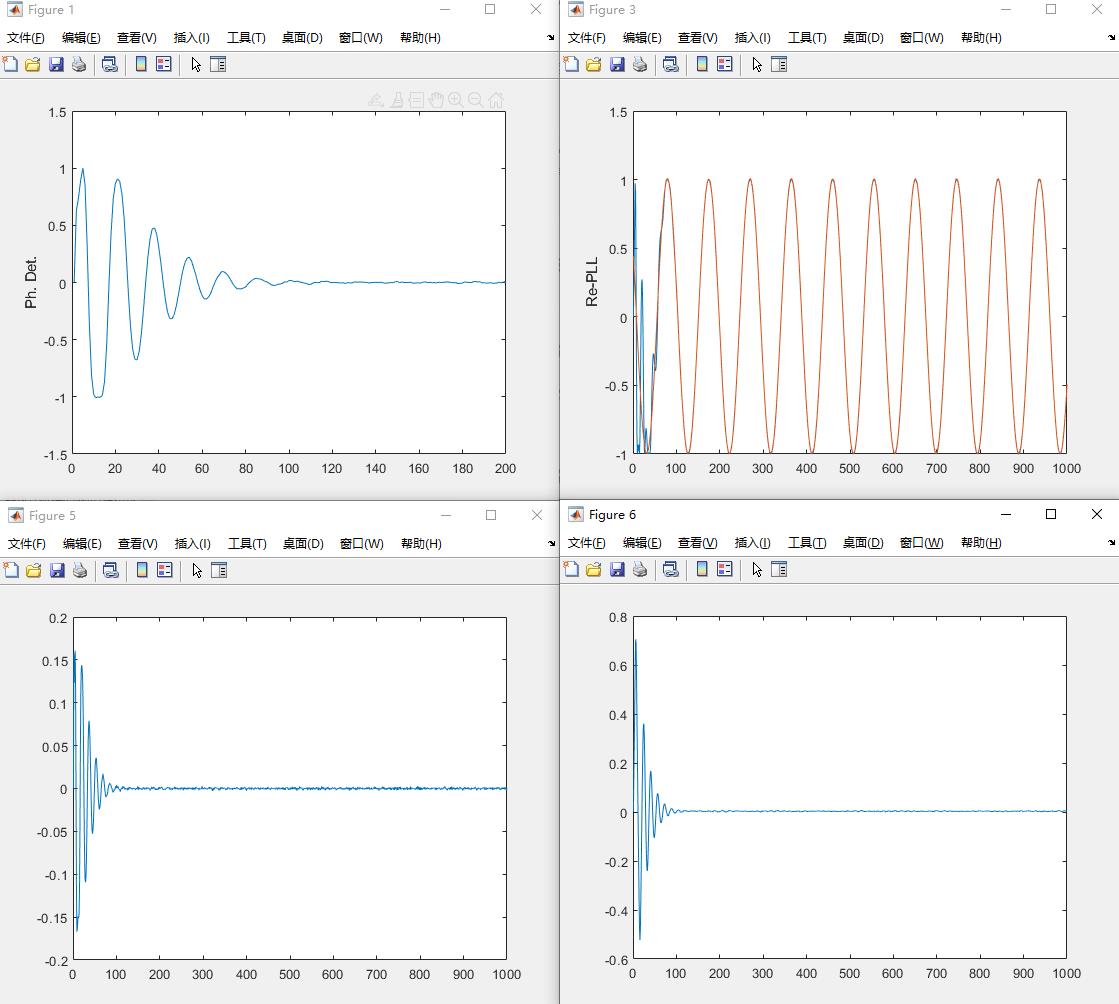

数字锁相环的matlab仿真

1.简介与仿真结论

2.理论分析

全数字锁相环路的工作原理:环路的输入信号通常为时间上连续的信号,如单频正弦波、模拟调频信号或移频键控信号等。环路的输出信号,即数字控制振荡器的输出信号为周期性脉冲序列,其周期可调且受数字滤波器输出信号的控制。输入信号和数控振荡器的输出信号加到抽样相位检测器的输入端。在检测器中,由数控振荡器的输出脉冲序列对输入信号抽样,检测出脉冲序列与输入信号之间的相位差,并变换成数字信号作为检测器的输出信号。该信号经数字滤波器滤波后作为数控振荡器的控制信号,改变数控振荡器的周期,实现对相差的校正。

与模拟锁相环路比较,全数字锁相环路有如下特点:

(1)全部采用数字电路。由于数字电路中的有源器件工作于导通和截止两种工作状态,受干扰的影响比模拟电路小,使工作的可靠性提高。另外,数字电路易于集成化。

(2)在数字锁相环路中,时钟源通常不直接受控,不同于模拟锁相环路中的压控振荡器直接受误差信号的控制,这将有利于提高环路的性能。应用数字锁相环路,在一定范围内可以消除类似于模拟锁相环路中压控振荡器特性的非线性、环路滤波器传输函数的不稳定等的影响,从而改善锁相环路的性能。全数字锁相环已成为全数字相干通信、跟踪接收机和频率综合器中的核心部件,日益获得更广泛的应用。

3.部分核心代码

% PLL illustration

clear all;

close all;

% define initial phase offset and incoming Cw frequency and Sampling frequency

theta = pi/3;

f=1000;

fs=100000;

% Create the real and imaginary parts of a Cw non-modulated Carrier to be tracked.

k=1:1:1000;

delf=f/20;

Signal=exp(j*(2*pi*k*(f+delf)/fs+theta))+0.01*(rand(1,1000)+j*rand(1,1000));

% initilize PLL Loop

phi_hat(1)=30;

e(1)=0;

phd_output(1)=0;

nco(1)=0

% define Loop filter parameters

kp=0.15; % Proportional constant

ki=0.1; % Integrator constant

% PLL implementation

for n=2:length(Signal)

nco(n)=conj(exp(j*(2*pi*n*f/fs+phi_hat(n-1)))); % Compute nCO

phd_output(n)=imag(Signal(n)*nco(n)); % Complex multiply nCO x input

e(n)=e(n-1)+(kp+ki)*phd_output(n)-ki*phd_output(n-1); % Filter integrator

some(n)=(kp+ki)*phd_output(n)-ki*phd_output(n-1);

phi_hat(n)=phi_hat(n-1)+e(n); % update nCO

end;

% plot waveforms

index_stop=200;

figure;

plot(1:index_stop, phd_output(1:index_stop)),ylabel('Ph. Det.');

figure;

plot(1:index_stop, phi_hat(1:index_stop)*180/pi,'m'),ylabel('Est. Phs.');

index_stop=1000;

% subplot(211)

figure;

plot(1:index_stop, real(nco(1:index_stop)),1:index_stop,real(Signal(1:index_stop))),ylabel('Re-PLL');

% subplot(212)

figure;

plot(1:index_stop, imag(nco(1:index_stop)),1:index_stop,imag(Signal(1:index_stop))),ylabel('Im-PLL');

figure;

plot(1:index_stop,some(1:index_stop));

figure;

plot(1:index_stop,e(1:index_stop));

A01-15

以上是关于VHDL顶层原理图里输出信号仿真时出现Node missing source是啥意思?好像是输出信号里的定义有点问题的主要内容,如果未能解决你的问题,请参考以下文章

1.用modelsim-altera 6.5e仿真的时候 显示 no data 2.signaltap ii 选择signal clock时出现错误