SDRAM操作原理分析

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了SDRAM操作原理分析相关的知识,希望对你有一定的参考价值。

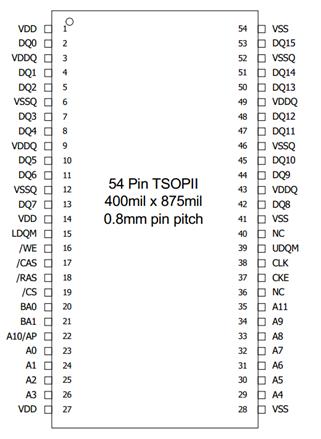

芯片原理图

引脚原理图

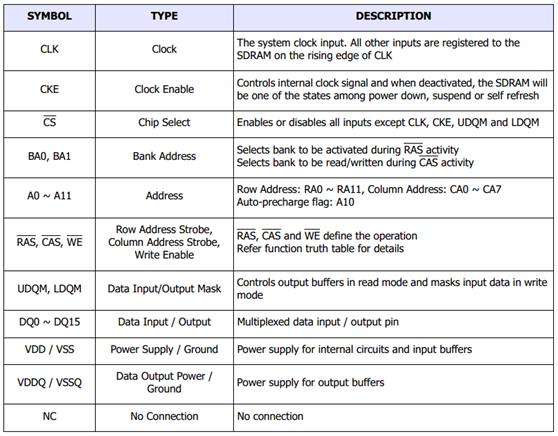

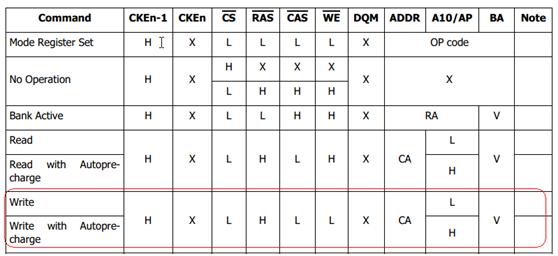

指令

????通过对上面指令的总结,简化出要用到的指令如下:

指令 | 常量名 | CKE | CSn | RAS | CASn | WEn | 备注 |

空操作 | NOP | 1 | 0 | 1 | 1 | 1 | ? |

行激活 | ACTIVE | 1 | 0 | 0 | 1 | 1 | ? |

读操作 | READ | 1 | 0 | 1 | 0 | 1 | ? |

写操作 | WRITE | 1 | 0 | 1 | 0 | 0 | ? |

预充电 | PR | 1 | 0 | 0 | 1 | 0 | ? |

自刷新 | AR | 1 | 0 | 0 | 0 | 1 | ? |

设置寄存器 | LMR | 1 | 0 | 0 | 0 | 0 | ? |

突发停止 | BURST_STOP | 1 | 0 | 1 | 1 | 0 | 1 |

?

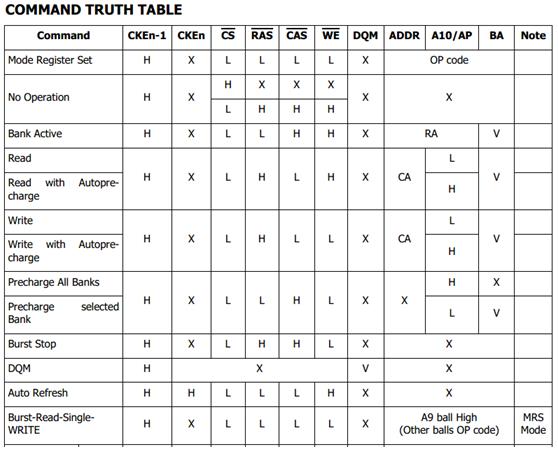

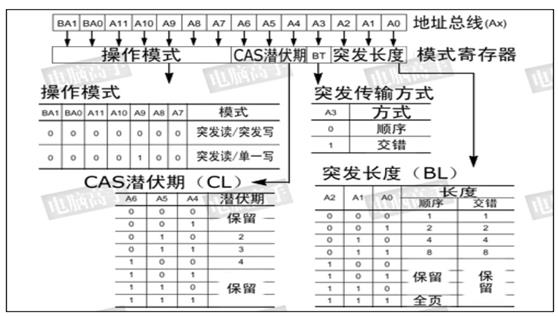

芯片配置

操作模式:SDRAM内部有三种操作模式:单一的读写、突发读写、页读写(突发读写全页)

突发传输模式:一般情况下都采用顺序读写操作;

CAS潜伏期:即发出读指令之后,经过多少个时钟周期才可以读取数据,而在写数据中是没有这个概念的。

突发长度:突发就是连续读写的操作,如果没有突发操作,对SDRAM内部连续地址进行读写则要发送指令和地址,然后读取或写入数据,循环操作,有了突发操作后,就可以制定突发长度,发送读写的起始地址然后对SDRAM进行连续的读写,突发的长度可以设置,突发全页就是连续操作一行,就是256个存储单元。

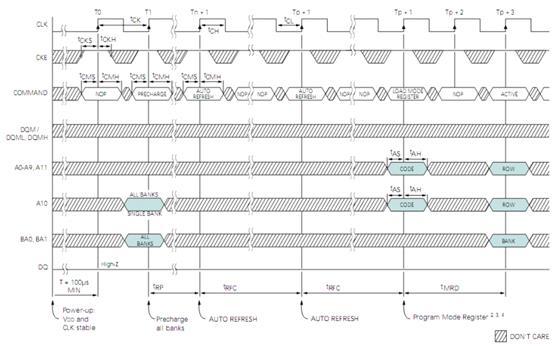

初始化时序图

初始化操作过程如下:

- 上电等待200us

- 发送PR命令

- 满足tRP时间要求至少20ns

- 发送AR(AutoRefresh)命令

- 满足tRFC(tRPC又名tRCC)时间要求至少63ns

- 发送AR(AutoRefresh)命令

- 满足tRFC(tRPC又名tRCC)时间要求至少63ns

- 发送LMR(LodeModeRegister)命令和相关配置信息

- 满足tMRD 时间要求至少1个时钟

?

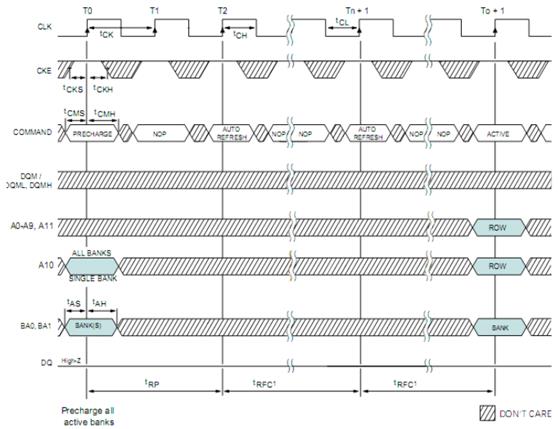

定时自动刷新

存储体中电容的数据有效保存期上限是64ms,也就是说每一行刷新的循环周期是64ms。这样刷新速度就是:行数量/64ms 。我们在看内存规格时,经常会看到4096 Refresh Cycles/64ms 或8192 Refresh Cycles/64ms的标识,这里的4096与8192就代表这个芯片中每个L-Bank的行数。刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096行时为15.625 μs,8192行时就为7.8125 μs。

刷新操作分为两种:Auto Refresh,简称AR与Self Refresh,简称SR。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。对于AR,SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者说CAS 在RAS 之前有效。所以,AR又称CBR(CAS Before RAS,列提前于行定位)式刷新。由于刷新涉及到所有L-Bank,因此在刷新过程中,所有L-Bank都停止工作,而每次刷新所占用的时间为9个时钟周期(PC133 标准),之后就可进入正常的工作状态,也就是说在这9个时钟期间内,所有工作指令只能等待而无法执行。64ms之后则再次对同一行进行刷新,如此周而复始进行循环刷新。显然,刷新操作肯定会对SDRAM 的性能造成影响,但这是没办法的事情,也是DRAM 相对于SRAM (静态内存,无需刷新仍能保留数据)取得成本优势的同时所付出的代价。

操作过程如下:

- 先发送Precharge命令,命SDRAM释放所有资源库。

- 相关操作需要消耗时间tRP-20ns。

- 发送AutoRefresh命令,命SDRAM刷新内部逻辑的内容。

- 相关操作需要消耗时间tRFC-63ns、

- 发送AutoRefresh命令,命SDRAM刷新内部逻辑的内容。

- 相关操作需要消耗时间tRFC-63ns。

写操作

????SDRAM的写操作有两种模式,如下

Write with Autopre-charge:每当一次性的写发生以后,SDRAM自动释放相关的资源库,以方便下一次的写操作。相反则需要手动进行释放,一般采用Write with Autopre-charge。

两者的区别就是A10的电平高低。

操作过程如下:

- 发送Active命令,发送库(Bank)和行(Row)地址信息。

- 满足tRCD时间要求,至少20ns。

- 发送Write命令、库(Bank)和列(Column)地址;A10拉高代表With Auto Precharge;

- 同时写入的一字数据。这时候DQM必须拉低。

- 满足tWR(tDPL)时间要求,至少2个时钟。

- 满足tRP时间要求,至少20ns。

经过时间tWR(tDPL)以后,一字数据就成功被写入。随后SDRAM开始执行Auto Precharge的操作,释放当前相关的资源库。最后经过tRP以后(Auto Precharge的操作完成)。

?

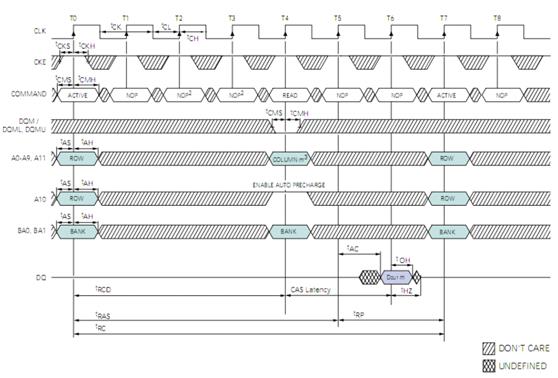

读操作

- 发送Active命令、行(Row)和库(Bank)地址。

- 满足时间要求tRCD-20ns。

- 发送Read命令、列(Column)和库(Bank)地址,DQM拉低,拉高A10一个时钟,表示读操作后自动释放资源库(WithAutoPrecharge)。

- 满足CAS Latency时间要求

- CAS Latency满足之后,接下来满足时间要求tAC-6ns、tRP-20ns,然后读取数据。

以上是关于SDRAM操作原理分析的主要内容,如果未能解决你的问题,请参考以下文章