NI PXIe-5644R矢量信号收发器硬件架构

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了NI PXIe-5644R矢量信号收发器硬件架构相关的知识,希望对你有一定的参考价值。

http://xilinx.eetrend.com/article/7471

随着NI PXIe-5644R向量信号收发器(VST)的诞生,NI通过将用户可编程FPGA的灵活性引入RF仪器中,重塑了仪器的概念。

1. 高性能与革命性的设计

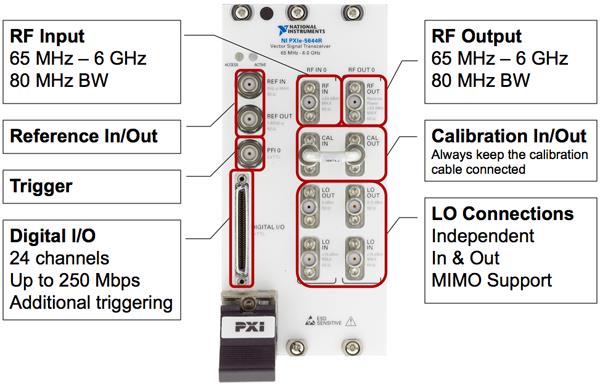

NI PXIe-5644R VST在用于现场可编程门阵列(FPGA)中,将矢量信号分析仪(VSA)和矢量信号发生器(VSG)中典型的RF I/O功能与NI或用户定义用于实现信号处理和控制的功能结合在一起。RF输入和RF输出包含独立的本地振荡器(LO)、65 MHz至6 GHz的频率范围以及高达80 MHz的瞬时带宽。NI PXIe-5644R属于单个3槽PXI Express模块(见图1)。通过在单个PXI Express机箱中使用多个VST模块可以创建多输入多输出(MIMO)配置。

图1:NI PXIe-5644R硬件前面板

NI PXIe-5644R最引人注目的特性是什么?毫无疑问,当然是如此小的尺寸却所能实现非常高的性能。通过利用高级校准和宽带数字校正,NI PXIe-5644R VST可以凭借其难以置信的小尺寸满足研发级仪器的性能需求。用户可编程FPGA所提供的更加快速的测试时间和灵活性,使NI PXIe-5644R更适合RF的表征、验证和确认以及产品测试。

除了高性能和小尺寸的特点,NI PXIe-5644R VST最为革命性的特征是采用了用户可编程的Xilinx Virtex-6 FPGA,支持使用LabVIEW FPGA模块进行编程。该FPGA连接至VSA和VSG基带I/Q数据与24条数据速率高达250 Mbit/s的数字I/O线。 RF技术、高速数字I/O技术与FPGA技术的有力结合,使得NI PXIe-5644R有能力处理如实时在测设备(DUT)控制、自定义触发、功率电平伺服、软件定义无线电和通道仿真等诸多应用。

2. FPGA 基卡架构

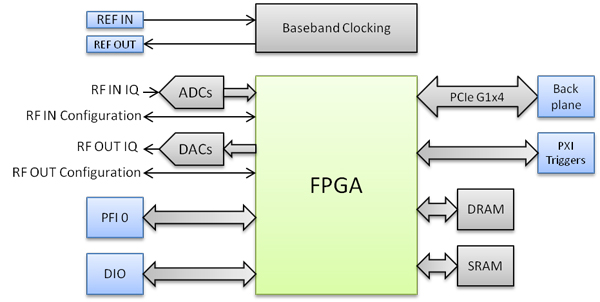

NI PXIe-5644R FPGA基卡包括Xilinx Virtex-6 FPGA、基带时钟电路、模数转换器(ADC)、数模转换器(DAC)、功能可编程的数字I/O线(PFI 0)、数字I/O连接器、PCI Express接口、PXI触发器、DRAM和SRAM。

图2:NI PXIe-5644R FPGA基卡框图

Xilinx Virtex-6 FPGA

NI PXIe-5644R包含一块用于系统配置、数字数据移动和数字信号处理的Xilinx Virtex-6 LX195T FPGA。该FPGA与ADC、DAC、PCI Express总线、DRAM、SRAM、PFI 0、数字I/O和PXI触发器直接连接,允许通过自定义编程满足各种类型应用的要求。

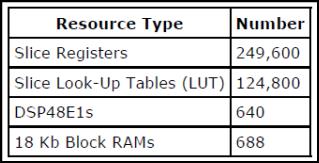

可重配置的FPGA资源

Xilinx Virtex-6 LX195T FPGA 包含以下资源。

支持LabVIEW FPGA编程

NI PXIe-5644R的Xilinx FPGA完全支持使用LabVIEW FPGA模块进行编程。由于LabVIEW可方便地表示并行和数据流,使其十分适用于FPGA编程。因此对于传统FPGA设计的新老用户,都可以有效地利用可重配置硬件的功能。

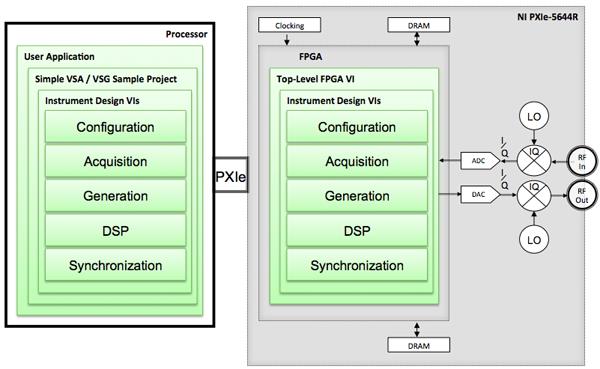

NI提供了用于NI PXIe-5644R的LabVIEW范例项目和仪器设计VI,可帮助用户快速设计和执行首次测量。仪器设计VI可允许用户修改FPGA和处理器层次(如PC和实时操作系统)的LabVIEW代码并按功能类型进行分类,如配置、采集、生成、数字信号处理(DSP)和同步(如图3所示)。如需了解更多关于NI PXIe-5644R VST软件的详细信息,可查看VST软件架构白皮书或者观看VST网络视频。

图3:与NI PXIe-5644R硬件对应的LabVIEW范例项目和仪器设计VI

基带时钟

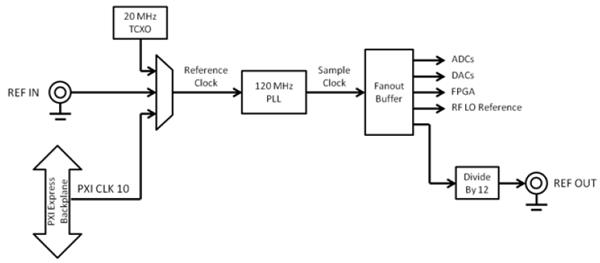

NI PXIe-5644R在FPGA内包含多个时钟。主时钟为可用于ADC、DAC和相关FPGA逻辑的采样时钟。

采样时钟

采样时钟频率为120 MHz,并且由锁相环(PLL)导出。可以选择将内部TCXO、NI 5644R REF IN前面板连接器或PXI_CLK 10作为PLL的参考信号。如图4所示,采样时钟同样可以作为RF IN和RF OUT内部LO电路的参考信号。虽然采样时钟频率固定为120 MHz,但通过FPGA内部的分数插值和分数抽取DSP VI可以实现高分辨率的I/Q数据速率。

图4:NI PXIe-5644R时钟架构

FPGA 时钟

下表列出了FPGA中的时钟。除该时钟以外,LabVIEW FPGA允许衍生用户定义频率的时钟。

ADCs 和 DACs

NI PXIe-5644R使用双通道16位ADC和DAC。ADC和DAC使用的时钟频率为120 MS/s,可提供80 MHz的复杂带宽并可自动与FPGA内部的采样时钟域进行同步。该方式有利于实现同一个时钟域中ADC和DAC的完全同步,从而启用接收和发送间的确定性延迟。RF IN和RF OUT IQ数据流处于FPGA的同一个时钟域。通过同步和确定性延迟,可使实时测试和嵌入式应用编程更加容易。

PFI 0

PFI 0是一个3.3 v LVTTL、双向的通用数字I/O口。PFI 0通常用于触发器输入或记号/事件输出。但由于PFI 0 I/O的缓存直接连接至FPGA,所以可以通过LabVIEW FPGA编程,对PFI 0的功能进行配置,以满足特殊的应用需求。

数字I/O

通过VHCDI端口可访问NI PXIe-5644R的数字I/O。总共包括24条双向LVTTL数字I/O线,每通道包含4线(总共6端口),并可对每个端口进行单独配置。数字I/O连接器也包含时钟输入和时钟输出线、以及可用于触发或额外双向数字I/O的PFI 1和PFI 2线。由于数字I/O的缓存直接连接至FPGA,所以可以通过LabVIEW FPGA编程,对单个数字I/O口的功能进行配置,以满足特殊的应用需求。

线缆和附件

NI提供多种可兼容数字I/O连接器的线缆和附件。注意该线缆和附件使用与NI PXIe-5644R数字I/O匹配的自定义引脚,并可保持50欧姆传输线环境。不建议使用其他VHDCI线缆。

DRAM 和 SRAM

NI PXIe-5644R包括两个DRAM块,每块为256 MB并可提供理论最大数据速率2.1 GB/s,通过FPGA可单独访问每个DRAM块。该DRAM块属于通用类型,但通常用于存储待生成的波形或者已采集的波形。

同时包含2 MB的板载SRAM,最大读取和写入数据速率分别为40 MB/s和36 MB/s。SRAM属于通用内存,通常用于存储多个硬件配置,该配置可以无需使用主机而直接从FPGA进行应用。

PCI Express 接口

NI PXIe-5644R包含一个一代的x4 PCI Express 接口,可用于DMA传输、可编程I/O以及点对点数据流。

3. 接收器架构

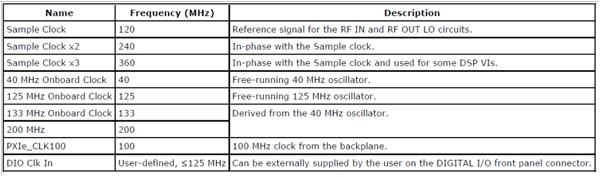

NI PXIe-5644R包括一个零差式RF接收器,也称为同步、零中频或直接下变频接收器。在零差式接收器中,输入RF信号将传递至混频器,该方式类似于传统外差式接收器,如NI PXIe-5665和NI PXIe-5663E VSA中的接收器。但与外差式接收器不同,零差式接收器中的LO频率等同于或接近于输入RF信号的频率,从而得到直流中心或低IF信号,如10或20 MHz。

输入信号将与基带混频并拆分为同相(I)和正交(Q)分量,其中载波为同相并分别偏移90度。然后I和Q路径信号将分别进行数字化并得到I和Q数据。最后软件会组合I和Q数据流并显示原始信号。图5显示了零差式或零中频架构的简要框图。

图5:零差式(零中频)架构基本框图

零差式(零中频)接收器优势

与传统外差式架构相比,零差式架构具有多方面优势,如简化设计、低成本、低功耗以及更多选择,并可用于分离信号重叠的邻近通道。其他优点包括更高带宽、通过单个LO简化设计、紧凑设计以提供更小封装尺寸等。以下部分将详细说明各个优势。

1. 带宽。带单个ADC的接收器存在信号带宽的实际上限,为时钟频率的40%。使用相同的采样时钟频率,由于零差式架构包括两个ADC,可允许双倍带宽即采样时钟频率的80%。通常情况下,使用可支持较低采样时钟频率的ADC可获得更好的无寄生动态范围(SFDR)和信噪比(SNR)性能。零差式接收器在不降低ADC性能的情况下可允许更宽的带宽,而对于只有单个ADC的接收器,在这种条件下会降低ADC性能。

2. 单本地振荡器(LO)。由于多通道测试系统在多输入多输出(MIMO)应用中变得越来越重要,使得共享LO成为必须要求。与传统外差式架构中使用多个LO相比,零差式架构中仅需共享单个LO而降低成本并大大降低系统配置的复杂程度。

3. 紧凑设计.与外差式架构相比,零差式架构使用更为简单的RF设计。更少的LO信号;无需庞大昂贵的RF和IF滤波器;零差式架构仅需更少转换阶段,从而使设计更为精简。

零差式(零中频)接收器面临的挑战

虽然零差式架构具有很多优势,但仍存在诸如无法实现包络检测等缺点。NI PXIe-5644R通过使用正交检测和数字信号处理可解决该问题。

直流偏移是零中频架构的另一个挑战。在ZIF结构中任何混合至0 Hz的信号都会引起直流的频谱分量,该失真存在于数据采集瞬时带宽的中部。由采集数据以及瞬时带宽各个频率偏移组成的频谱,将会在每个采集数据的中部显示该重复的直流偏移分量。通过在数字化的I和Q数据流中应用偏移可以实现直流偏移归零。每个LO频率必须应用单独的归零操作,当运行NI PXIe-5644R自校准过程时可以自动完成该操作。

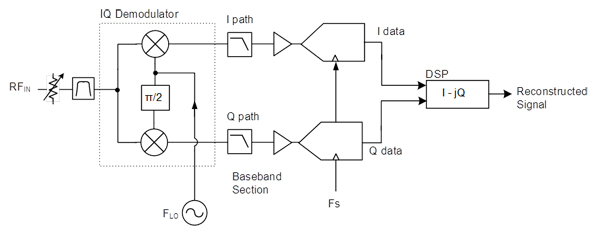

接收器信号路径

NI PXIe-5644R接收器设计的顶层架构如图6所示。该框图显示了校准合成器、可选高功率衰减器、可选低功率信号放大器、波段外选择滤波器、附加增益和衰减信号调理以及根据频率选择一个混频器(共三种)进行解调。

图6:NI PXIe-5644R接收器框图

选择滤波器组包含8条带低通或带通滤波器的不同路径。该滤波器可允许接收器过滤多余噪声,使得接收器只处理所需范围内的信号。在进行完所选滤波以及其他信号调理后,根据频率将会把RF信号发送至其中一个解调器(共三种)。每个解调器可用于指定波段,以便优化增益和相位。

接收器路径包含多个固态衰减器,可提供超过80 dB的衰减并支持1 dB步进变化。RF输入为AC耦合,三个可切换的增益放大器和一个前置放大器可用于扩展动态范围并改进噪声指数。

内部提供的低相位噪声LO(本地振荡器)可将多个下变频器连接至单个LO源。使用同一个LO源对于相位相干的信号采集应用十分有用,如多输入多输出(MIMO)系统。当使用该配置时,共享同一个LO的每个NI PXIe-5644R RF通道都将调整为相同的RF频率。

下变频的基带信号将被直接传输至NI PXIe-5644R的内部ADC通道。该ADC通道会按120 MS/s以及16位动态范围对基带模拟信号进行数字化,将结果传递至板载FPGA进行后续处理,最后传递至主机。

下变频器

NI PXIe-5644R接收器包括一个单级直接转换(I/Q)下变频器。RF信号将从配置的LO频率下变频至DC,其中基带信号可进行数字化以便后续处理。该架构在实现宽瞬时带宽的同时可确保高效的镜频抑制以及LO泄漏最小化。镜频抑制和LO泄漏性能可通过宽带正交校正实现,该接收器路径已经过优化,并可作为矢量信号分析仪用于宽带解调

低IF模式和带内重调

低IF接收器属于使用IQ解调器的另一种接收器类型,其框图与图5显示的零IF接收器相同。在零IF接收器中,LO频率位于调制信号的频率范围之内,而低IF接收器的LO频率位于调制信号范围之外。这将导致DC分量不再位于下变频区间内。将不会存在部分与DC相关的减损,如DC偏移、1/f噪声以及部分情况下的基带谐波。

以低IF模式操作NI PXIe-5644R可实现LO调制和数字频域移位这两个功能的组合。以数字移位频率从载波生成或采集所需信号可以避免直接转换结构中存在的LO泄漏问题。该方式的代价,低IF接收器的最大带宽是使用相同ADC采样率的零IF接收器的一半。NI PXIe-5644R可支持高达80 MHz的复杂瞬时带宽以及分配给数字频率修正的额外4 MHz复杂带宽。额外频率移位会导致可用80 MHz带宽减少为(80/2) - (x- 2) MHz,其中x表示请求的数字频率移位。

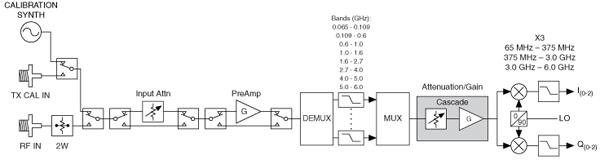

4. 发送器架构

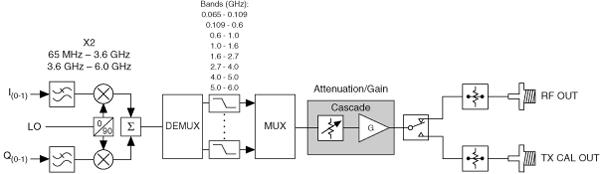

NI PXIe-5644R VST上的RF发送器架构包括2个调制器、1个滤波器组以及附加信号调理模块。其顶层框图如图7所示。

图7:NI PXIe-5644R发送器框图

发送器的信号路径

NI PXIe-5644R中的2个调制器与NI PXIe-5673E VSG中使用的调制器相同,根据不同的频率对其相位和增益平衡进行了优化。NI PXIe-5644R RF发送器的滤波器组与RF接收器中使用的滤波器组相同,同为8条带低通或带通滤波器的路径,如图7所示。

滤波之后的RF信号进入级联信号调理模块,该模块包括3个可编程衰减器、1个可选放大器和2个固定放大器。最后根据传输路径是否需要进行校准,将RF信号切换到RF输出或者是校准输出前面板连接器。

上变频器

NI PXIe-5644R RF发送器路径中包含1个可将基带信号从DC上变频为已配置的LO频率RF信号的单级直接转换 (I/Q) 上变频器。该架构在实现宽瞬时带宽的同时可确保高效的镜频抑制以及LO泄漏最小。镜频抑制和LO泄漏的高性能可通过宽带正交校正实现。该路径已进行优化,并可作为CW发生器或VSG宽带调制。

发送器路径包含4个固态衰减器,可提供超过100 dB的衰减并支持1 dB步进变化。当需要生成高功率信号时,将使用1个额外的可调增益放大器。

发送器路径内部提供的低相位噪声LO(本地振荡器)可将多个上变频器连接至单个LO源。对于MIMO系统来说,使用同一个LO源对于生成相位相干的信号十分有用。当使用该配置时,共享同一个LO的NI PXIe-5644R RF每个通道都将调整为相同的RF频率。

平均功率和波峰因素注意事项

波峰因素表示波峰信号功率和平均均方根(RMS)功率之间的功率变化。在CW模式中使用的正弦信号的波峰因素为3 dB,即表示正弦信号的平均RMS功率比波峰功率小3 dB。调制信号(尤其是OFDM)会存在更大的波峰因素,大约为10 dB至12 dB。

当配置为信号生成的设备时,同时考虑平均RMS功率和波峰因素就显得十分重要。NI PXIe-5644R可支持最大平均功率输出6 dBm以及高达12 dB的波峰因素。超出6 dBm平均功率后,该设备将无法确保被校准或保持线性。尤其需要注意当平均功率设置为超出6 dBm并且信号的波峰因素仍设置为大于等于12 dB时,将可能发生严重饱和或启用NI PXIe-5644R的逆功率保护电路。

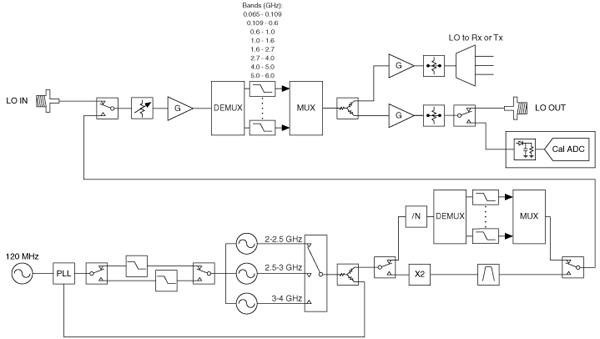

5. 合成器 本地振荡器(LO)架构

NI PXIe-5644R的频率范围为65 MHz至6 GHz,并可提供小于1 Hz的调整精度。该调制精度包含了LO步长大小和FPGA上实现的频率移位DSP。

两种LO步进模式:

1. 整数步进模式包括4、12和24 MHz步长

2. 分级步进模式包括200 KHz步长。该模式可提供更大间隔但同样会产生更多杂波信号,该模式可确保达到指标要求。

NI PXIe-5644R合成器LO先将120 MHz时钟输入锁相环(PLL),该锁相环包括3个频率分别为2至2.5 GHz、2.5至3 GHz以及3至4 GHz的矢量控制振荡器(VCO)。如所需输出信号小于4 GHz,当前信号将被切换至分频器。类似的,如果所需结束信号为4至6 GHz,当前信号将被切换至倍频器(2个乘法器)。接下来进入一个带额外除法器的滤波器组,以便在需要时删除谐波。

在设置一定增益后,信号将被切换至一个内部或外部振荡器,后者用于需要相位相干的MIMO应用。为了提高MIMO配置的性能,在导出之前也可通过校准ADC对LO路径进行校准。如图8所示,LO信号将会进入包含低通和带通滤波器的滤波器组,该低通和带通滤波器与NI PXIe-5644R RF接收器和发送器中使用的滤波器相同。

图8:NI PXIe-5644R合成器LO顶层框图

谱纯度

当输入RF信号与LO混合时,该信号将含有来自LO的谱边缘,因此LO具有良好的谱纯度十分重要。频带VSA通常使用现成的集成合成器,通常其效果不如传统的离散合成器。NI PXIe-5644R可用于宽带仪器设计,其特点为可以从头创建一个传统的离散合成器。该方式可允许NI PXIe-5644R在仪器的所有频率范围内实现良好的测量性能。

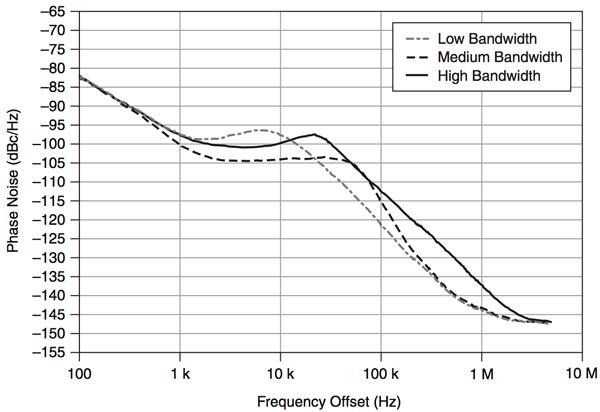

NI PXIe-5644R包括下列三种不同的PLL带宽选项,这些选项的不同之处在于相位噪声和稳定时间。

1. 高带宽—更低频率稳定时间(250 us)和更高相位噪声

2. 中等带宽—中等稳定时间(500 us),与低带宽选项类似的相位噪声,低带宽选项已为窄带(500 MHz或更小)进行优化

3. 低带宽—优化相位噪声以及更高的频率稳定时间(1 ms)

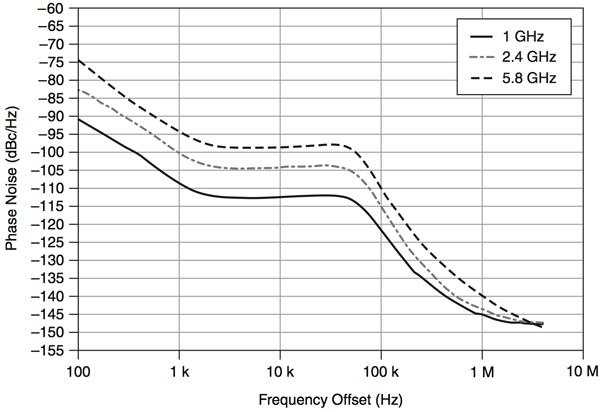

当测量RF标准时(如802.11ac和LTE),通常建议使用中等带宽选项。但如果无需考虑调整速度,也可以选择低带宽选项。高带宽选项的使用范例为高速调频。图9显示了不同PLL带宽选项的相位噪声。图10显示了仅使用中等带宽选项时不同频率的相位噪声。

图9:已测量的2.4 GHz相位噪声和循环带宽

图10:使用中等PLL带宽选项测量以下频率的相位噪声:1 GHz、2.4 GHz和5.8 GHz

6. 校准

每张NI PXIe-5644R板卡在出厂时均已对频率和幅值响应进行了独立精确校准,每个仪器均包含用于验证NIST可跟踪精度水平的校准证书。外部工厂校准可调整频率参考、内部LO路径增益、外部LO路径增益、RF输入增益和RF输出增益。为了使NI PXIe-5644R长期达到规范,建议使用一年(或在较宽规范时使用两年)工厂校准。

校准路径

NI PXIe-5644R校准依赖于一条位于RF输入和RF输出之间的固定路径。该路径可使用SMA-SMA半硬式线缆连接校准输入(CAL IN)和校准输出(CAL OUT)前面板连接器。请不要从设备前面板松开或移除该线缆,否则将影响自校准功能。

自校准

此外当环境温度变化超过5摄氏度(5° C)时,建议进行自校准。温度的起伏会降低NI PXIe-5644R的几个技术指标的性能。执行自校准可根据周边环境温度对性能进行补偿和优化。自校准通过调整以下NI PXIe-5644R参数来校正温度:

. LO路径增益

. RF输入增益

. RF输出增益

. RF输入LO泄漏

. RF输出LO泄漏

. RF输入镜频抑制

. RF输出镜频抑制

校准合成器通过一个频率稳定且失真度低的放大器以提供一个稳定的幅值。设备上的校准表将同时扫描频率和功率,同时还包括频率的矢量校准。高级校准技术是NI PXIe-5644R通过小尺寸实现研发级仪器性能的主要原因之一。

以上是关于NI PXIe-5644R矢量信号收发器硬件架构的主要内容,如果未能解决你的问题,请参考以下文章