上升沿

Posted drunknbeard

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了上升沿相关的知识,希望对你有一定的参考价值。

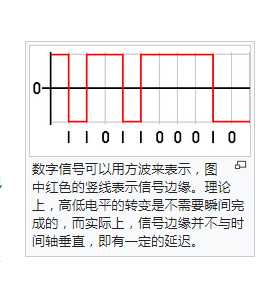

在电子学中,信号边缘(英语:signal edge),或称信号边沿,是数字信号在两种逻辑电平(0或1)之间状态的转变。由于数字信号电平由方波来表示,因此这种状态的变化被称为“边缘”。

信号的一个上升沿(rising edge)是数字信号从低电平向高电平的转变。当接入的时间脉冲信号由低电平向高电平转变时,触发器电路被触发,而当接入的时间脉冲信号从高电平向低电平转变时,这种转变则被触发器电路忽略,那么我们称这个触发器电路为上升沿触发的e(rising edge-triggered)。

与上升沿对应的概念为下降沿(falling edge),它是指数字信号从高电平向低电平的转变。当接入的时间脉冲信号由高电平向低电平转变时,触发器电路被触发,而当接入的时间脉冲信号从低电平向高电平转变时,这种转变则被触发器电路忽略,那么我们称这个触发电路为下降沿触发的(falling edge-triggered)。

信号边缘可以被用来触发时序控制,在时间脉冲上升沿或下降沿触发的T触发器就是一个典型的例子,这类触发器并不是通常的电平敏感,而是信号边缘敏感。此外,在硬件描述语言中,使用Verilog自定义原语(user defined primitives)时,上升沿、下降沿分别以(01)、(10)表示,也可以用缩写字母r、f表示。

以上是关于上升沿的主要内容,如果未能解决你的问题,请参考以下文章