《FPGA全程进阶---实战演练》第五章 基于74HC595的LED操作

Posted raymon_tec

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了《FPGA全程进阶---实战演练》第五章 基于74HC595的LED操作相关的知识,希望对你有一定的参考价值。

1基础理论部分

1.1分频

分频,是的,这个概念也很重要。分频是指将一单一频率信号的频率降低为原来的1/N,就叫N分频。实现分频的电路或装置称为“分频器”,如把33MHZ的信号2分频得到16.5MHZ的信号,3分频得到11MHZ的信号,10分频得到3.3MHZ的信号。

分频主要是相对于主晶振来说,用不到那么高的频率,开发板一般根据具体需要会加入晶振,一般若是功耗较高可选用50MHz,其他情况可以相对调整,如24MHz等等。那么分频的典型应用,二分频,四分频,八分频,还有任意分频。

对于分频,我们可以利用quartus ii 自带的PLL进行分频,这样会占用一定的资源,也可以利用计数器实现一定的分频,注意,FPGA中不同于其他的CPU,没有计时器的概念,只有计数器。

1.2 LED

LED(light emitting diode),发光二极管,简称LED,是一种能够将电能转化成可见光的固态的半导体器件,可以直接把电转换成光。可以用在电路及仪器中作指示灯,或者组成文字或数字显示等。有不同化合物制成的二极管如砷,镓,磷等化合物制成,不同的化合物组合会显示不同颜色的光。

在设计LED的驱动电路时,不能直接接到3.3V或者5V来点亮,LED有额定电流,超过这个额定电流,LED就会烧掉,反接也会烧掉。一般的LED的额定电流从10mA~1A不等。FPGA开发采用的LED主要是贴片0805或者0603等,额定电路一般从10mA~30mA.

1.3 74HC595

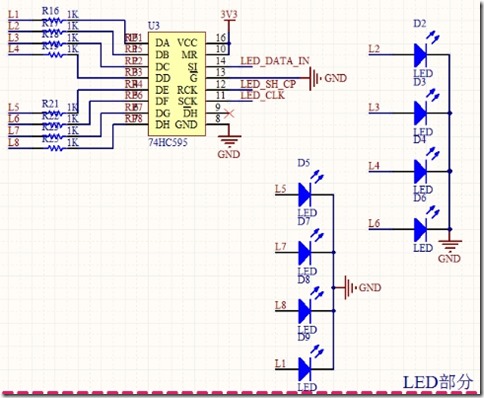

开发板上面的LED控制是用串入并出/串出的移位寄存器74HC595芯片,芯片在电路中的接入情况如图5.1所示,实物图如图5.2所示。其中MR引脚直接接高电平,不进行复位。串出引脚9不接,不进行串出引脚的使用。输出使能引脚13直接接地,手册上建议。11和12引脚分别为移位寄存器时钟输入和存储时钟输入,分别引出。

图5.1 LED部分电路图

图5.2 实物图

2 verilog代码实现部分

2.1 74HC595 控制部分

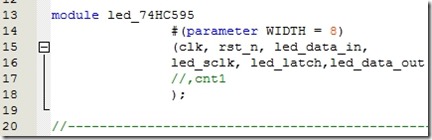

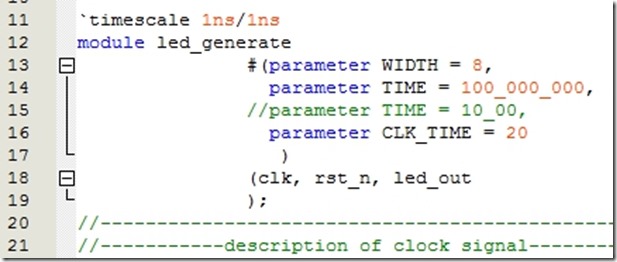

14行定义了一个全局参数WIDTH = 8,用来控制程序下面所有的有关于数量的使用。

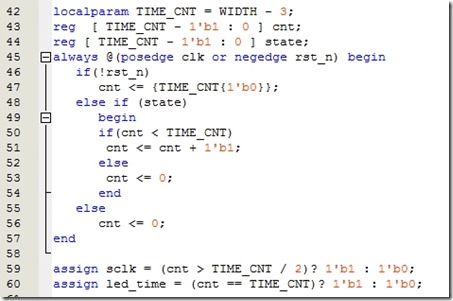

59行和60行分别定义了时钟信号和时钟使能信号,其中时钟信号sclk时钟周期前半段为低电平,后半段为高电平,可以实现对数据的中间采样,时钟使能信号led_time可以控制数据和时钟对齐。48行的state是一个状态改变的寄存器,只要数据一更新,state就有效。

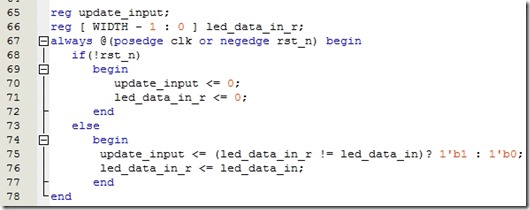

75行定义了update_input信号用来检测输入数据的变化。

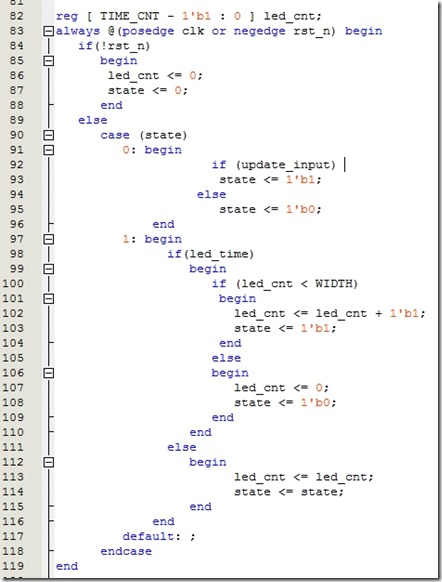

状态转换部分,在case语句中先检测state的初始位,然后进入循环操作,检测update_input是否使能,使能更新state,不使能保持state,更新后开始输出位数计数器led_cnt的计数

在121到123行,对输出的三路信号进行了约束限制,这种方法值的借鉴,在用不到时不输出信号,用到时输出信号,最大量的节省时钟。Led_data_out是先从高位输出到低位。

2.2 LED数据产生部分

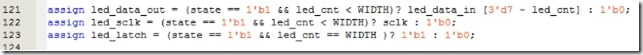

在模块声明处,仍旧使用全局定义变量,控制模块中常量的使用。

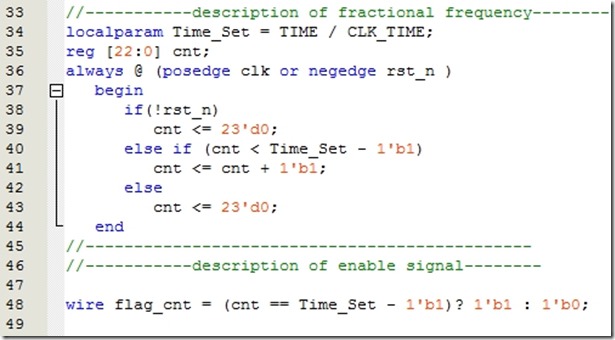

计数模块,产生时钟使能信号。

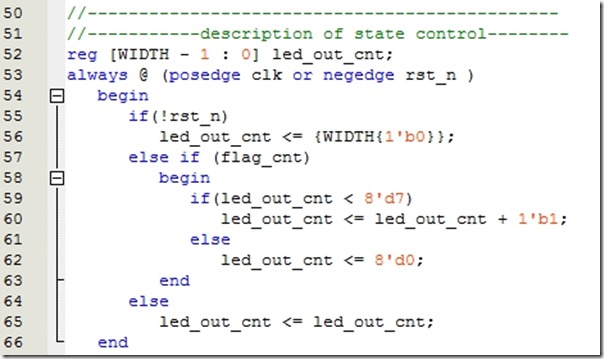

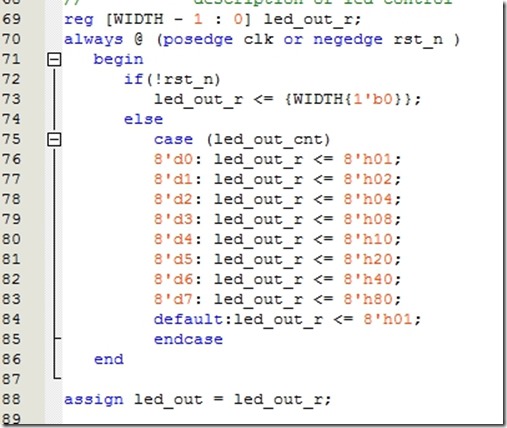

Reg型变量Led_out_cnt是用来控制LED变化, 每当时钟信号使能开始计数,板卡上面一共有8个LED,所以计数8个即可。

LED解码部分,通过上面的led_out_cnt信号进行解码,控制LED的流水操作。

3 modelsim验证部分

3.1 led_generate 模块仿真

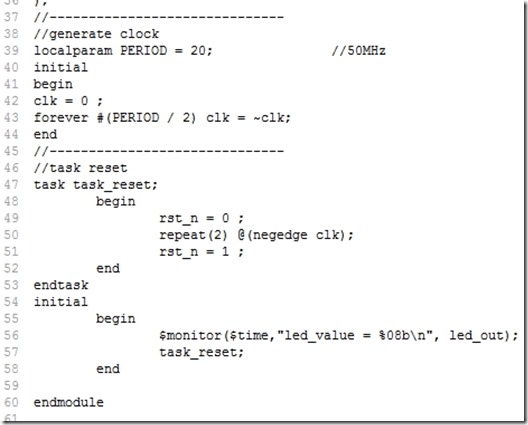

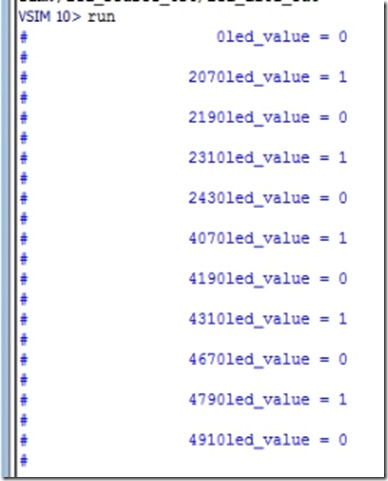

43行产生时钟信号,通过PERIOD进行周期控制。49~51产生复位信号,当时钟两次下降沿后复位信号拉高。56行用来监测led_out输出的时间,生成的脚本文件如图5.3所示。

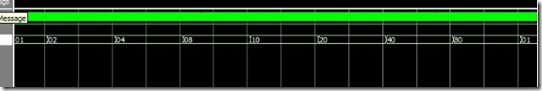

图5.3仿真波形

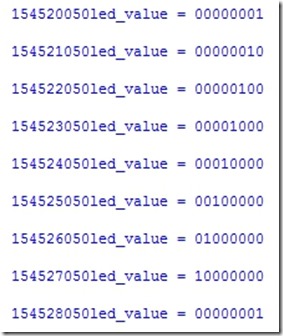

图5.4是利用脚本文件生成,可以观察到实现了流水功能,且时间间隔1s;

图5.4 脚本生成文件

3.2 led_74HC595 模块仿真

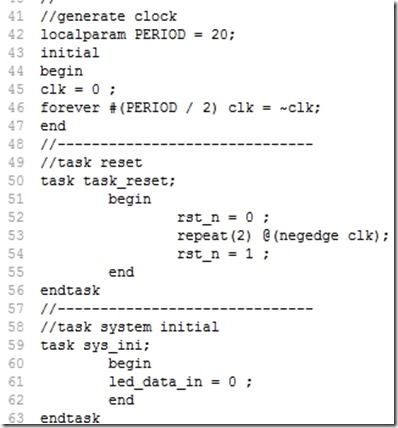

前半部分和上述都一样,可以作为固定部分,大家可以自行复制即可。59行到63行增加了系统输入信号初始化部分。在输入信号输入前,最好最安全就是进行一次初始化。

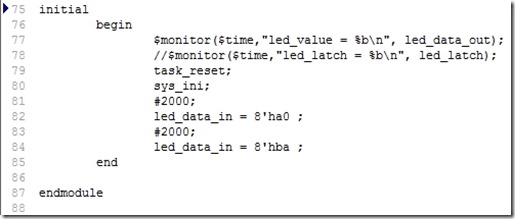

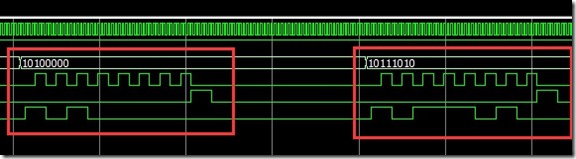

75行到87行是对输入进行模拟输入,并监测led_data-out信号,输出的结果如图5.5所示,由图可以看到时间间隔为120ns。

图5.6是仿真波形,可以看到时钟led_sclk每次采样在输入信号的正中间位置,最大程度保证采样可靠。

图5.5 脚本文件

图5.6 仿真波形

以上是关于《FPGA全程进阶---实战演练》第五章 基于74HC595的LED操作的主要内容,如果未能解决你的问题,请参考以下文章

封神台靶场:第五章:进击!拿到Web最高权限!配套课时:绕过防护上传木马实战演练

提供跟老男孩学Linux运维Shell编程实战的第第五章源代码