FPGA Prototyping By Verilog Examples第五章 状态机FSM设计

Posted yf869778412

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA Prototyping By Verilog Examples第五章 状态机FSM设计相关的知识,希望对你有一定的参考价值。

上升沿检测电路之Moore型FSM

// Listing 5.3

module edge_detect_moore

(

input wire clk, reset,

input wire level,

output reg tick

);

// symbolic state declaration

localparam [1:0]

zero = 2\'b00,

edg = 2\'b01,

one = 2\'b10;

// signal declaration

reg [1:0] state_reg, state_next;

// state register

always @(posedge clk, posedge reset)

if (reset)

state_reg <= zero;

else

state_reg <= state_next;

// next-state logic and output logic

always @*

begin

state_next = state_reg; // default state: the same

tick = 1\'b0; // default output: 0

case (state_reg)

zero:

if (level)

state_next = edg;

edg:

begin

tick = 1\'b1;

if (level)

state_next = one;

else

state_next = zero;

end

one:

if (~level)

state_next = zero;

default: state_next = zero;

endcase

end

endmodule

上升沿检测电路之Mealy型FSM

// Listing 5.4

module edge_detect_mealy

(

input wire clk, reset,

input wire level,

output reg tick

);

// symbolic state declaration

localparam zero = 1\'b0,

one = 1\'b1;

// signal declaration

reg state_reg, state_next;

// state register

always @(posedge clk, posedge reset)

if (reset)

state_reg <= zero;

else

state_reg <= state_next;

// next-state logic and output logic

always @*

begin

state_next = state_reg; // default state: the same

tick = 1\'b0; // default output: 0

case (state_reg)

zero:

if (level)

begin

tick = 1\'b1;

state_next = one;

end

one:

if (~level)

state_next = zero;

default: state_next = zero;

endcase

end

endmodule

上升沿检测电路之基本门电路设计

// Listing 5.5

module edge_detect_gate

(

input wire clk, reset,

input wire level,

output wire tick

);

// signal declaration

reg delay_reg;

// delay register

always @(posedge clk, posedge reset)

if (reset)

delay_reg <= 1\'b0;

else

delay_reg <= level;

// decoding logic

assign tick = ~delay_reg & level;

endmodule

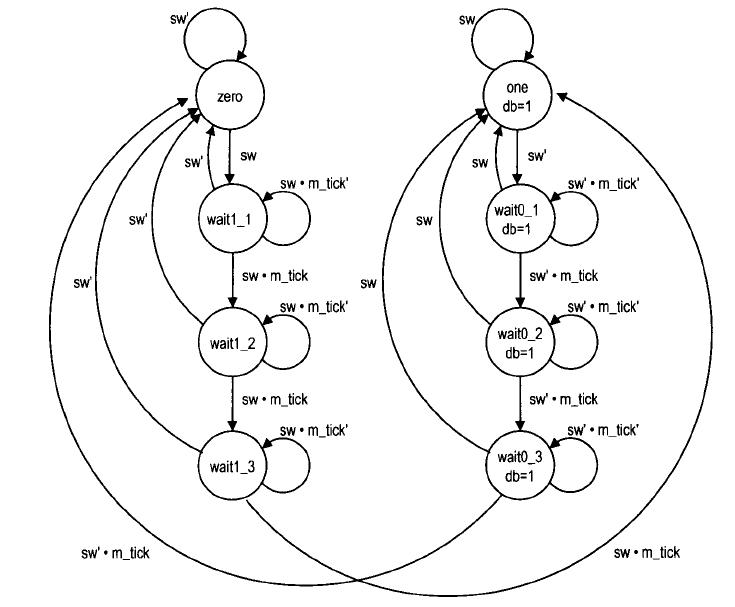

按键消抖电路FSM

// Listing 5.6

module db_fsm

(

input wire clk, reset,

input wire sw,

output reg db

);

// symbolic state declaration

localparam [2:0]

zero = 3\'b000,

wait1_1 = 3\'b001,

wait1_2 = 3\'b010,

wait1_3 = 3\'b011,

one = 3\'b100,

wait0_1 = 3\'b101,

wait0_2 = 3\'b110,

wait0_3 = 3\'b111;

// number of counter bits (2^N * 20ns = 10ms tick)

localparam N =19;

// signal declaration

reg [N-1:0] q_reg;

wire [N-1:0] q_next;

wire m_tick;

reg [2:0] state_reg, state_next;

// body

//=============================================

// counter to generate 10 ms tick

//=============================================

always @(posedge clk)

q_reg <= q_next;

// next-state logic

assign q_next = q_reg + 1;

// output tick

assign m_tick = (q_reg==0) ? 1\'b1 : 1\'b0;

//=============================================

// debouncing FSM

//=============================================

// state register

always @(posedge clk, posedge reset)

if (reset)

state_reg <= zero;

else

state_reg <= state_next;

// next-state logic and output logic

always @*

begin

state_next = state_reg; // default state: the same

db = 1\'b0; // default output: 0

case (state_reg)

zero:

if (sw)

state_next = wait1_1;

wait1_1:

if (~sw)

state_next = zero;

else

if (m_tick)

state_next = wait1_2;

wait1_2:

if (~sw)

state_next = zero;

else

if (m_tick)

state_next = wait1_3;

wait1_3:

if (~sw)

state_next = zero;

else

if (m_tick)

state_next = one;

one:

begin

db = 1\'b1;

if (~sw)

state_next = wait0_1;

end

wait0_1:

begin

db = 1\'b1;

if (sw)

state_next = one;

else

if (m_tick)

state_next = wait0_2;

end

wait0_2:

begin

db = 1\'b1;

if (sw)

state_next = one;

else

if (m_tick)

state_next = wait0_3;

end

wait0_3:

begin

db = 1\'b1;

if (sw)

state_next = one;

else

if (m_tick)

state_next = zero;

end

default: state_next = zero;

endcase

end

endmodule

路漫漫其修远兮,吾将上下而求索

转载自:http://www.cnblogs.com/qiweiwang/archive/2011/04/12/2013415.html

以上是关于FPGA Prototyping By Verilog Examples第五章 状态机FSM设计的主要内容,如果未能解决你的问题,请参考以下文章