怎么对ZYNQ的FCLK做时钟组约束

Posted kingstacker

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了怎么对ZYNQ的FCLK做时钟组约束相关的知识,希望对你有一定的参考价值。

前言

对于包含PS和PL的设计,两者的数据交互PL必然会用到PS端的时钟。

对于FCLK(PS端时钟输入到PL端)的约束,此时钟的基础约束已在IP中产生。以下想约束其异步时钟的时钟组特性。

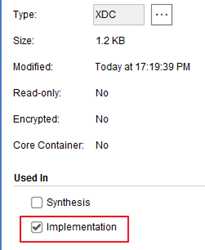

注意事项:FCLK的名字在综合时不可见,在适配阶段才可见,所以对于约束文件的属性需要选择只在适配阶段有效,否则综合时报警告(感觉无伤大雅)。

但PL中又有别的时钟,与FCLK是异步的,而且这些时钟之间并不需要进行时序分析。

则有两种选择,(1)约束false路径。但时钟之间的路径是双向的,则需要正着约束一下,反着也要约束,比较麻烦。

(2)使用clock group约束。可以划分时钟域,时序分析只会分析时钟域中的情况,不会分析跨时钟域部分。

而跨时钟域部分通常由开发者代码保证不会产生亚稳态。

流程

(1)首先我们并不清楚fclk在综合编译后叫啥名字,所以首先就是需要获取fclk名字。

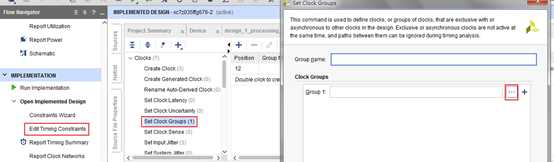

打开适配后的设计,点击编辑时序约束。

找寻时钟。

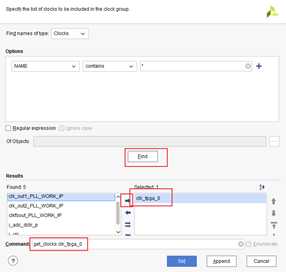

在下图中点击Find查找所有时钟,左下角就会显示出时钟名,添加到右侧,就得到了command中的名字。当然也可直接使用图形工具进行相应的约束操作。

约束语句如下:三个时钟组互不相关,跨时钟域处理需要代码保证。

set_clock_groups -async -group [get_clocks -include_generated_clock i_clk] \\

-group [get_clocks -include_generated_clock i_adc_dclk_p] -group [get_clocks clk_fpga_0]

含义说明:i_clk和i_adc_dclk_p调用了两个不同的pll,两者的输出时钟不晓得名字就可以用上述语法进行约束。

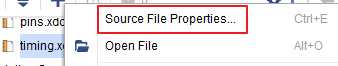

(2)设置时序约束文件只在适配阶段才起作用。

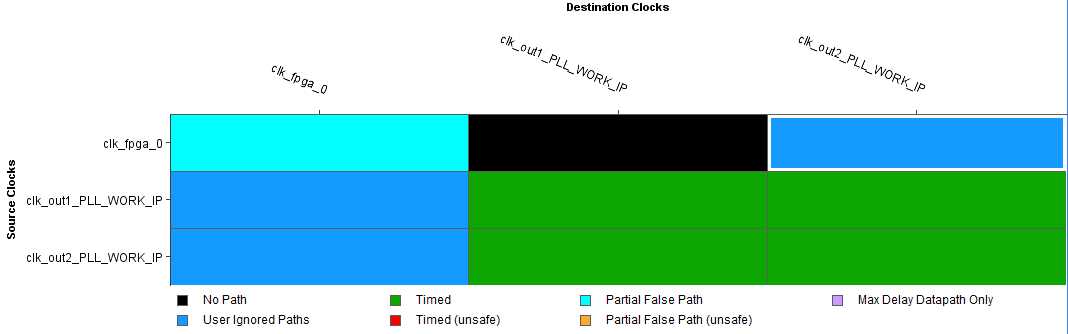

(3)重编译检查劳动成果。对时钟相关性进行分析,可以看到异步路径已经被STA忽略。

以上。

以上是关于怎么对ZYNQ的FCLK做时钟组约束的主要内容,如果未能解决你的问题,请参考以下文章