传统同步设计中的功耗

Posted duanxianfengzhengfly

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了传统同步设计中的功耗相关的知识,希望对你有一定的参考价值。

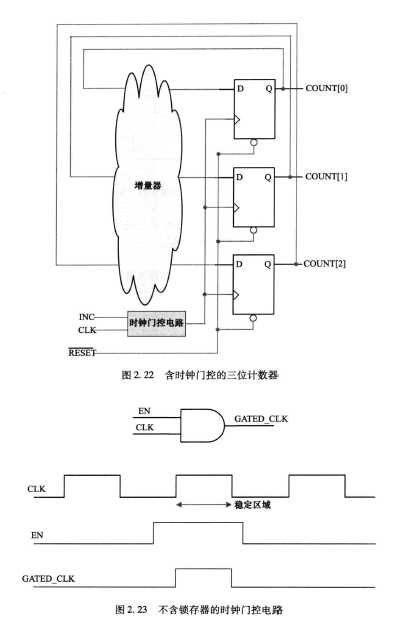

在传统设计风格中,系统时钟控制每个寄存器时钟端,功耗由3部分组成

1.每个时钟沿变化的组合逻辑所产生的功耗(触发器驱动这些组合逻辑);

2.触发器本身产生的功耗(即使触发器的输入和内部状态未变化,该功耗仍然存在);

3.设计中时钟树产生的功耗。

时钟树几乎消耗了整个芯片的功耗的50%,因此最好始终在根部产生或关闭时钟,以使整个时钟树都关闭;

解决方案

用门控时钟:

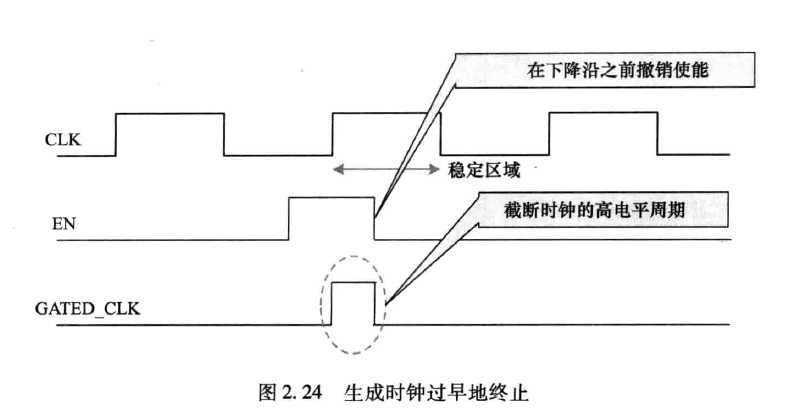

1.不含锁存器的门控时钟,只简单的使用单个门(与门,或门)

此要求使能信号宽度覆盖时钟高电平时时间,

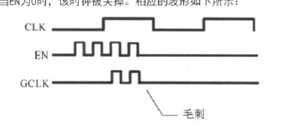

不然会产生过早截断时钟

或者产生多个时钟脉冲毛刺

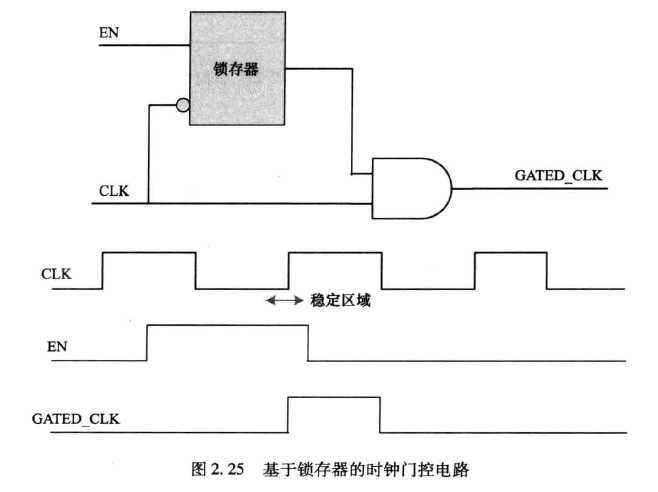

2.基于锁存器的门控时钟:

这样只要使能信号在下降沿时满足条件就可以很好的实现门控;

注意:使用下降沿有效的时钟,使用或门进行控制,并用正沿触发错存器寄存使能信号。

以上是关于传统同步设计中的功耗的主要内容,如果未能解决你的问题,请参考以下文章

数字后端低功耗 - 多种低功耗技术及其在IC后端布局中的应用