低功耗设计技术--Multi VDD--Level shifter

Posted asic-horizon

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了低功耗设计技术--Multi VDD--Level shifter相关的知识,希望对你有一定的参考价值。

本文转自:自己的微信公众号《集成电路设计及EDA教程》

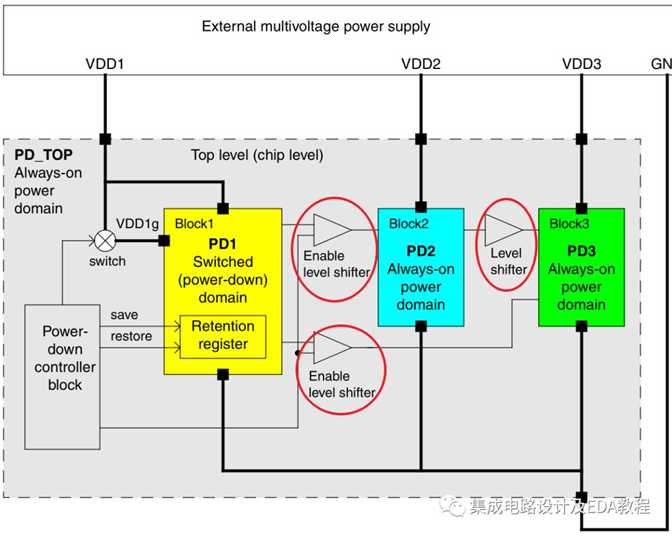

前面的推文中我们分别介绍了低功耗设计中的Multi-VDD技术以及门控电源技术。在实际的低功耗设计中,门控电源技术中也常常结合Multi-VDD技术一起使用。

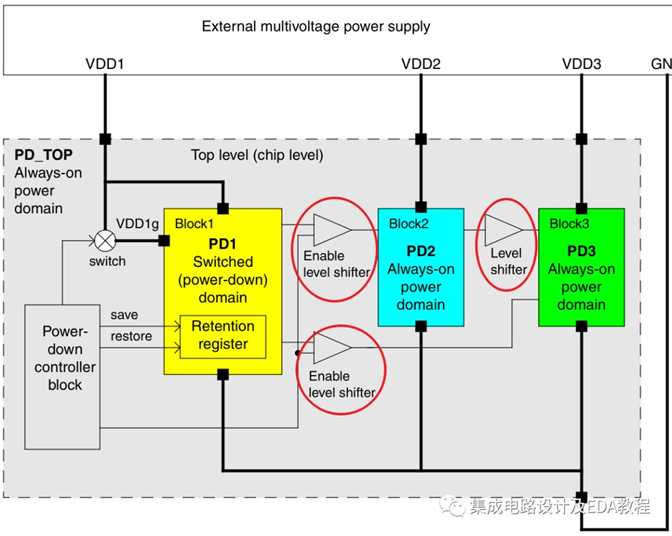

在使用了Multi-VDD技术之后,设计中会形成多个Power Domain(PD):

不同Power Domain之间如果需要数据的Talk,那么在中间需要插入Level Shifter(电平转换单元):

本推文我们来讲解一下第二个特殊的Cell -- Level Shifter。

Level shifter Cell

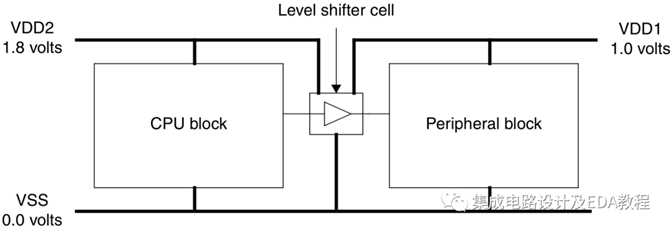

Level Shifters主要是多供电电压(MSV)的设计中,在2个不同电压域之间有数据交互的情况下,需要将某个电压域输出的电平转换成另一个电压域可以识别的逻辑电平,因此需要用到电平转换的器件,这就是Level Shifter。这种Cell在我们使用的IO中也广泛存在,用于将外部的电压与Core电压之间进行转换。

根据电平转换的方向,Level Shifter可以分为三种:

HL -> 高电平转低电平

LH -> 低电平转高电平

HL_LH -> 双向转换均可

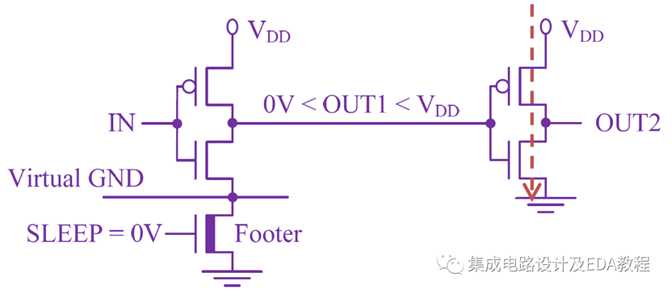

另外,如果设计中还采用了前面推文中讲的Power Gating技术,在不通电压域之间进行通信的情况下,除了需要添加Level Shifter之外还需要用到另外一种Cell -> Isolation Cell。因为电源关断之后,其驱动的电路就出现了输入浮空的情况,它的输入会处于高阻态,会用泄放电流将上面的电荷缓慢泄放掉,再次期间,其状态是不能确定的(如下图所示)。因此,为了解决这个问题,我们需要在电源关闭电路的输出端添加一个隔离单元(Isolation Cell)将输出钳位到一个确定的状态。

一般来说Isolation Cell的输出部分有较大的电容负载,也就是说Isolation Cell的延时将会比较大,对时序有一定的影响,是需要注意的。

关于Isolation Cell的详细内容下篇推文单独讲。

如果设计中含有Multi-VDD且有的Power Domain可以被关断,多个Domain之间还有数据交互,那么既需要用到Level Shifter也需要Isolation Cell,这种情况也非常常见。因此一般Foundary都会那种带有Isolation功能的Level shifter,兼两种功能。

下图就是这种情况,PD1是可被关断的,它与PD2以及PD3之间用的Level Shifter就是带有Isolation功能的Level Shifter。而PD2是Always On的,所以它送到PD3的数据只需要用普通的Level Shifter即可。

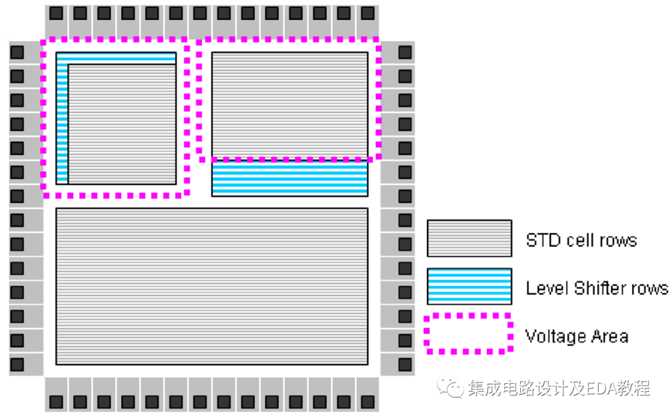

Level Shifter的物理布局

Level shifter是 Always-on Cell,一般有多个电源地Pin。它们的结构比较复杂,一般要比普通的Cell高度要高,它们的作用非常关键,我们需要保证它们的电源地连接是正确的。

考虑到以上因素,很多设计会采用下面的方案来摆放Level Shifter,将它们放置在特定区域内,Level Shifter的电源地Rail以及PG Pin的连接也更加规范有条理:

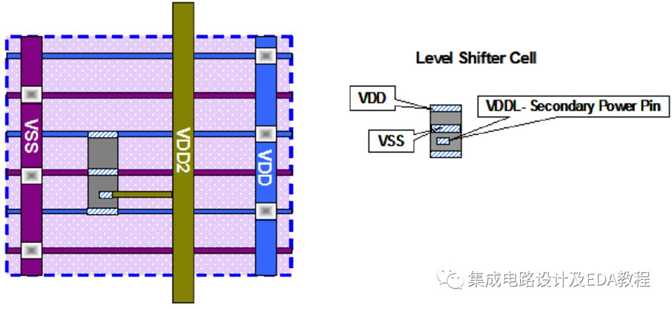

如下图所示为Dual Height的Level shifter Cell在版图中的摆放及其PG Pin的连接:

上面这种PG的连接特别的不方便,可能会占用较多的Routing Resources引起DRC。

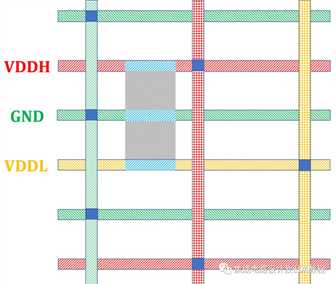

除此之外,还可以采用下面的双Power Rail的方式,Level shifter横跨两个Rail的高度,两个不同的VDD,一个GND。

下面描述的是Level Shifter的Liberty格式:

|

cell(level_shifter) { is_level_shifter : true ; #定义为true,则该Cell被认为是lever shifter cell level_shifter_type : HL | LH | HL_LH ; #定义电平转换方向,HL表示高电平转低电平,LH表示低电平转高电平,HL_LH表示都可以用 input_voltage_range (<float>, <float>); #输入电压范围,指该Cell输入连接的电路,电压工作范围,EDA工具会根据Operating Condition的选择,检查该Cell是否满足电路需要,可以在功能pin中进行定义,如果在cell主体定义,则必须与output_voltage_range同时存在 output_voltage_range (<float>, <float>);#输出电压范围,指该Cell输出连接的电路,电压工作范围,EDA工具会根据Operating Condition的选择,检查该Cell是否满足电路需要,可以在功能pin中进行定义,如果在cell主体定义,则必须与input_voltage_range同时存在 … pg_pin(<pg_pin_name_P>) { pg_type : primary_power; std_cell_main_rail : true; #该primary_power连接在Cell设计中的主rail … } pg_pin(<pg_pin_name_G>) { pg_type : primary_ground; … } pin (data) { direction : input; input_signal_level : “<voltage_rail_name>”; #输入信号电压环名 input_voltage_range ( <float> , <float>); level_shifter_data_pin : true ; #数据功能Pin … }/* End pin group */ pin (enable) { direction : input; input_voltage_range ( <float> , <float>); level_shifter_enable_pin : true ; #使能Pin,如果level shifter还作为isolation cell的时候,使能信号会在电源关闭时停止level shifter功能,仅仅作为isolation cell存在 … }/* End pin group */ pin (output) { direction : output; output_voltage_range ( <float> , <float>); power_down_function : (!pg_pin_name_P + pg_pin_name_G); … }/* End pin group */ … }/* End Cell group */

#power_down_function 属性用来识别出何时output pin处于电源被关断的状态。 The power_down_function string attribute is used to identify the condition when an output pin is switched off by pg_pin and to specify the Boolean condition under which the cell’s output pin is switched off (when the cell is in "off" mode due to the external power pin states) |

参考文献:

孙轶群 ,国民技术股份有限公司,数字集成电路低功耗物理实现技术与UPF

Synopsys Low-Power Flow User Guide

以上是关于低功耗设计技术--Multi VDD--Level shifter的主要内容,如果未能解决你的问题,请参考以下文章