VLSI数字信号处理系统——第十七章低功耗设计

Posted 夏风喃喃

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VLSI数字信号处理系统——第十七章低功耗设计相关的知识,希望对你有一定的参考价值。

VLSI数字信号处理系统——第十七章低功耗设计

作者:夏风喃喃

参考:

VLSI数字信号处理系统:设计与实现 (美)Keshab K.Parhi/著

文章目录

一. 引言

二. 理论背景(略)

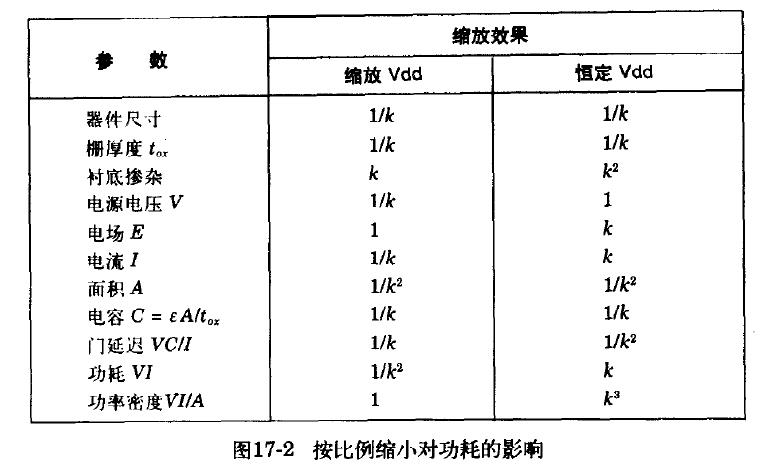

三. 按比例缩小与功耗

四. 功耗分析

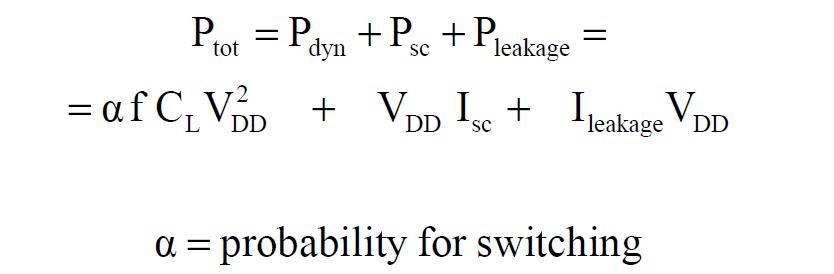

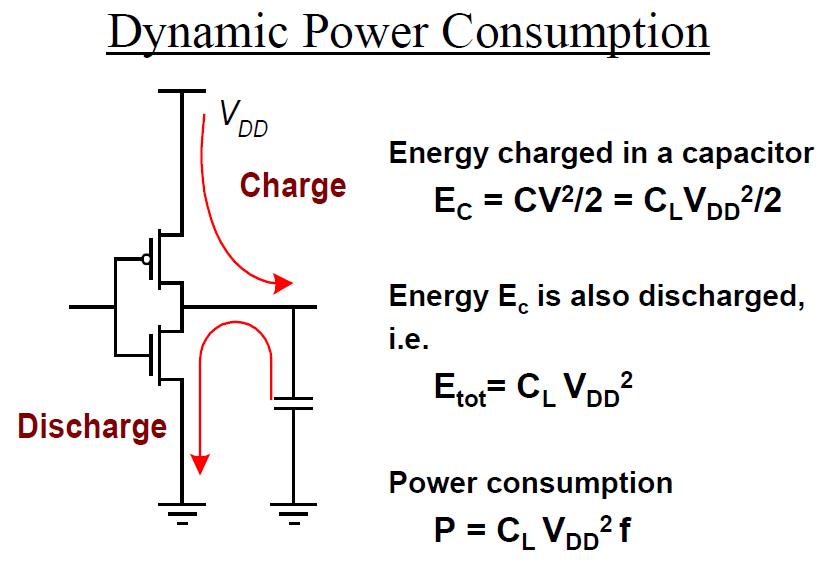

数字CMOS电路的功耗可以表示为:

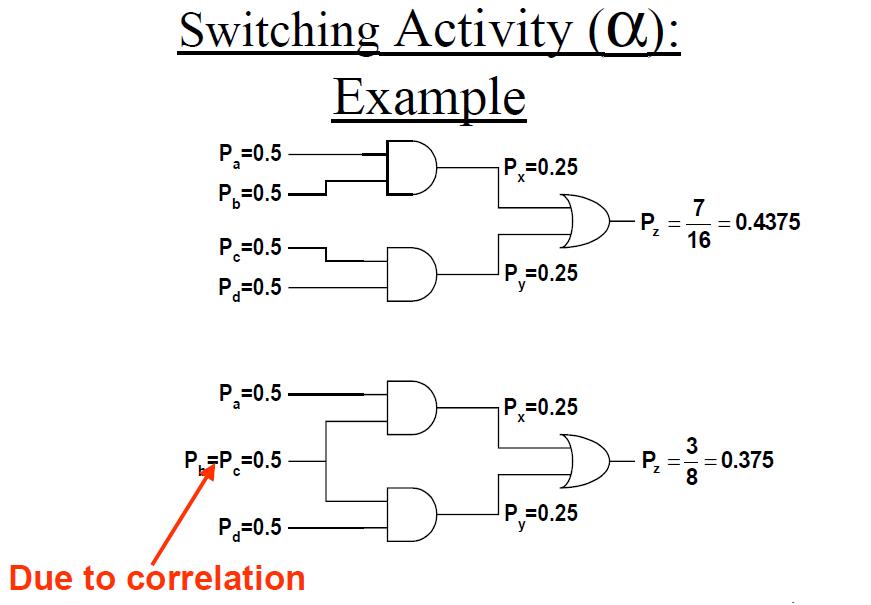

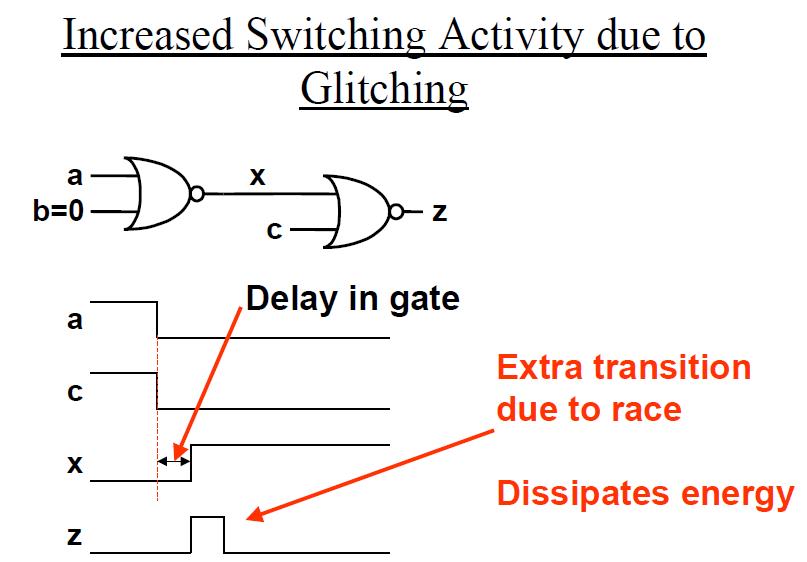

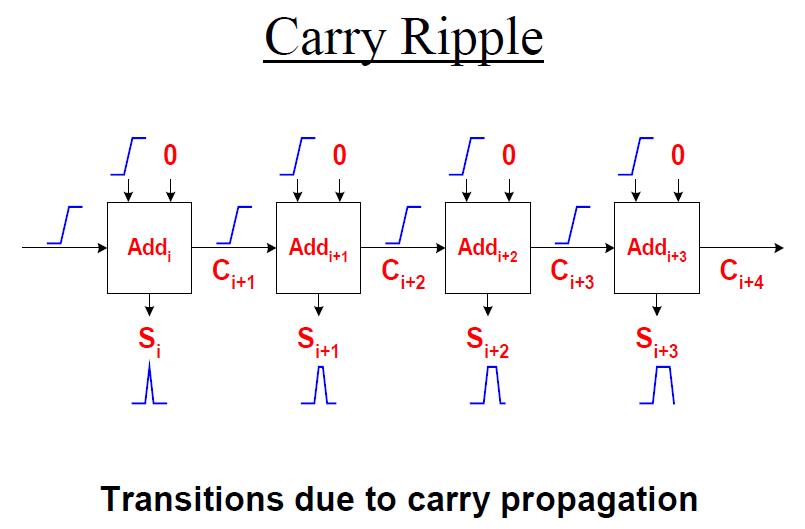

4.1 开关活动率

动态翻转因子:

毛刺会增加动态翻转因子。

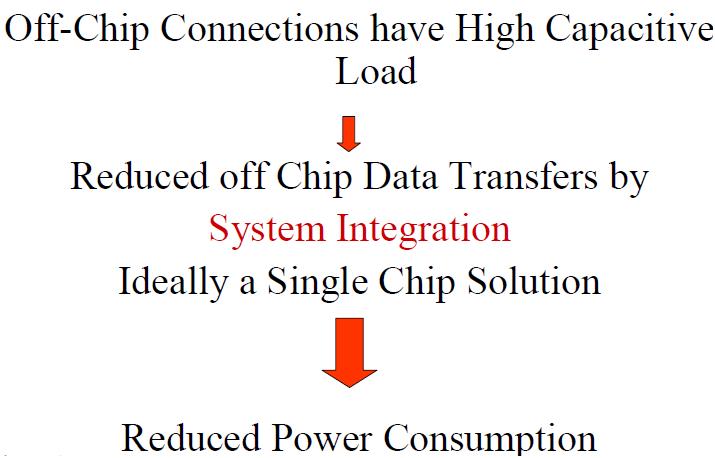

4.2 物理电容

动态功耗:

单片集成可以减小负载电容,减小动态功耗。

五. 功耗降低技术

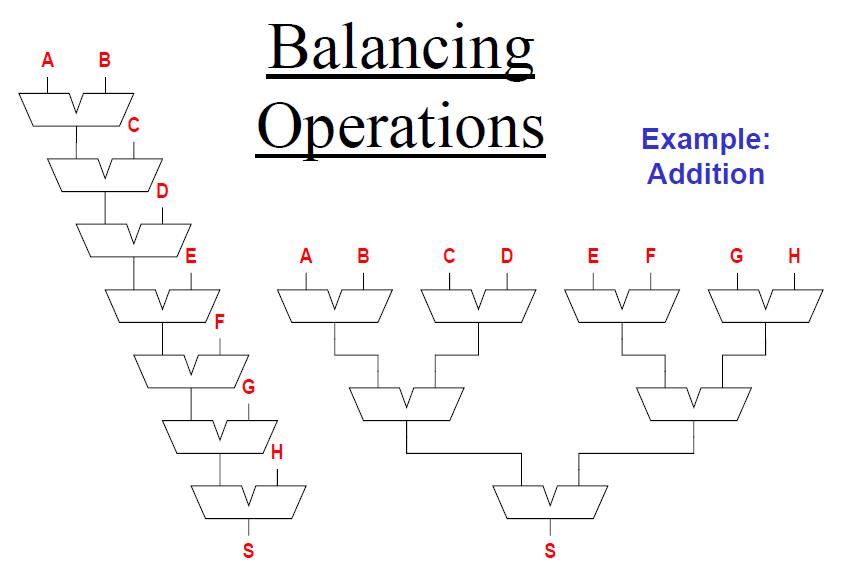

5.1 路径平衡

5.2 晶体管和逻辑门尺寸优化(略)

5.3 晶体管重排序(略)

5.4 用于低功耗的重定时(略)

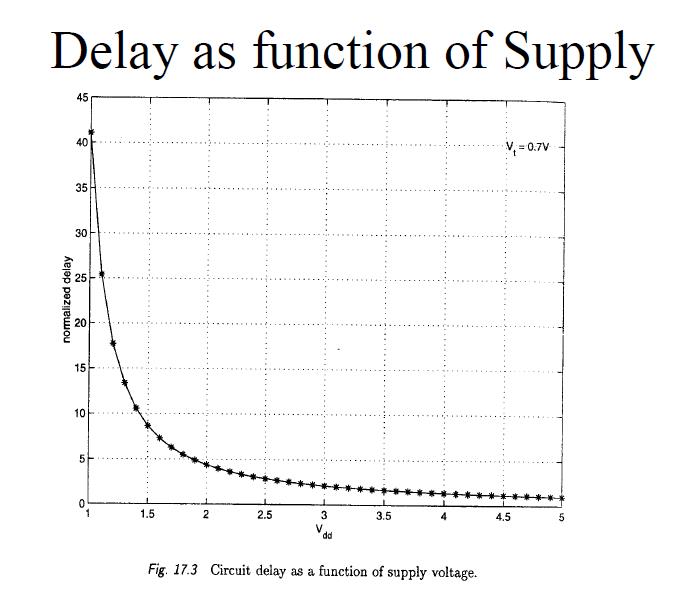

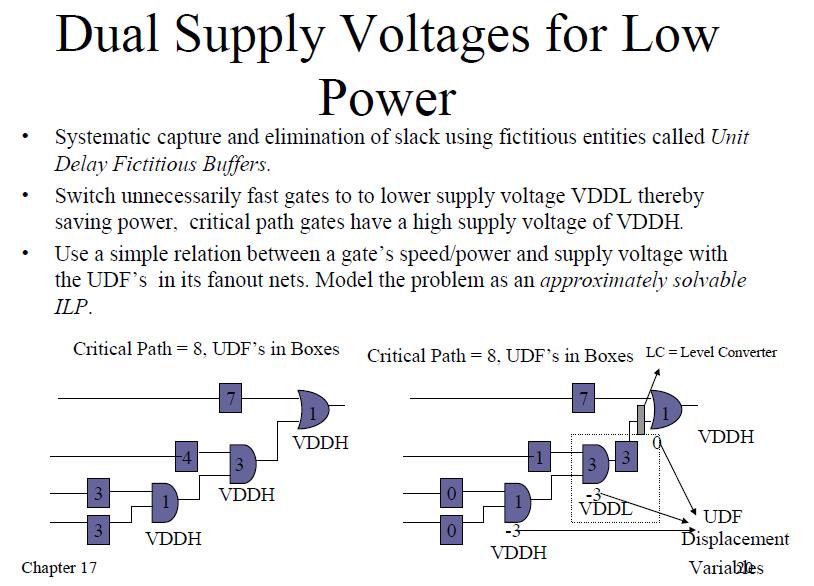

5.5 电压按比例缩小和多电源电压

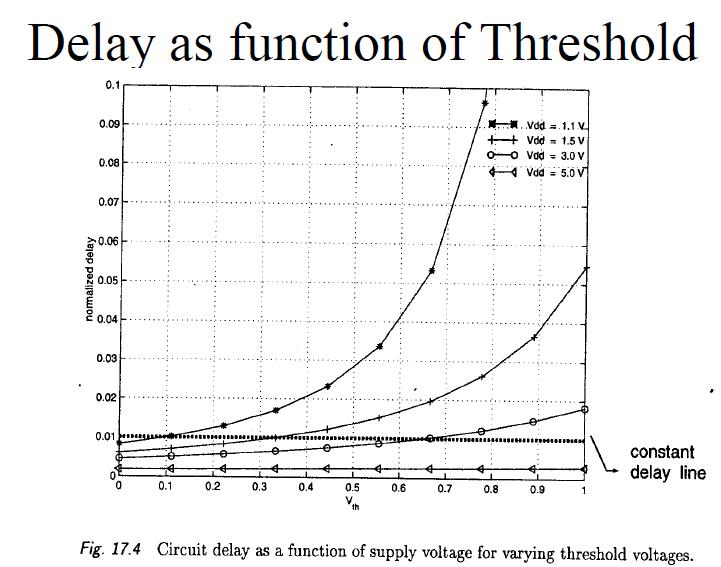

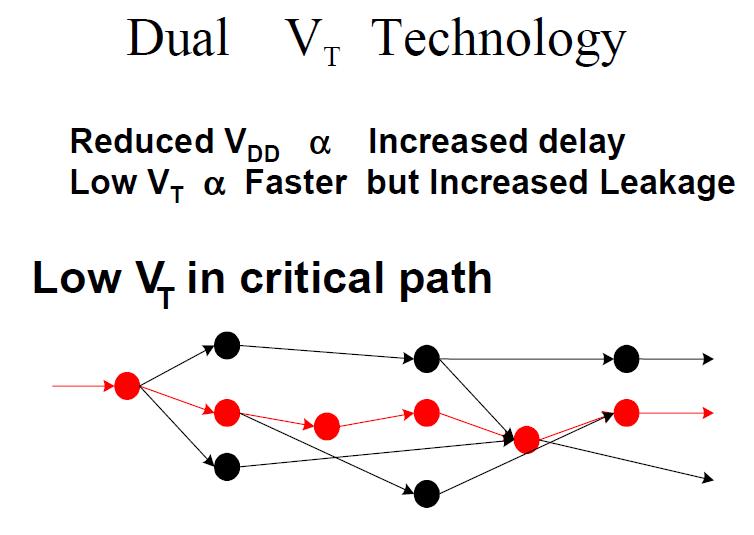

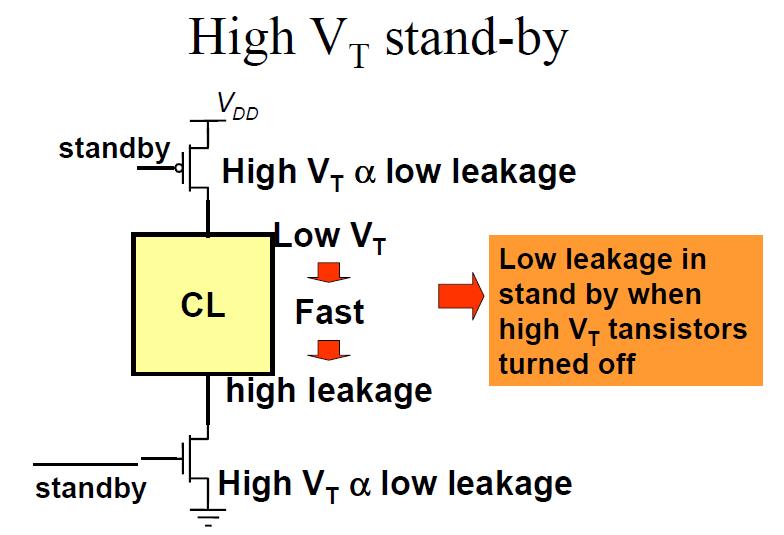

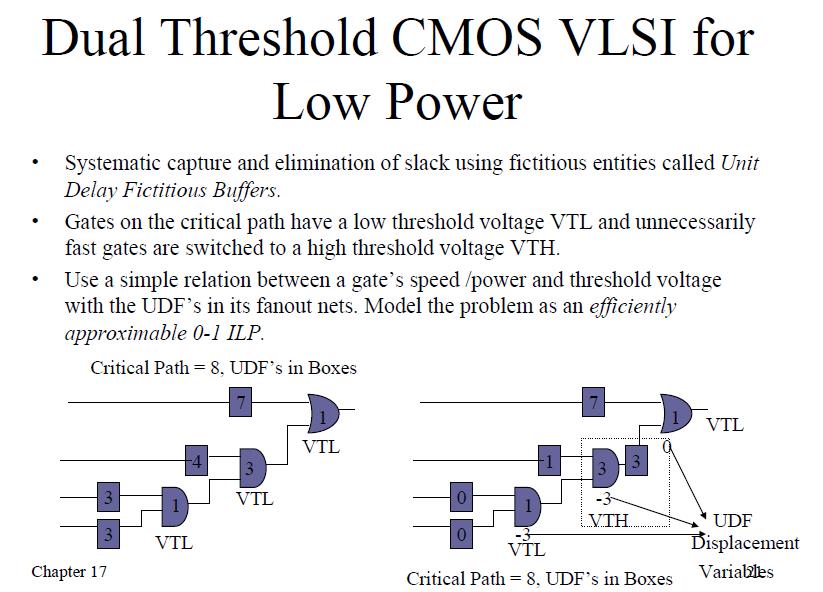

5.6 双/多 V t h V_{th} Vth

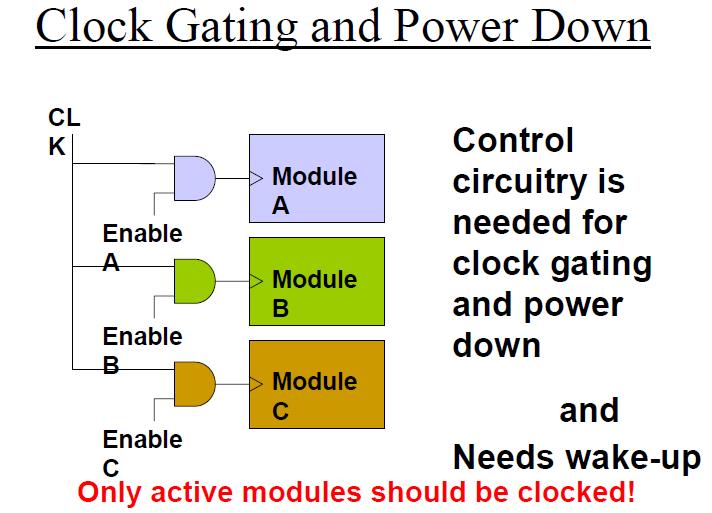

5.7 时钟

5.8 电路风格(略)

六. 功耗估计方法(略)

6.1 基于仿真的方法(略)

6.2 非仿真性方法(略)

七. 结论

以上是关于VLSI数字信号处理系统——第十七章低功耗设计的主要内容,如果未能解决你的问题,请参考以下文章