Nand flash基本原理

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Nand flash基本原理相关的知识,希望对你有一定的参考价值。

前面了解了随机存取存储器的基本原理,其主要是通过电容的充放电来保证数据的读写,当掉电后,其数据也丢失了,这节我们主要学习下flash的基本组成和原理。现在Flash在嵌入式系统中的地位和pc上的硬盘类似,用于保存系统运行所必须的系统,数据和应用层序,与内存掉电后丢失不同,它在掉点后仍可永久保存。

1. 闪存存储单元

对于闪存,我们常见的有SLC和MLC两种,细分还有eSLC和eMLC等,因为闪存式一种电压元件,因此它是以不同的电压范围来代表不同的数据,现在看看两者之间的区别。

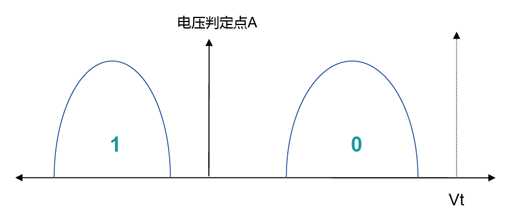

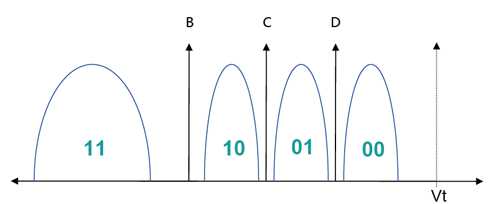

1) SLC(single-level cell):单阶存储单元,也就是闪存的每一个存储单元存储1bit的数据,存储的数据代表0还是1是基于vth的电压阈值来判定,对于闪存写入,就是对其进行充电,使得它的电压值超过电压判定点A,存储单元就表示为0(已编程),如果没有充电或者电压阈值低于A点,就表示1(已擦除)。主要针对军工,企业级应用,有着高速写入,低出错率和耐用性。

2)MLC(Multi-level cell)多阶存储单元,其是以每个存储单元存储2bit的数据,存储的数据是"00","01","10","11"也是基于电压的阈值的判定,其被分成4份。相对于SLC,MLC的每个单元是2bit,那么其容量也会大一些,同时其存储单元中存放更多的数据,那么其结构也相对复杂,出错的机会也比较大。主要针对的是消费级应用,有着高容量,低成本,使用于USB闪存,手机,数码相机等存储卡。

2. 闪存内部原理

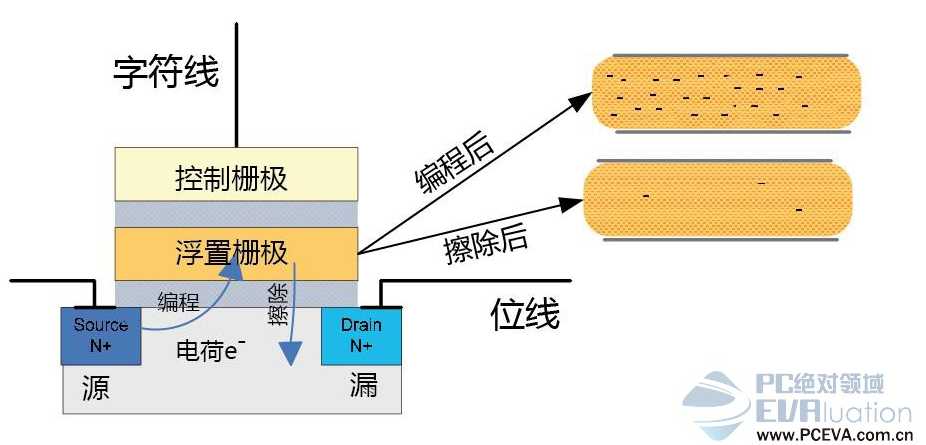

由其存储的颗粒结构,知道闪存式一种电压元件,其靠电压来存储数据,那么来看看其结构以及工作原理。闪存的内部存储结构是金属-氧化层-半导体-场效应管(MOSFET):源极,漏极和栅极,其工作原理与场效应管类似,都是电压利用控制源极和漏极之间的通断,不同的是场效应管是单栅极结构,而闪存式双栅极结构,在栅极和硅衬底之间还有一个浮置栅极,浮置栅极是有氮化物夹在二氧化硅材料之间构成。

1) 对于闪存的写入,即控制栅极去充电,对栅极加压,使得浮置栅极存储的电荷越多,超过阈值,就表示0

2) 对于闪存的擦除,即对浮置栅极进行放电,低于阈值,就表示1

理解了闪存保存数据的基本原理后,我们来针对K9F1G08X0C这款芯片来看看其硬件组成和工作原理。其管脚分布如下

| 信号名称 | 管脚名称 | 类型 | 描述 |

| 数据线 | I/O0 ~ I/O7 | INPUTS/OUTPUTS | 用来传输命令/地址/数据,仅在读操作的时候用来输出数据 |

| 命令锁存使能 | CLE | Input | CLE为高时,在WE#上升沿,命令通过I/O[7:0]锁存到命令寄存器,当不传输命令时,CLE应该为低 |

| 地址锁存使能 | ALE | Input | ALE为高时,在WE#下降沿,地址信息通过I/O[7:0]锁存片内的地址寄存器。如果传输的不是地址信息,ALE应该为低 |

| 片选 | CE# | Input | 一旦器件进入PROGRAM或ERASE操作,CE#可以变无效 |

| 读使能 | RE# | Input | |

| 写使能 | WE# | Input | 在WE#上升沿命令/地址/数据锁存 |

| 写保护 | WP# | Input | 当为低时候,所有的PROGRAM和ERASE都被禁止 |

| 准备/忙状态 | R/B | 集电极开路输出。外部需要接上拉电阻,这个脚表示芯片正在进行PROGRAM或ERASE操作。在读操作期间,表示数据正从阵列中传输到串行数据寄存器中,一旦这些操作完成,R/B#回到High-Z状态。 | |

| 电源 | VCC | ||

| 地 | VSS |

由上面来看,nandflash的外围引脚很少,没有地址线,只有数据线,相对于由数据线和地址线的norflash,大大的减少了引脚数目,使得芯片的体积更小,硬件设计也更简单。现在的数据线是复用的,也就是说既可以传数据,也可以传地址,也可以传命令,那么是怎么做到的呢?硬件为了区分当前到底是需要传啥?设计了了CLE/ALE命令,所以你必须先发一个CLE/ALE命令,告诉控制器,我现在是命令还是地址,这样就能识别并做相应的处理。我们了解了硬件的连接,那么对于flash是怎么存储的呢?下面来看看这款芯片的的存储布局

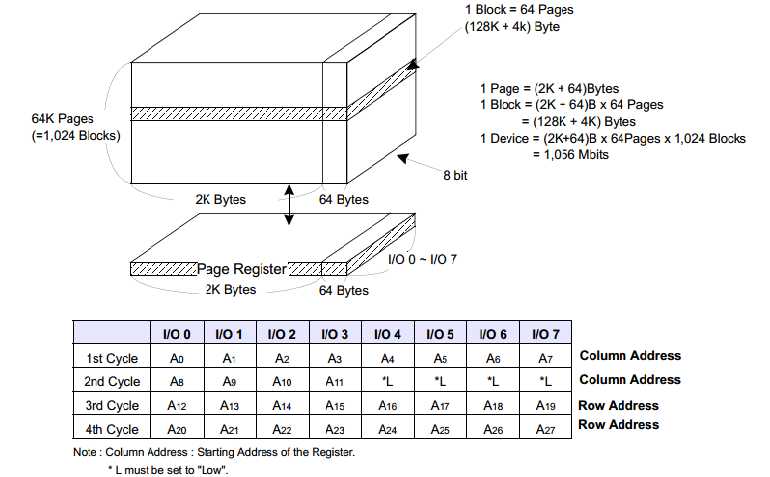

由图可以看出一片Nand flash为一个设备(device),其数据存储分层为:

1. 1个设备(device)=1024个块(Blocks),块也是Nand flash擦除操作的最小单位。

2. 1个块(block) = 64页(Pages),页是Nand flash写入的最小单位,对于每一个页,由数据块区域和空闲区域。数据区,也容易理解,就是存储一些数据,而对于空闲区,一般也叫做OOB(out of Band),这个区域,是基于Nand flash的硬件特性设计的,Nand flash在数据读写的时候很容易错误,所以为了保证数据的正确性,必须要有对应的检测和纠错的机制,此机制就被叫做ECC,所以设计了该多余的区域,用来放置数据的校验值。

3. 1个页(page) = 数据块大小(2K)+OOB块大小(64Bytes)

那么通过上面我们就可以计算出怎么访问一个物理地址:块大小*块号+页大小*页号+页内地址。

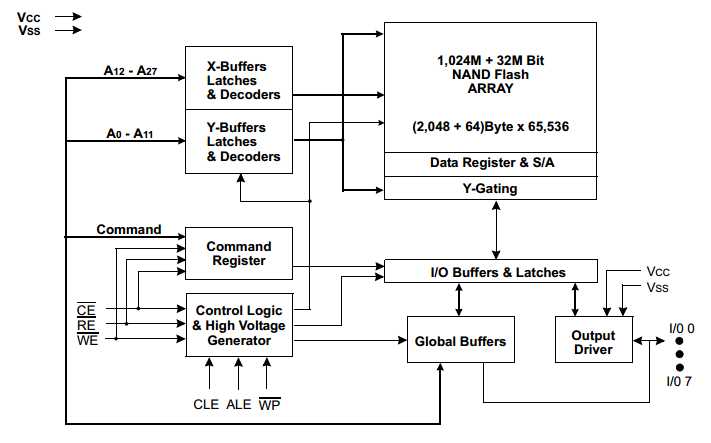

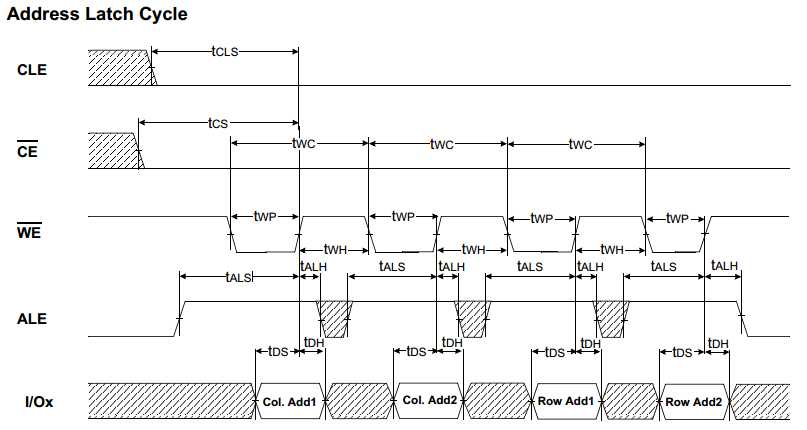

从硬件的图来看,对于K9F1G08X0C这款芯片,其容量为132MB,那么就应该需要28条地址先,而现在只有8条地址线,对于Nand flash就导入了地址周期的概念,对于该款flash,所以需要4个周期:2个列地址(Column)周期和2个行地址(ROW)周期。从下面的功能框图来看,对于列地址A0--A11,就是页内地址,地址范围就是0--4094,与页内地址(2K+64)吻合,其实对于页内地址,其实只需要A0-A10,而对于多出来的A11,是用来表示页内的oob区域。那么对于A12-A27就是用来表示属于哪一个块和块里面的哪一个页号。

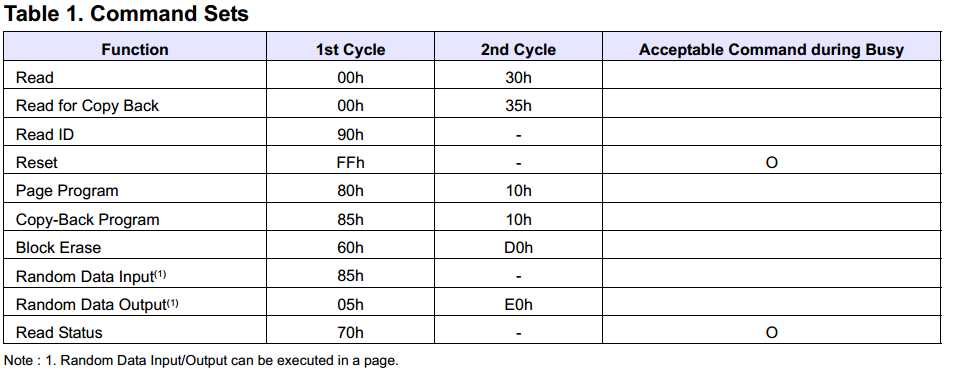

通过前面对于nand flash的基本原理的讲解,下面来看看怎么操作nand flash,下面是K9F1G08X0C支持的命令格式。

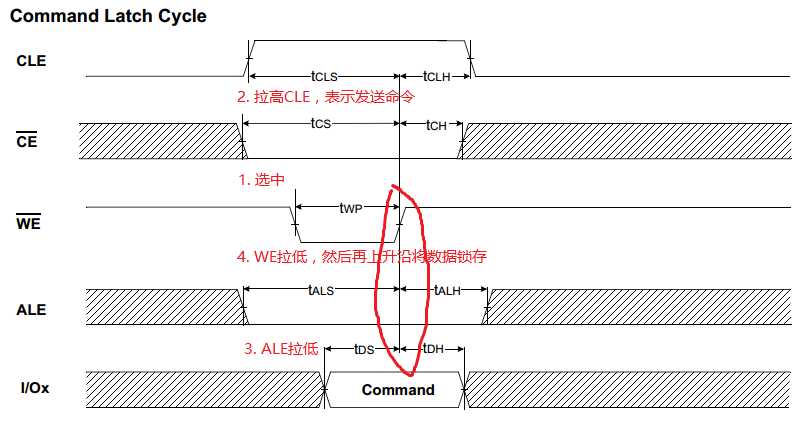

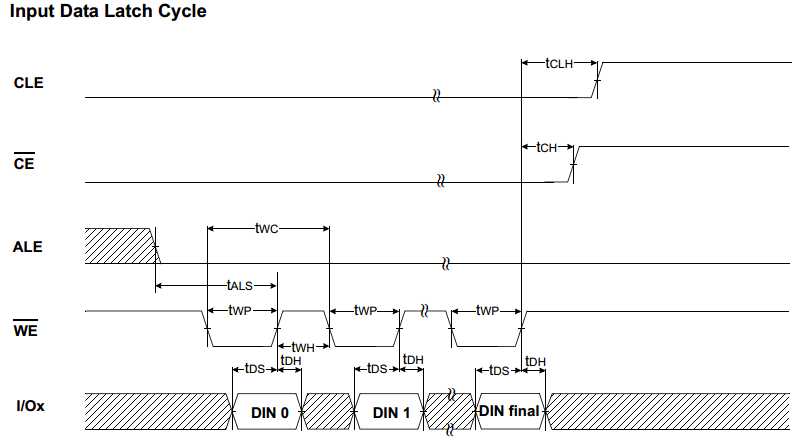

下图是发送一个命令/地址/数据的完整过程

通过时序图看出,上面有很多时间参数,在设置Nand flash控制器的时候,需要确认这些时间参数是否在合适的范围内,对于控制命令都是通过上面的几个基础命令组合而来,此时对于nand flash的基本控制方式和原理已经介绍完。

以上是关于Nand flash基本原理的主要内容,如果未能解决你的问题,请参考以下文章