MIPI DSI

Posted craze-ic

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了MIPI DSI相关的知识,希望对你有一定的参考价值。

MIPI DSI是什么?

MIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。MIPI(移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准,常用到的是DSI(显示接口)和CSI(摄像接口)。

嗯~MIPI DSI是一种用于显示的接口。小分辨率的都是并口,随着分辨率越做越高,速度越来越快,并口就不能满足需求了。因此出现了LVDS接口和MIPI DSI。

DSI初了解

MIPI官网链接:https://mipi.org/specifications/dsi-2 里面有所有的DSI,CSI,D-PHY等协议

打开DSI的SPEC,170多页

先看看introduction

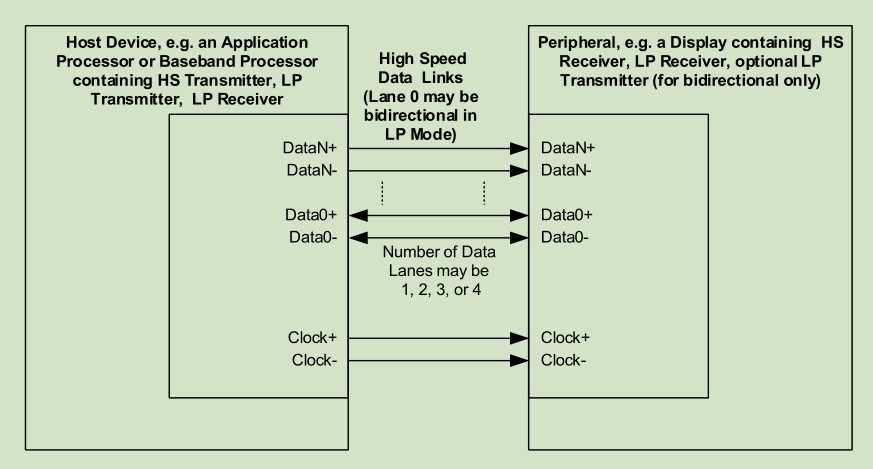

接口是4对数据差分信号和1对时钟差分信号,4条数据lane和1条datalane,第0条lane是双向的,其他lane是从发送到接收。

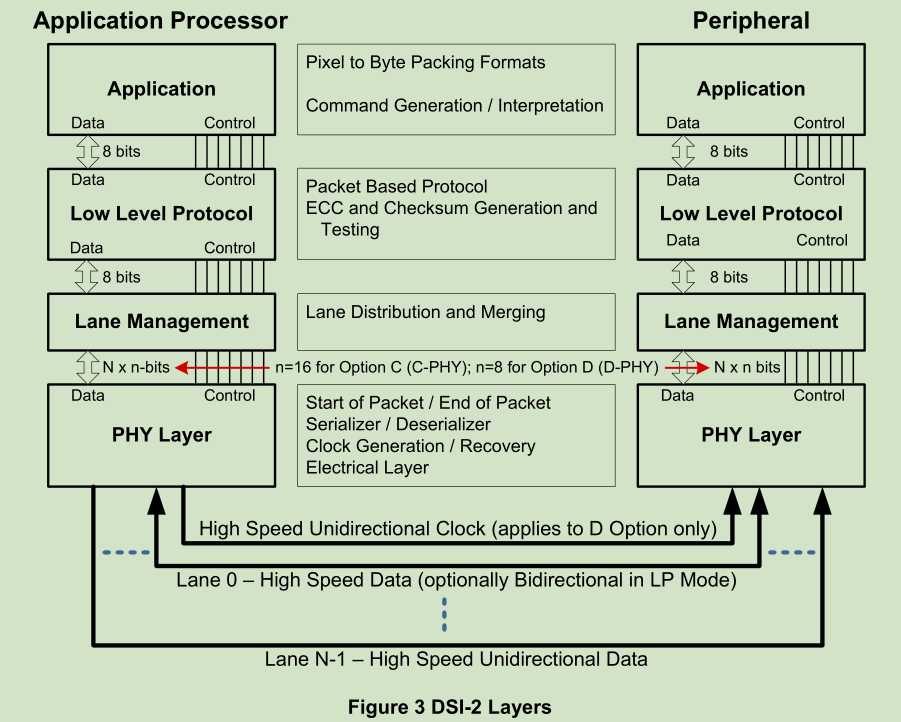

和很多高速串行接口一样(USB,SATA,PCIE),它们都是分层设计,大同小异。DSI如上图分为4层架构,Application属于上层架构,软件搞的;硬件需要搞的是下面3层:

PHY layer:物理层,定义传输媒介,包含高速串行接口,并串转换,时钟产生,组包;这部分的工作主要是模拟设计。

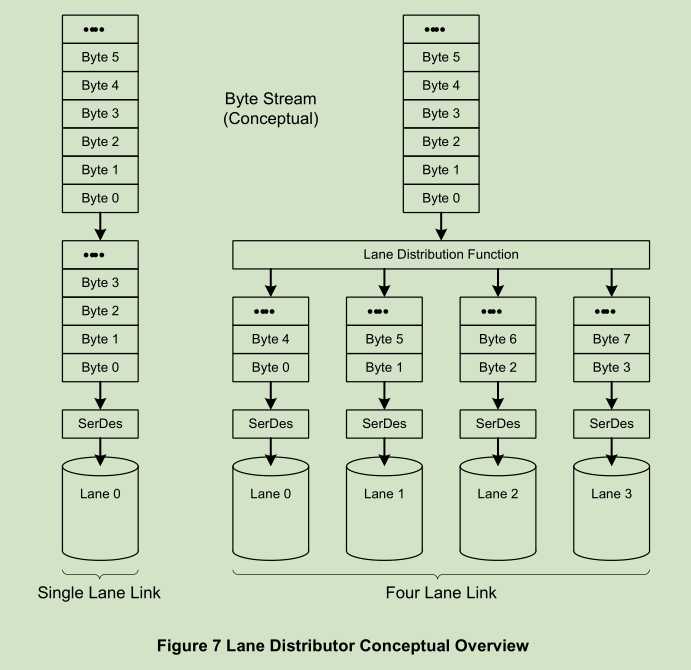

Lane management:lane管理,将数据流按照顺序依次分发到每条lane上。

Low level protocol;按照DSI协议指定数据组包方式,定义包头等相关内容,生成ECC,校验码等。

DSI的模式有command mode和video mode,

command mode下dsi以命令的方式发送命令和数据到具有现实缓存的控制器。寄存器配置,参数,帧数据等,这种模式下也可以读屏的信息等

video mode:这种模式是最常用的模式,从主机传输视频数据,这种模式以高速传输,为了减少复杂性和节约成本只采用video模式的系统只有一个单向数据路径。

接下来就逐层学习下

DSI Physical layer(D-PHY)

HS : 高速模式下传输视频数据,80Mbps~1Gbps/lane

LPS:Low-Power State,低功耗模式,用于控制:10Mhz(max)

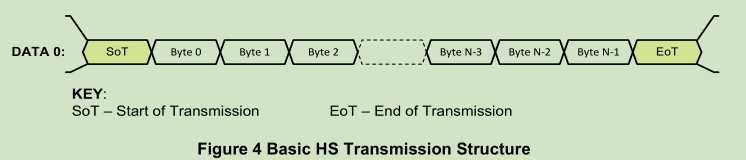

D-PHY低层协议规定最小的数据单元是一个字节,发送数据必须低位在前,高位在后。

D-PHY可能包含:

低功耗发送器(LP-TX)

低功耗接收器(LP-RX)

高速发送器(HS-TX)

高速接收器(HS-RX)

低功耗竞争检测器(LP-CD)

如果做host和屏对接,可以只有TX

lane状态和电压

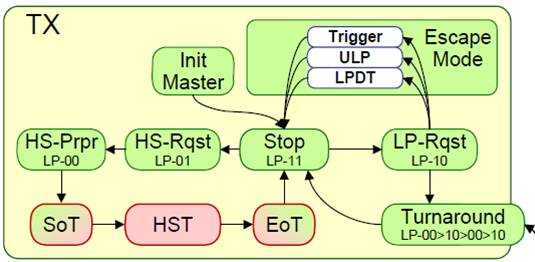

LP-00,LP-01,LP-10,LP-11(单端)

HS-0,HS-1(差分)

lane电压(典型)

LP:0-1.2v HS:100-300mv(200mv)

进入高速模式过程:LP11->LP01->LP00->SOT(00011101)->HSD(80Mbps->1Gbps)

退出高速模式过程:EOT->LP11

多条lane分发

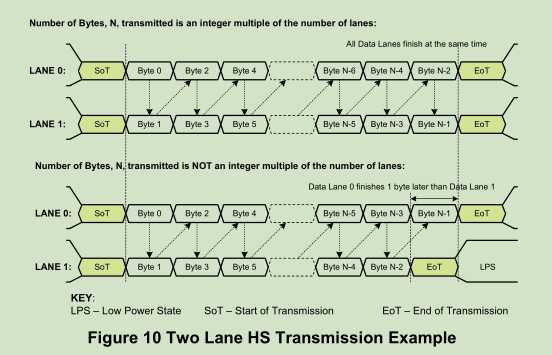

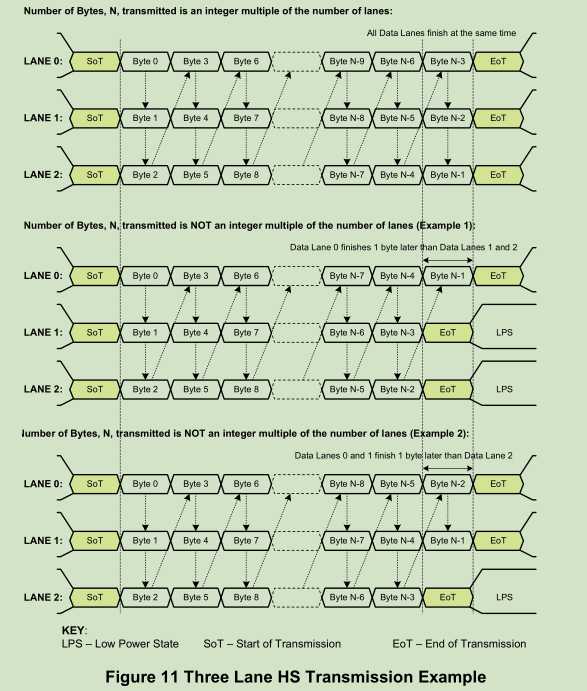

如果byte数和lane非对齐

2lane对齐传输和非对齐传输下EOT的发送如下图:

3lane对齐传输和非对齐传输下EOT的发送如下图所示:

MIPI是怎样组包,包的格式是什么样的呢?

DSI以包(packet)的方式封装进行传输的,帧类型有:

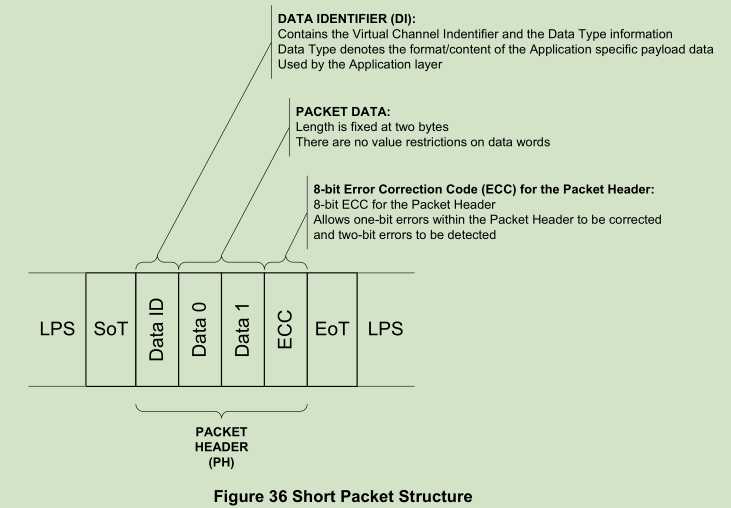

短帧:4bytes(固定)

长帧:6-65541bytes(可变)

短帧结构(4个字节)

数据标识(DI)1个字节

帧数据:data0,Data1,两个字节,表示要传输的数据

ECC:1个字节,误差校验码

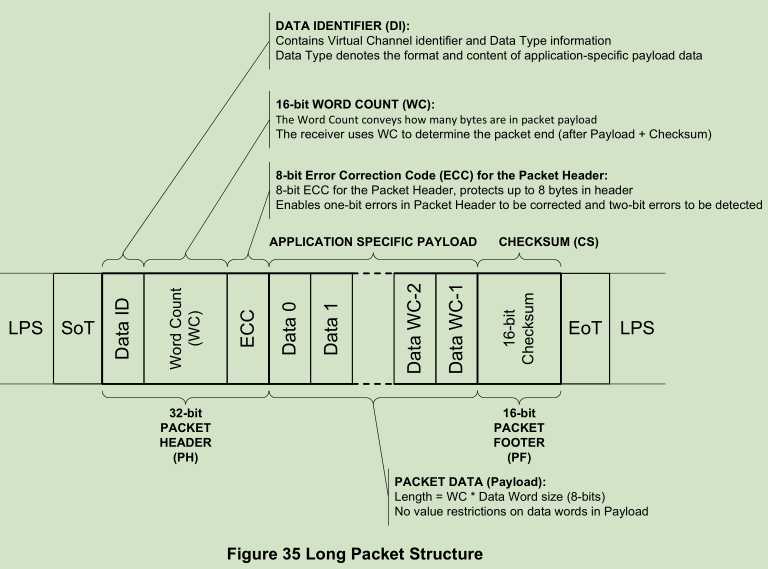

长帧结构

DI:数据标识符

WC:word count,两个字节,包中有效负载长度

ECC:一个字节,误差校正码

Data:有效负载

Checksum:2个字节校验码

以上是关于MIPI DSI的主要内容,如果未能解决你的问题,请参考以下文章