s3c2440裸机编程-时钟编程(配置时钟寄存器)

Posted fuzidage

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了s3c2440裸机编程-时钟编程(配置时钟寄存器)相关的知识,希望对你有一定的参考价值。

s3c2440裸机编程-时钟编程(二、配置时钟寄存器)

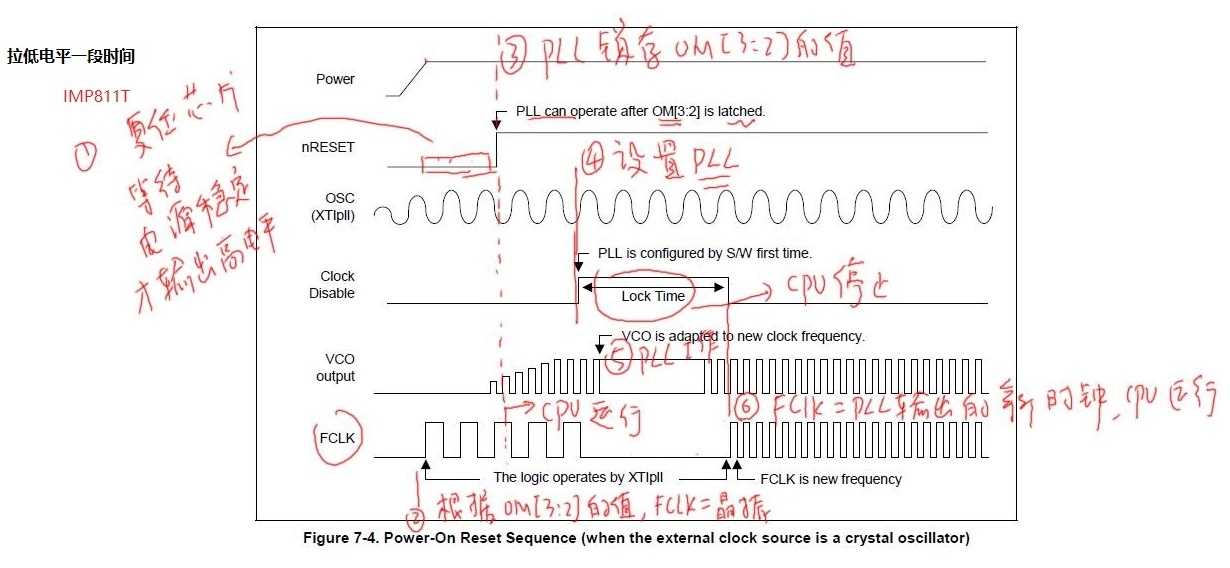

1.2440时钟时序

下图是2440时钟配置时序:

1.上电后,nRESET复位信号拉低,此时cpu还无法取指令工作。

2.nRESET复位信号结束后变为高电平,此时cpu开始工作。此时cpu主频FCLK=osc。

3.此时可以配置PLL,经过lock time后,FCLK倍频成新的时钟。

2.如何配置时钟

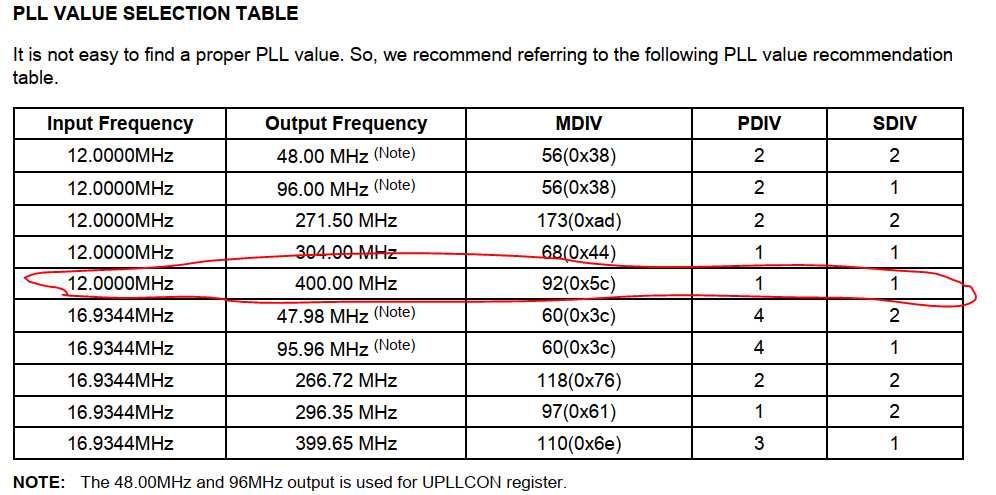

在参考手册的特性里介绍了S3C2440的工作频率,Fclk最高400MHz,Hclk最高136MHz,Pclk最高68MHz。那么 我们干脆配置FCLK:HCLK:PCLK= 400:100:50 (MHz).

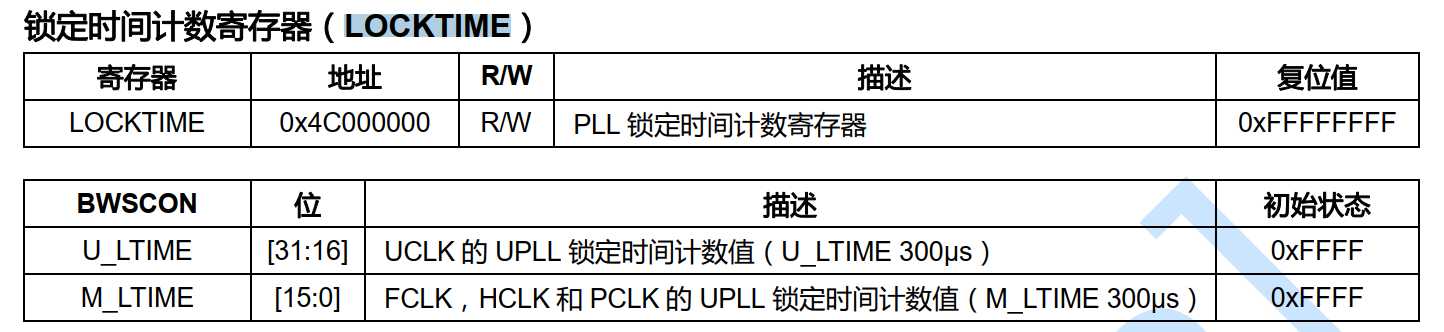

1,先配置lock time

我们取芯片手册上的推荐值。

/* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

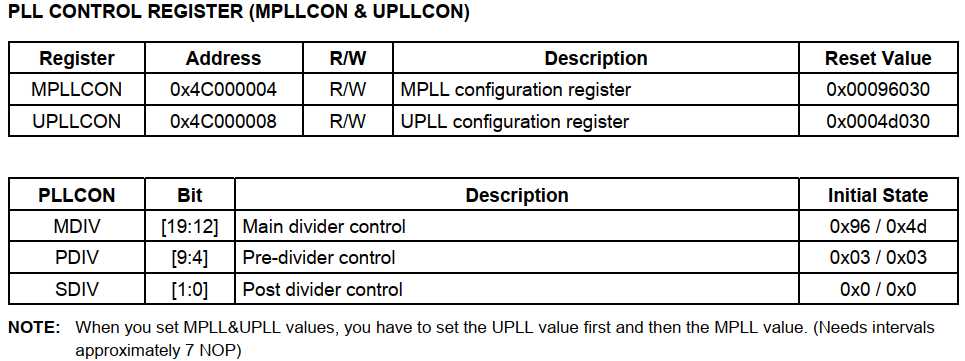

str r1, [r0]2,配置MPLL得到FCLK

也可参考配置表取值

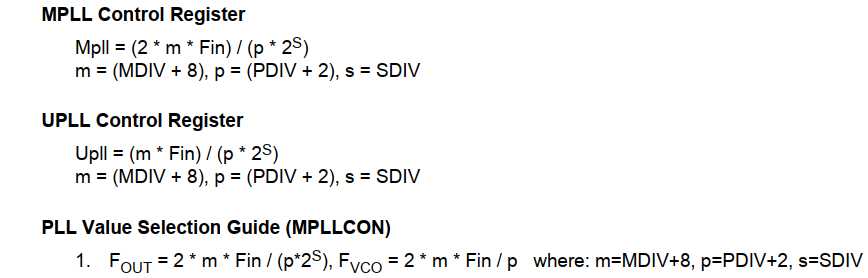

/*

** MPLL(FCLK) = 2*m*Fin/(p*2^s)

** 不妨取:

** m = MDIV+8 = 92+8=100

** p = PDIV+2 = 1+2 = 3

** s = SDIV = 1

** 则:

** FCLK= 2*100*12/(3*2^1)=400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12)|(1<<4)|(1<<0)

str r1, [r0]注意:如果也要配置了UPLL,那么先配置UPLL,要个7个NOP后才能再配置MPLL.

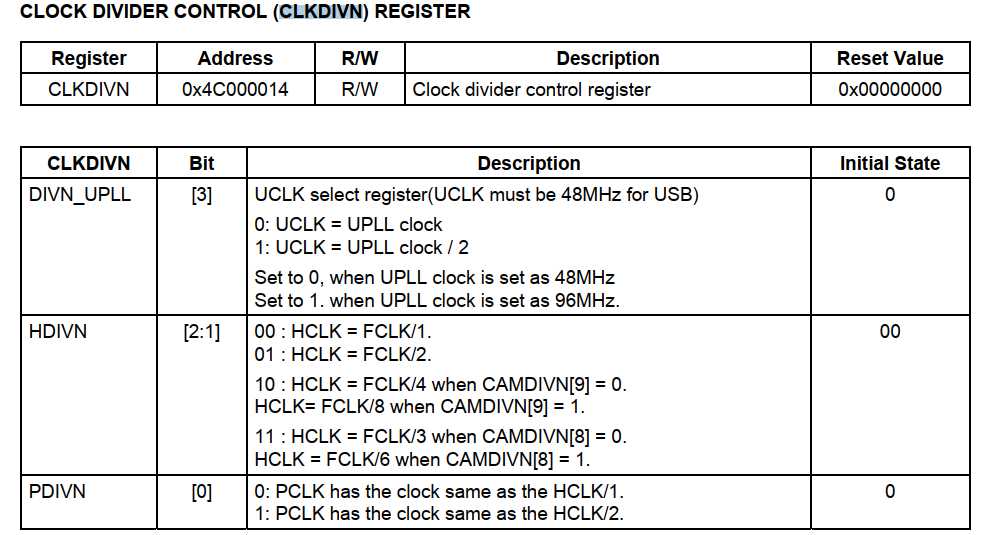

3,配置CLKDIVN得到HCLK,PCLK

/* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]注意:如果HDIV设置为非0,CPU的总线模式要进行改变,默认情况下FCLK = HCLK,CPU工作在fast bus mode快速总线模式下,HDIV设置为非0后, FCLK与HCLK不再相等,要将CPU改为asynchronous bus mod异步总线模式.

/* 设置CPU工作于异步模式 */

mrc p15, 0, r1, c1, c0, 0 ??????? /* 读取CP15 C1寄存器 */?

orr r1, r1, #0xc0000000 ??????? /* 设置CPU总线模式 */?

mcr p15, 0, r1, c1, c0, 0 ??????? /* 写回CP15 C1寄存器 */完整代码如下:

.text

.global _start

_start:

/* 关闭看门狗 */

ldr r0, =0x53000000

ldr r1, =0

str r1, [r0]

/* 设置MPLL, FCLK : HCLK : PCLK = 400m : 100m : 50m */

/* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 设置CPU工作于异步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

/* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

* m = MDIV+8 = 92+8=100

* p = PDIV+2 = 1+2 = 3

* s = SDIV = 1

* FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12)|(1<<4)|(1<<0)

str r1, [r0]

/* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定

* 然后CPU工作于新的频率FCLK

*/

/* 设置内存: sp 栈 */

/* 分辨是nor/nand启动

* 写0到0地址, 再读出来

* 如果得到0, 表示0地址上的内容被修改了, 它对应ram, 这就是nand启动

* 否则就是nor启动

*/

mov r1, #0

ldr r0, [r1] /* 读出原来的值备份 */

str r1, [r1] /* 0->[0] */

ldr r2, [r1] /* r2=[0] */

cmp r1, r2

ldr sp, =0x40000000+4096

moveq sp, #4096 /* r1=r2, nand启动,修改栈指针=4096(此时sram对应0地址) */

streq r0, [r1] /* 恢复原来的值 */

bl main

halt:

b halt以上是关于s3c2440裸机编程-时钟编程(配置时钟寄存器)的主要内容,如果未能解决你的问题,请参考以下文章