AMBA基础知识5:burst & 读写response

Posted Times_poem

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了AMBA基础知识5:burst & 读写response相关的知识,希望对你有一定的参考价值。

来自:https://blog.csdn.net/u014395662/article/details/79669378?utm_source=blogxgwz6

复习:

AXI协议中用到的一些术语

AXI Transaction:the complete set of required operations on the AXI bus form the AXI Transaction

AXI Burst:any required payload data is transferred as an AXI Burst

AXI Beats:a burst can comprise multiple data transfers, or AXI Beats

简单来说,AXI Transaction就是传输一段数据(AXI burst)所需要的一整套操作,而AXI burst就是待传数据,AXI burst由AXI Beats组成,一个Beat就是一个transfer。

基于burst的传输

每个AXI transaction的传输都是基于burst的,协议关于burst的类型规定如下:

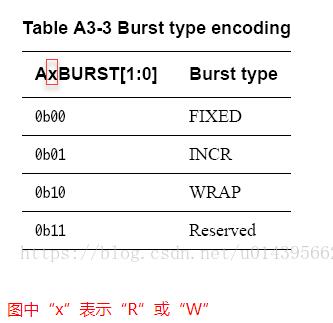

★Burst类型

▼FIXED:burst中的每个transfer都使用相同的地址

▼INCR:burst中的每个transfer的地址在上一个transfer的基础上递增

▼WRAP:与INCR burst类似,只是地址会卷绕(就是增加到某个地址后又回到最低地址)

★每个burst开始于控制信息和指向第一个字节的地址的传输(由Master发给Slave)

★每个burst不能超过4KB地址边界

★burst length

▼(AxLEN[7:0])是读/写burst的长度字段

▼ARLEN[7:0]:读

▼AWLEN[7:0]:写

▼Burst_Length = AxLEN[7:0]+1;

★INCR型的burst支持的长度为1到256,其它类型的burst长度必须保持在1到16

★WRAP burst的长度必须是2,4,8,16

★一旦burst长度一定,它就不能提前被Master或Slave终止。

★INCR burst或者长度超过16的burst可以被转换为较小的burst,即便transaction attributes指明该transaction是Non-modifiable也可以这么做。

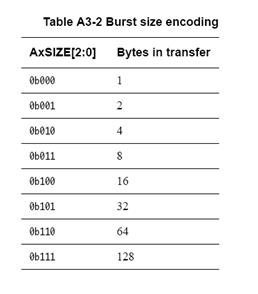

★burst size

▼(AxSIZE[2:0]):每个beat,或者说data transfer的字节数

▼ARSIZE[2:0] for read

▼AWSIZE[2:0] for write

★若总线宽度比burstsize更宽,那么AXI接口就必须根据传输地址将数据在总线上排列好

★burst size不能超过总线宽度

★burst address

◆Start_Address:由Master决定,每个burst第一个transfer的地址

◆Number_Bytes = burst size

◆Data_Bus_Bytes:总线宽度/8

◆Aligned_Address:Start_Address@ Number_Bytes

“A@B”表示A按照B对齐,也就是

A@B =(INT(A/B))*B

◆Burst_Length = AxLEN[7:0]+1

◆Address_N:burst中第N个transfer的地址,N从1开始;

◆Wrap_Boundary:在Wrap burst中的最低地址,必须按(Burst_length*Number_Bytes)对齐

★Write Strobe

◆WSTRB[n:0]:若WSTRB[n]是高,则说明WDATA[8n+7:8n]是有效的

◆当WVALID是低的时候,WSTRB可以为任意值,建议全部为低或者保持它原来的值

★Unaligned transfers

◆当burst address中的Aligned_Address != Start_Address的时候,即为unaligned transfer,这时,用write strobe来标明从Aligned_Address到Start_Address的无效字节

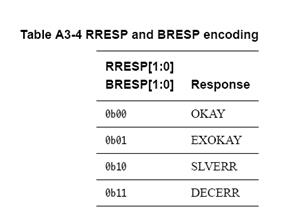

★读与写响应信号

◆信号:RRESP[1:0]和BRESP[1:0]

◆responses:

▼OKAY: Normal access success + Exclusive access failed

▼EXOKAY: Exclusive access okay

▼SLVERR: Slave error

Slave error conditions:

◆FIFO满或空

◆transfer size 不支持

◆向只读设备写

◆Slave timeout

◆access to a disabled or powered-down function

▼DECERR: Decode error

◆interconnect不能成功对Slave access译码

◆这种情况下,会access一个缺省Slave,由缺省Slave回应DECERR

!AXI协议要求transaction中所有的transfer都必须完成,即便出现了error condition,给出DECERR的default Component也必须满足这个要求。

▼BRESP和RRESP的编码:

◆在写transaction中,对于整个burst,Slave只用回应一个BRESP

◆在读transaction中,Slave可以对burst中的不同transfer回应不同的RRESP

以上是关于AMBA基础知识5:burst & 读写response的主要内容,如果未能解决你的问题,请参考以下文章