基于FPGA的远程升级系统概述

Posted fpga和matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于FPGA的远程升级系统概述相关的知识,希望对你有一定的参考价值。

目录

作者ID :fpga和matlab

CSDN主页:https://blog.csdn.net/ccsss22?type=blog

擅长技术:

1.无线基带,无线图传,编解码

2.机器视觉,图像处理,三维重建

3.人工智能,深度学习

4.智能控制,智能优化

5.其他一、理论基础

通过串口接收升级文件,将升级文件写入EPCS中,然后使用Remote_system_update模块进行升级操作。

存储器类型使用片上RAM,约20KB空间

使用的芯片是EP4CE40F23C6

这里,主要的核心部分是基于NIOSII的Remote system update模块的调用,这里在设计说明中,重点介绍一下Remote system update模块的使用方法。

RSU单元主要包括如下几个部分:

第一:页模式的选择

通过页模式选择特性,我们可以选择重配置期间时加载不同的配置程序。在FPGA芯片中,通过PGM[2:0]三个引脚来实现页选择。

第二:工厂配置

工厂配置就是系统的默认配置,当使用增强配置期间的时候,工厂配置会存放在000页。当使用串行配置器件的时候,工作配置则被放在从0X00000000地址开始的空间。工厂配置值能被系统生产商第一次配置进去,静止用户通过远程升级模式进行修改。

第三,应用配置

从远程接收到的配置数据,并存放到远程存储器里除工厂配置的其他的任意的空间。

第四,看门狗计数器

主要用来进行复位计数的功能。

第五,远程程序升级子模块

远程程序升级子模块管理着远程配置特性,这个字模块是由一个远程配置状态机来实现的。

第六,远程配置寄存器

远程配置寄存器主要用在存储配置地址以及引起重配置的错误类型。

系统的设计。

二、核心程序

第一,基于NIOSII的RSU单元模块设计

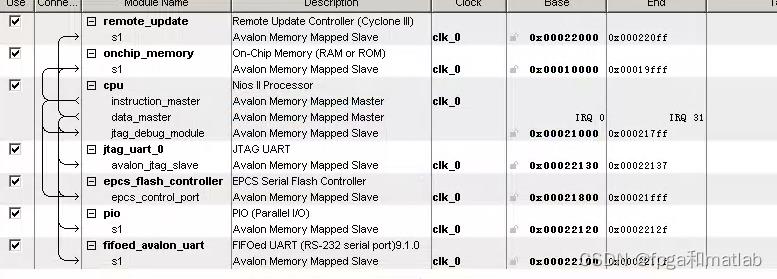

在SOPC界面中,做如下的IP核总线连接:

从上面的设置可以看到,整个NiosII系统,主要包括CPU核,片上RAM以及UART串口模块三个部分。

这些模块的参数设置以及地址分配分别如下所示:

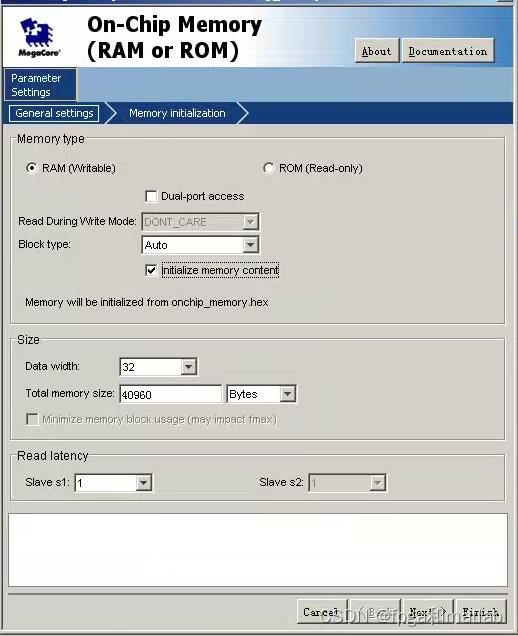

片上RAM:

注意,片上存储器的总大小这里设置为40960,当然你也可以改为你所要求的大小。

UART串口:

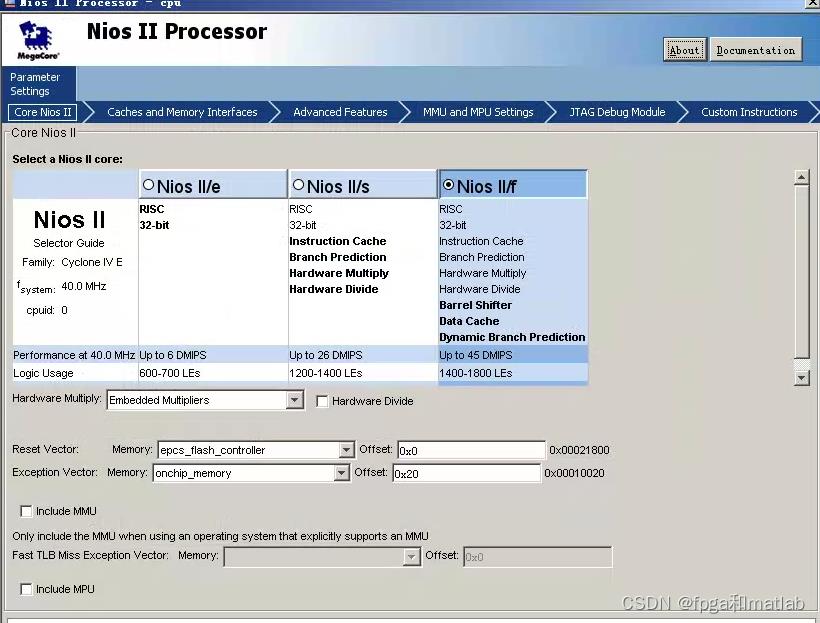

CPU核:

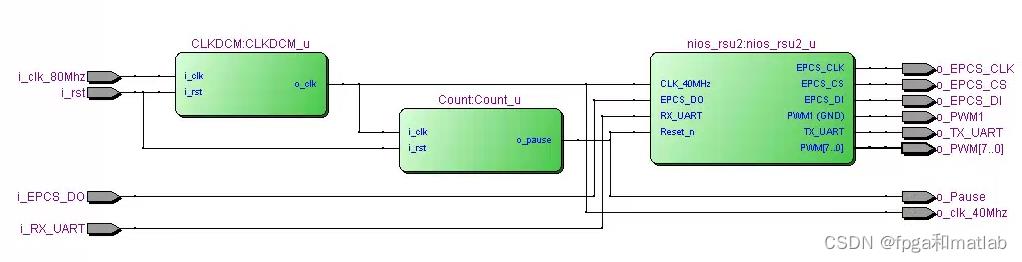

第二,系统整体设计

整个系统的结构如下所示:

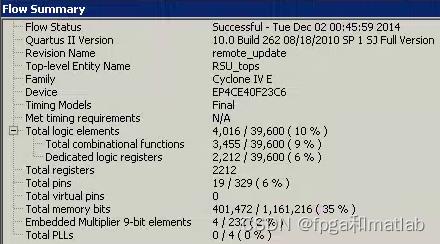

整个系统的资源占用如下所示:

`timescale 1 ns / 1 ps

module RSU_tops(

i_clk_80Mhz,

i_rst,

i_EPCS_DO,

i_RX_UART,

o_clk_40Mhz,

o_Pause,

o_TX_UART,

o_EPCS_CS,

o_EPCS_DI,

o_EPCS_CLK,

o_PWM,

o_PWM1,

o_LED1,

o_LED2

);

input i_clk_80Mhz;

input i_rst;

input i_EPCS_DO;

input i_RX_UART;

output o_clk_40Mhz;

output o_Pause;

output o_TX_UART;

output o_EPCS_CS;

output o_EPCS_DI;

output o_EPCS_CLK;

output [7:0]o_PWM;

output o_PWM1;

output o_LED1;

output o_LED2;

CLKDCM CLKDCM_u(

.i_clk (i_clk_80Mhz),

.i_rst (i_rst),

.o_clk (o_clk_40Mhz)

);

Count Count_u(

.i_clk (o_clk_40Mhz),

.i_rst (i_rst),

.o_pause (o_Pause)

);

nios_rsu2 nios_rsu2_u(

.EPCS_DO (i_EPCS_DO),

.RX_UART (i_RX_UART),

.CLK_40MHz (o_clk_40Mhz),

.Reset_n (o_Pause),

.TX_UART (o_TX_UART),

.EPCS_CS (o_EPCS_CS),

.EPCS_DI (o_EPCS_DI),

.EPCS_CLK (o_EPCS_CLK),

.PWM (o_PWM),

.PWM1 (o_PWM1),

.led1 (o_LED1),

.led2 (o_LED2)

);

endmodule `timescale 1 ns / 1 ps

module nios_rsu2(

EPCS_DO,

RX_UART,

CLK_40MHz,

Reset_n,

TX_UART,

EPCS_CS,

EPCS_DI,

EPCS_CLK,

PWM,

PWM1,

led1,

led2

);

input wire EPCS_DO;

input wire RX_UART;

input wire CLK_40MHz;

input wire Reset_n;

output wire TX_UART;

output wire EPCS_CS;

output wire EPCS_DI;

output wire EPCS_CLK;

output wire [7:0] PWM;

output wire PWM1;

output reg led1;

output reg led2;

Remote_NIOS b2v_inst(

.clk_0(CLK_40MHz),

.reset_n(Reset_n),

.data0_to_the_epcs_flash_controller(EPCS_DO),

.rxd_to_the_fifoed_avalon_uart(RX_UART),

.dclk_from_the_epcs_flash_controller(EPCS_CLK),

.sce_from_the_epcs_flash_controller(EPCS_CS),

.sdo_from_the_epcs_flash_controller(EPCS_DI),

.txd_from_the_fifoed_avalon_uart(TX_UART),

.out_port_from_the_pio(PWM));

assign PWM1 = 1'b0;

wire sel;

assign sel = EPCS_CS;

always @(posedge CLK_40MHz or posedge Reset_n)

begin

if(Reset_n)

begin

led1 <= 1'b0;

led2 <= 1'b0;

end

else begin

if(sel == 1'b1)

begin

led1 <= 1'b0;

led2 <= 1'b1;

end

else begin

led1 <= 1'b1;

led2 <= 1'b0;

end

end

end

endmodule

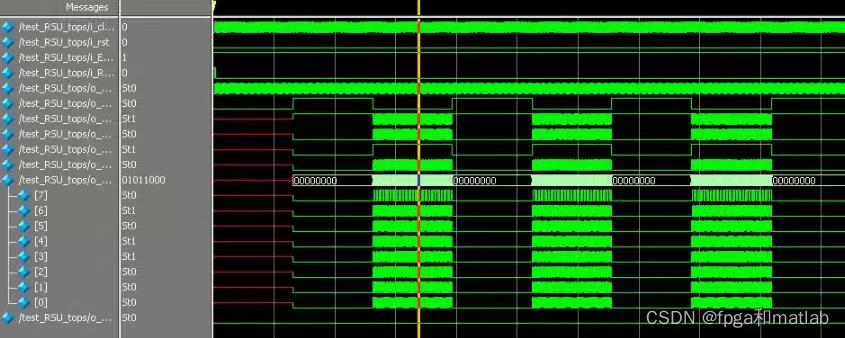

三、仿真测试结果

这里,仿真效果如下图所示:

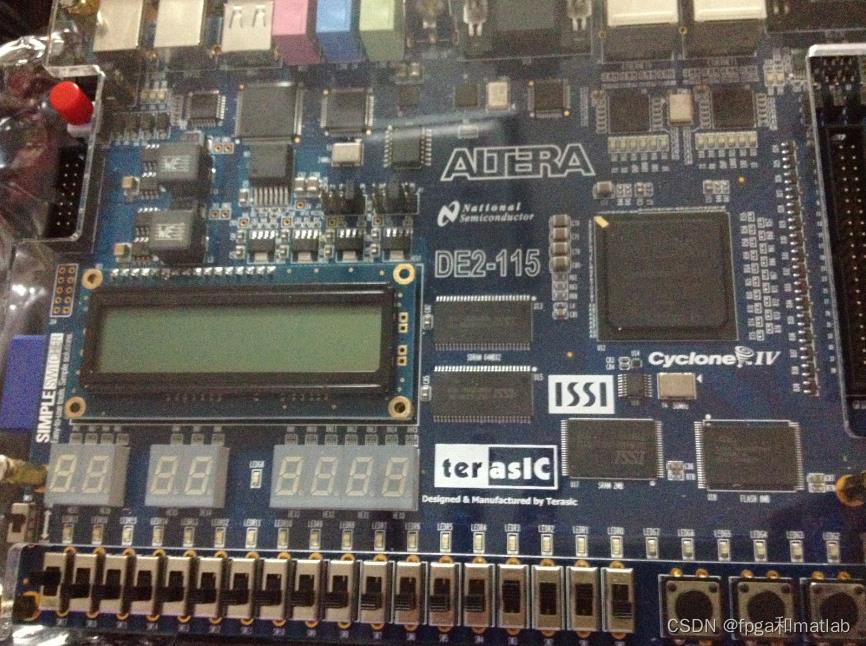

然后我这里下面的测试步骤都是基于这个板子来做的测试,测试步骤:

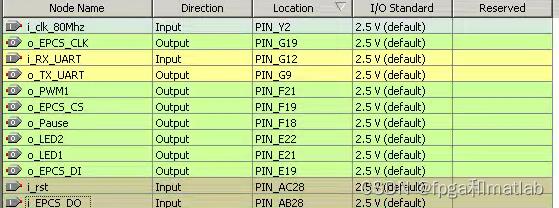

管脚的绑定截图:

然后,我们这里主要观察的是LED1和LED2两个灯的工作情况。这里,我再我的板子上连接的两个绿色的LED灯。

A12-23

以上是关于基于FPGA的远程升级系统概述的主要内容,如果未能解决你的问题,请参考以下文章