STA基础chapter3

Posted zhanghaha-zzz

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了STA基础chapter3相关的知识,希望对你有一定的参考价值。

标准单元库

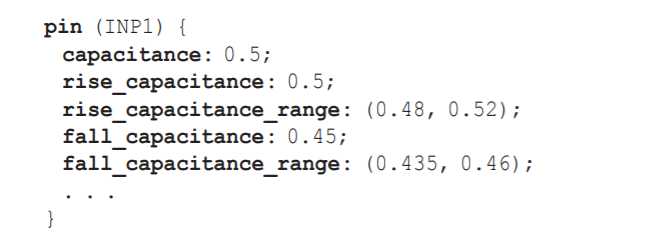

3.1引脚电容

大多数情况下,只为输入引脚指定电容,输出引脚电容为0(工艺库中确实如此)。

下图,单位pF。

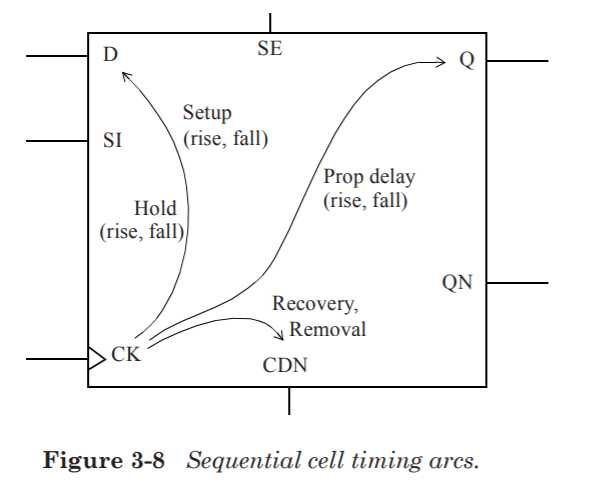

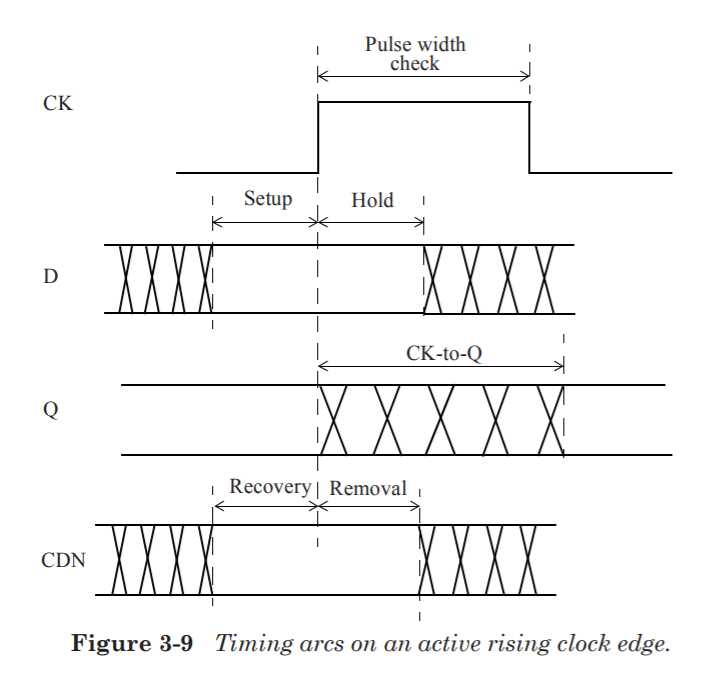

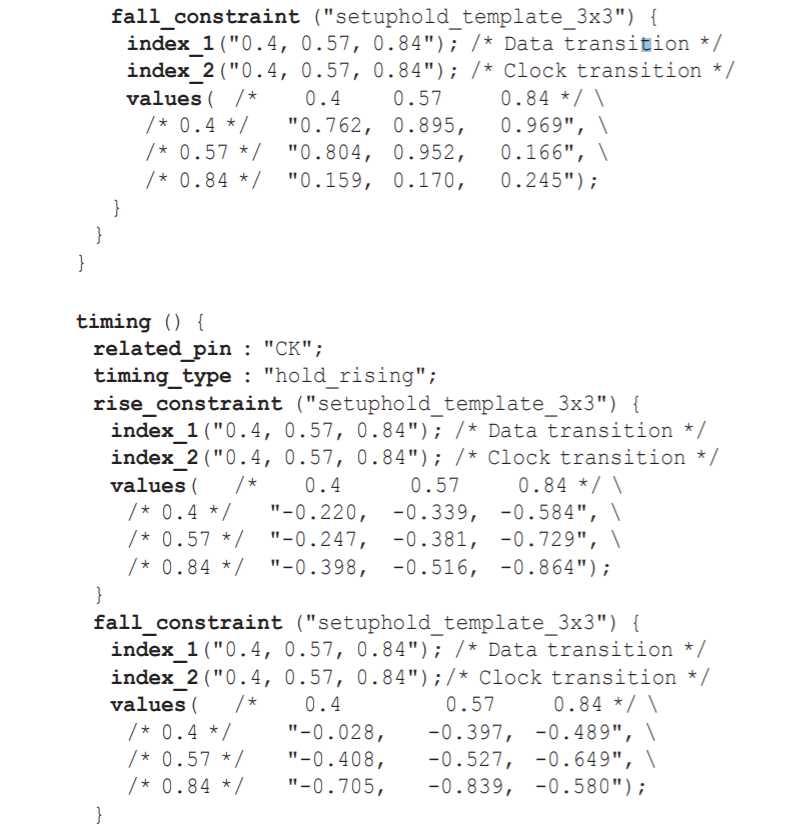

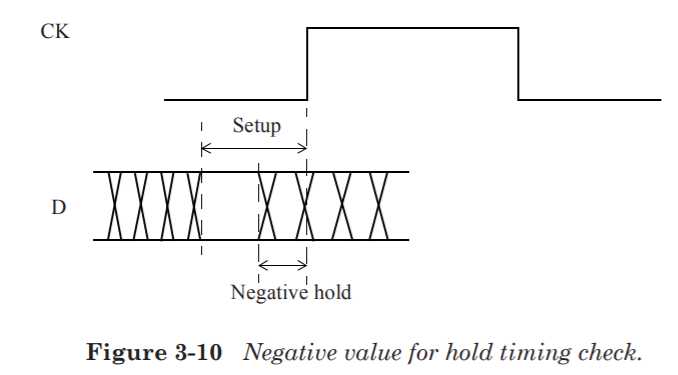

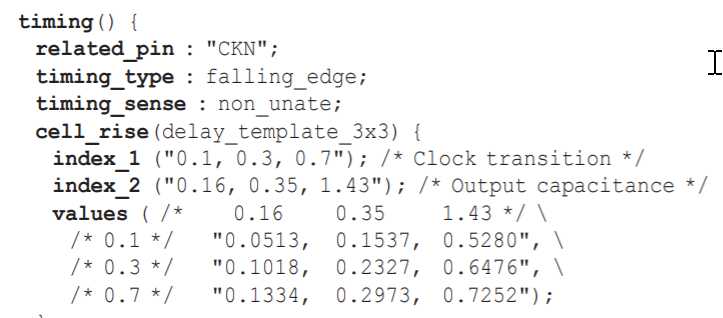

3.2 时序模型

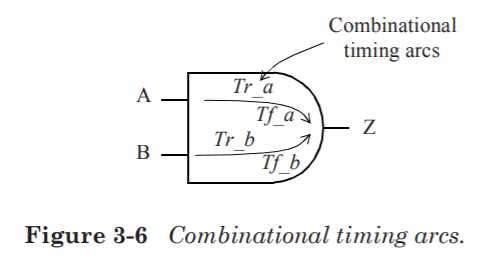

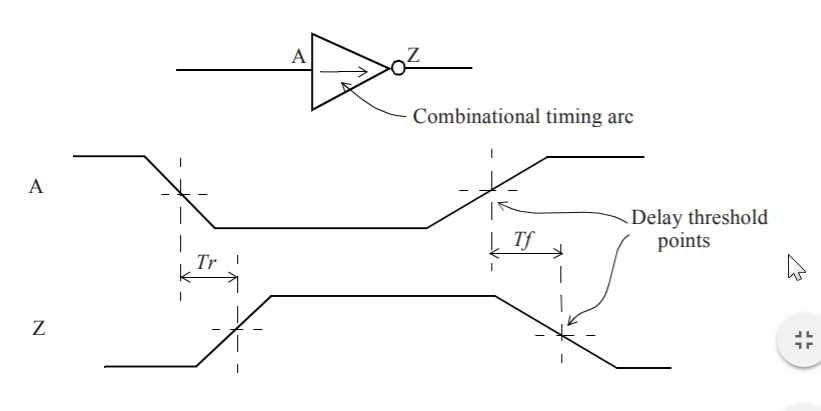

输出上升延时rise delay和输出下降延时:

延迟值与负载电容大小直接相关,电容越大延时越大。在大多数情况下延时随着输入传播延时(过渡时间)的增加而增加。有几种情况下,输入阈值(用于测量延时)与单元内部开关节点有很大不同。通过单元的延时可能表现出相对于过渡时间的非单调行为——较大的过渡时间可能可能会产生较小的延时,特别是负载较小时。

3.2.1线性时序模型

3.2.2非线性延时模型NLDM

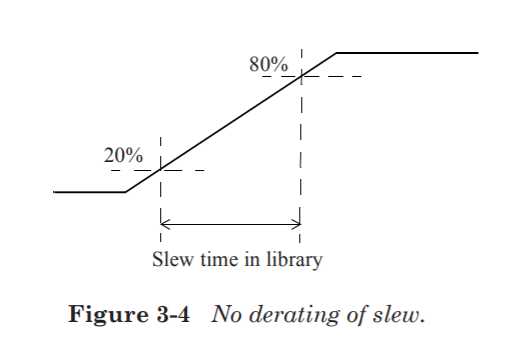

slew:

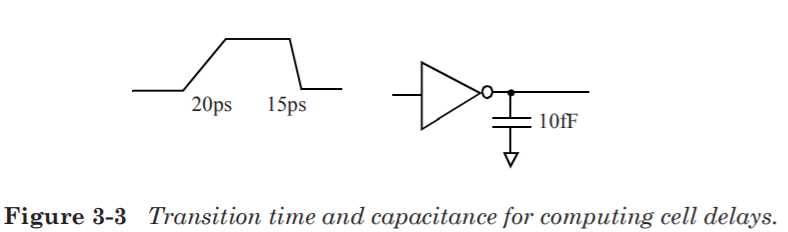

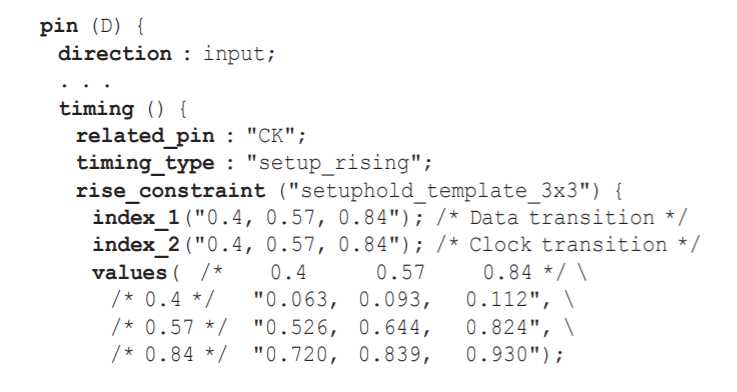

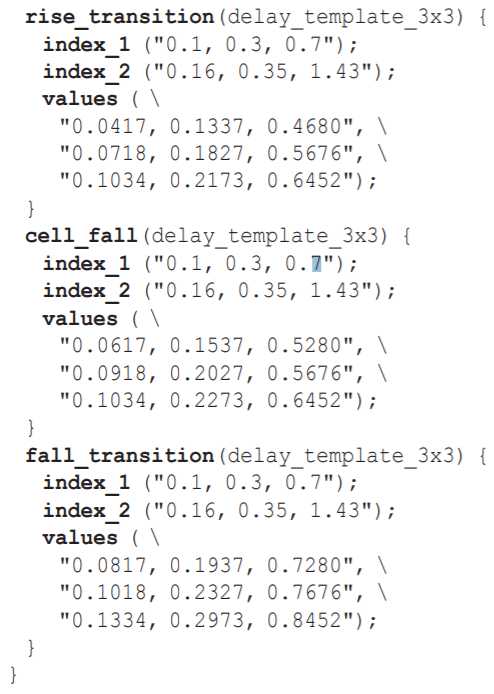

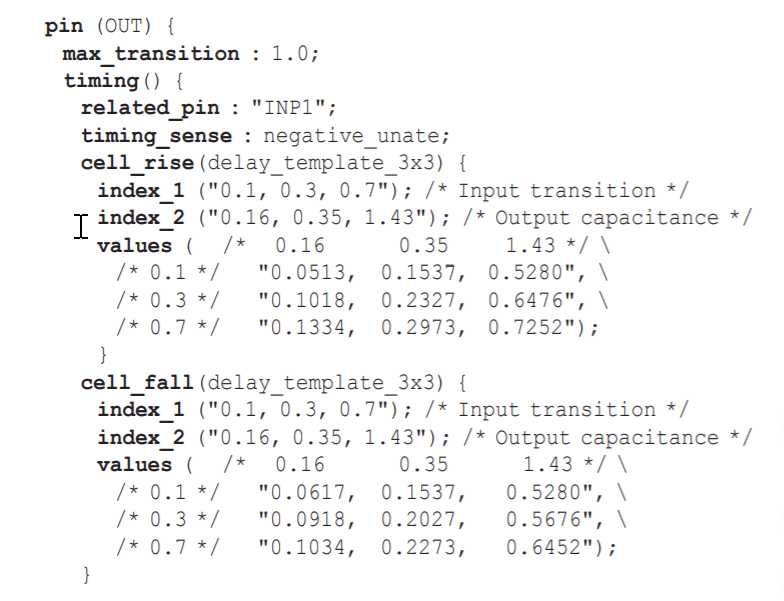

延时表现为以输入过渡延时,输出负载为独立变量的table:

上面描述的是输出引脚的延时,table包含了从INP1到OUT的上升和下降延时模型,和OUT引脚的最大过渡。

关于transition time:

以上是关于STA基础chapter3的主要内容,如果未能解决你的问题,请参考以下文章

收录近500篇文章|学习路线|基础知识|接口|总线|脚本语言|芯片求职|安全|EDA|工具|低功耗设计|Verilog|低功耗|STA|设计|验证|FPGA|架构|AMBA|书籍|

收录近500篇文章|学习路线|基础知识|接口|总线|脚本语言|芯片求职|安全|EDA|工具|低功耗设计|Verilog|低功耗|STA|设计|验证|FPGA|架构|AMBA|书籍|

收录近500篇文章|学习路线|基础知识|接口|总线|脚本语言|芯片求职|安全|EDA|工具|低功耗设计|Verilog|低功耗|STA|设计|验证|FPGA|架构|AMBA|书籍|

收录近500篇文章|学习路线|基础知识|接口|总线|脚本语言|芯片求职|安全|EDA|工具|低功耗设计|Verilog|低功耗|STA|设计|验证|FPGA|架构|AMBA|书籍|