心得Lattice后端使用经验小结(ECP5UM,DDR3,Diamond3.10,Reveal逻辑分析)

Posted free123

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了心得Lattice后端使用经验小结(ECP5UM,DDR3,Diamond3.10,Reveal逻辑分析)相关的知识,希望对你有一定的参考价值。

DDR3 IP例化

LEF5UM器件,应用DDR3控制器IP。主要分几步:IP获取,安装,例化。

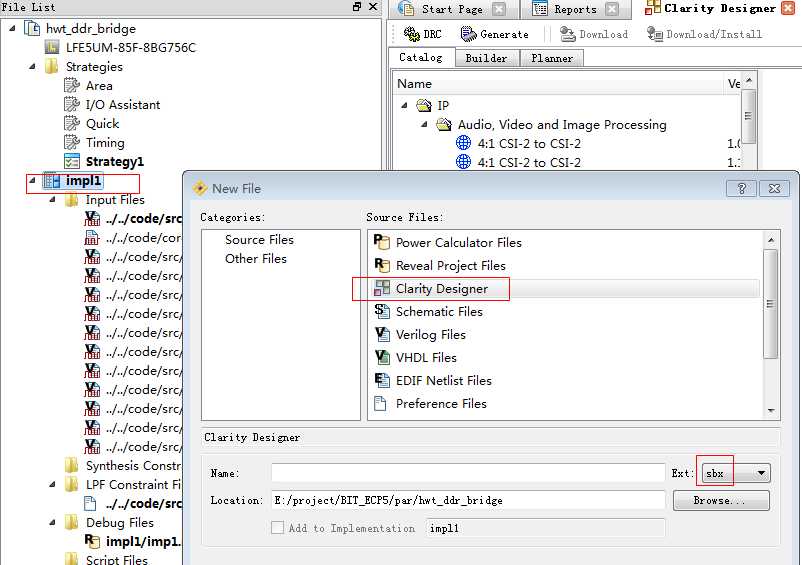

1、先在impl1目录下,右键,新建sbx文件,即Clarity Designer,通过该文件,进行IP的例化管理。

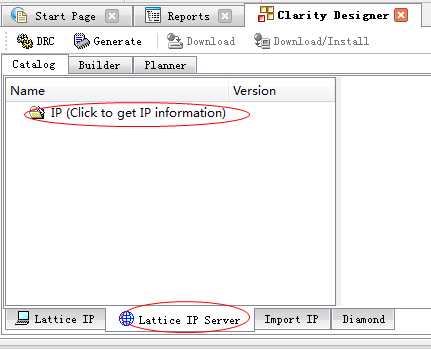

2、打开sbx,在选项卡“Lattice IP Server”里点击IP联网获取IP列表。

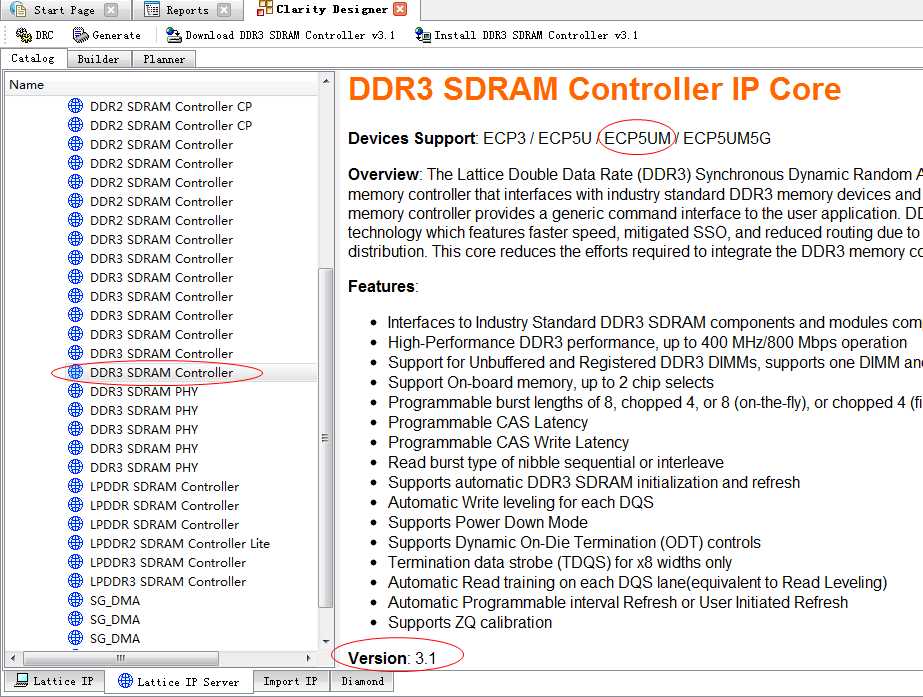

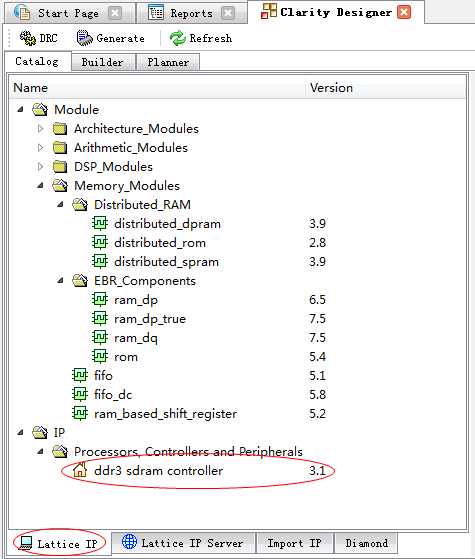

3、选择“DDR3 SDRAM Controller”,目前(18年12月)最新版本3.1,下载(格式exe)后安装到指定目录(如:C:LatticeCoreddr3_sdram_common_v3.1),这样可以在选项卡“Lattice IP”中看到“ddr3 sdram controller 3.1”。

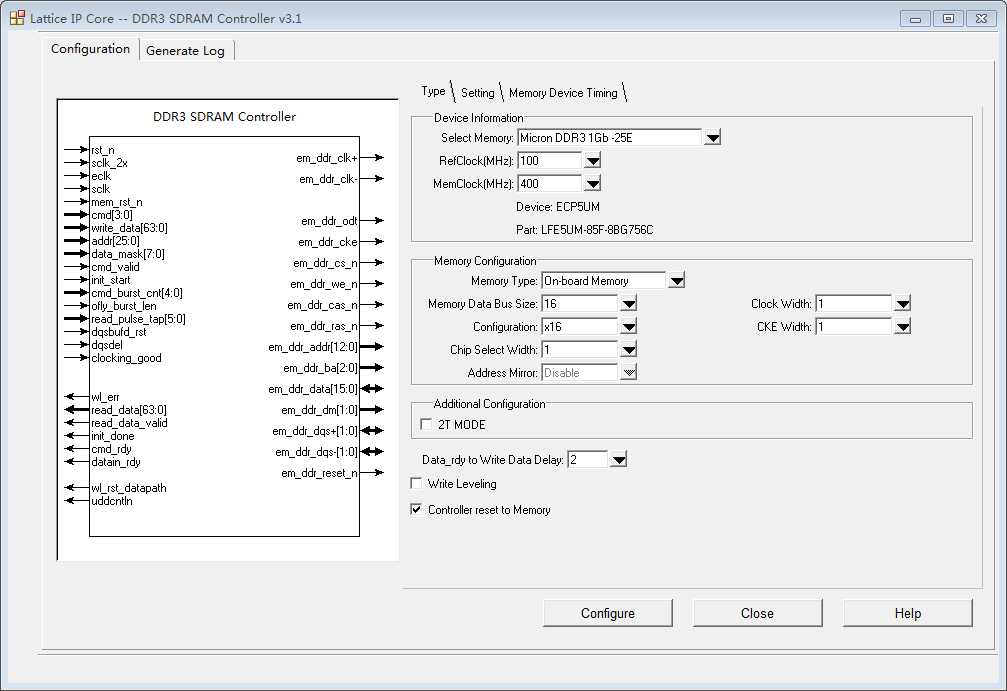

4、打开ip,GUI界面如下,在本项目中,参考时钟(RefClock)来自单板晶振产生的100M,ddr的工作频率400M,双沿也就800M。Memory Type选择On-board Memroy,总线宽度16,配置x16,时钟宽度1。注意,Data_rdy to Write Data Delay选择2,表示data_rdy有效之后必须在第2拍送数据,其实,这里2拍往往是不够的,通常送给ddr3控制器的数据来自一个fifo,这样,fifo跟ddr3控制器直接,不多几拍时钟周期的话,会导致后端时序很难收敛。我的解决办法是,对fifo进行预读操作,让fifo数据打个3~4拍才到ddr3控制器,具体预读fifo的实现就不展开了。

bit/mcs烧录

Lattice工具一个不好用的地方,就是mcs烧录得讲究顺序,否则会报错。烧录mcs的步骤:

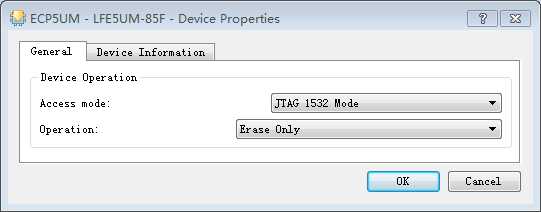

A、JTAG模式下,选择Erase Only。

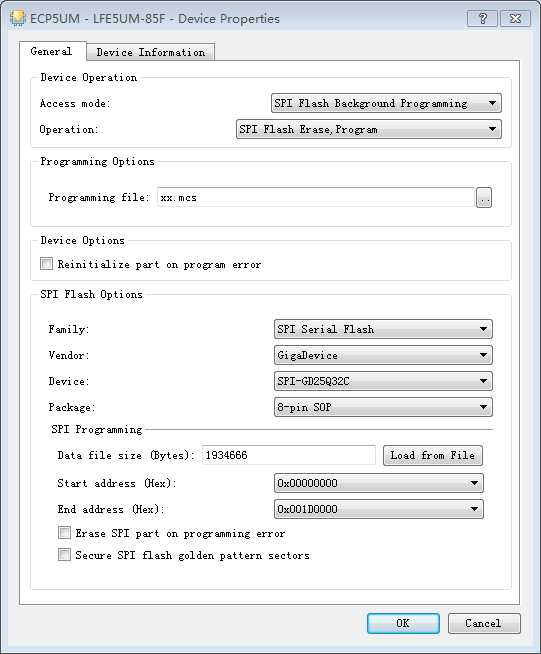

B、选择SPI Flash,操作时可以不用verify,如下。

Reveal逻辑分析仪

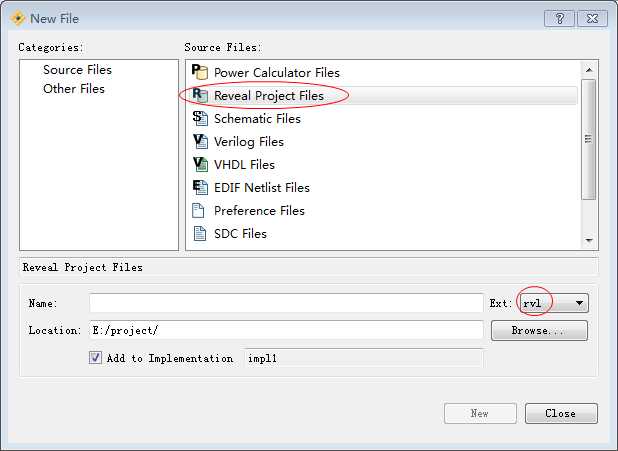

FPGA厂家都会提供内嵌逻辑分析仪,Xilinx叫chipscope,Lattice的叫reveal,可以单独安装reveal程序,也可以在diamond工程中打开。在“File List”的“Debug Files”里,右键,点击Reveal Project Files,可新建*.rvl文件,相对Xilinx,这个rvl比较好用,复制veriog代码信号名,只要没被优化,就可以很快找到。

=======================

by NicoWei

2018-12-25 17:48:09

=======================

以上是关于心得Lattice后端使用经验小结(ECP5UM,DDR3,Diamond3.10,Reveal逻辑分析)的主要内容,如果未能解决你的问题,请参考以下文章