基于nvidia xavier智能车辆自动驾驶域控制器设计与实现(一)

Posted 深圳信迈科技DSP+ARM+FPGA

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于nvidia xavier智能车辆自动驾驶域控制器设计与实现(一)相关的知识,希望对你有一定的参考价值。

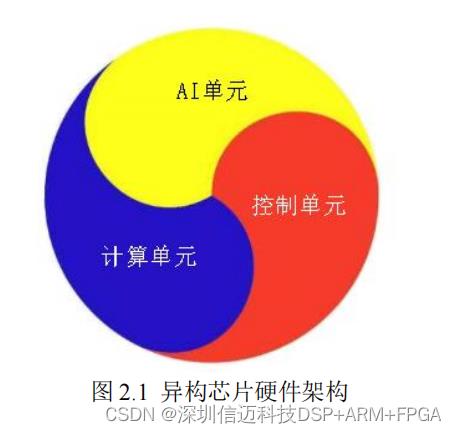

智能车辆在减少交通事故、节能减排、缓解交通拥堵等方面具有十分重要的作用,自动驾驶系统又是智能车辆的核心。近年来,随着智能车辆的应用场景日益广泛,人工智能算法在自动驾驶系统中广泛应用,自动驾驶系统功能不断增强,导致单一芯片架构的硬件平台的算力已经无法满足自动驾驶系统的需要。智能车辆的感知系统由多种类型传感器组成,导致系统集成和通信接口的复杂性增加,传统分布式控制系统架构不能满足可靠性要求。因此,设计一个接口丰富、功能多样、高性 能、集成化高的智能车辆域控制器具有重要的意义。 本文基于异构芯片方案,设计了一个智能车辆域控制器系统平台的软硬件架构。硬件架构以 CPU + GPU 异构芯片模块 Xavier 为主控制器,满足多传感器融合感知系统算力需求。外部接口设计采用了多路多类型接口设计,主要包括多路的Ethernet 、UART 和 CAN 总线等接口。为降低系统集成的复杂性, Ethernet 接口采用非标准POE 功能设计,通过 Ethernet 接口为传感器提供电源供应以减少布线数量。同时, 系统集成了组合导航模块和无线通信模块,为智能车辆系统提供高精度定位和网联通信。软件架构采用分层化和模块化设计。系统层以 Linux 为核心,集成了 ROS 中 间件和通用软件框架,为系统提供分布式通信服务和开发框架。应用层设计了通用基础软件,包括数据采集接口 API 、车辆线控接口 API 、地图接口 API 和组合导航服务 API 等。相比传统分布式控制器,本文设计的域控制器具有接口丰富、功能多样、高性能、集成化高等特点。 2.1.1 异构芯片硬件架构 智能车辆域控制器是结合车辆线控平台和大量多类型外围传感器的核心部分, 具有多样的接口类型、足够的接口数量和高性能等特点。多传感器数据融合、人工 智能算法等技术对域控制器的接口和算力性能都有着更高要求,因此,域控制器需 要采用单卡集成多种架构芯片的异构多核芯片的硬件方案。异构多核芯片硬件架构 主要由具有不同功能的 AI 单元、计算单元和控制单元三部分组成,如图 2.1 所示。 控制单元主要基于传统车辆控制器(

MCU

)完成车辆动力学横纵向控制任务。

搭载基础软件平台的控制单元将各个车辆控制的功能软件连接起来实现车辆控制。

同时,软件系统需要预留与智能车辆操作系统集成的通信接口。

基于多核

CPU

的计算单元具有主频高,计算能力强等特点,通过系统内核管理

软件和硬件资源、完成任务调度。计算单元主要用于执行大部分自动驾驶相关的核

心算法,整合多传感器融合数据完成路径规划、决策控制等功能。

基于并行计算架构的

AI

单元是异构芯片硬件架构中算力最大的一部分,通过

系统内核进行加速引擎和软硬件资源的分配、调度。

AI

单元主要完成多传感器融合

数据的分析和处理,输出用于规划、决策和控制的周围环境信息。目前,主流的

AI

芯片可选架构有

GPU

、

FPGA

、

ASIC

等,其性能对比如表

2.1

所示。

控制单元主要基于传统车辆控制器(

MCU

)完成车辆动力学横纵向控制任务。

搭载基础软件平台的控制单元将各个车辆控制的功能软件连接起来实现车辆控制。

同时,软件系统需要预留与智能车辆操作系统集成的通信接口。

基于多核

CPU

的计算单元具有主频高,计算能力强等特点,通过系统内核管理

软件和硬件资源、完成任务调度。计算单元主要用于执行大部分自动驾驶相关的核

心算法,整合多传感器融合数据完成路径规划、决策控制等功能。

基于并行计算架构的

AI

单元是异构芯片硬件架构中算力最大的一部分,通过

系统内核进行加速引擎和软硬件资源的分配、调度。

AI

单元主要完成多传感器融合

数据的分析和处理,输出用于规划、决策和控制的周围环境信息。目前,主流的

AI

芯片可选架构有

GPU

、

FPGA

、

ASIC

等,其性能对比如表

2.1

所示。

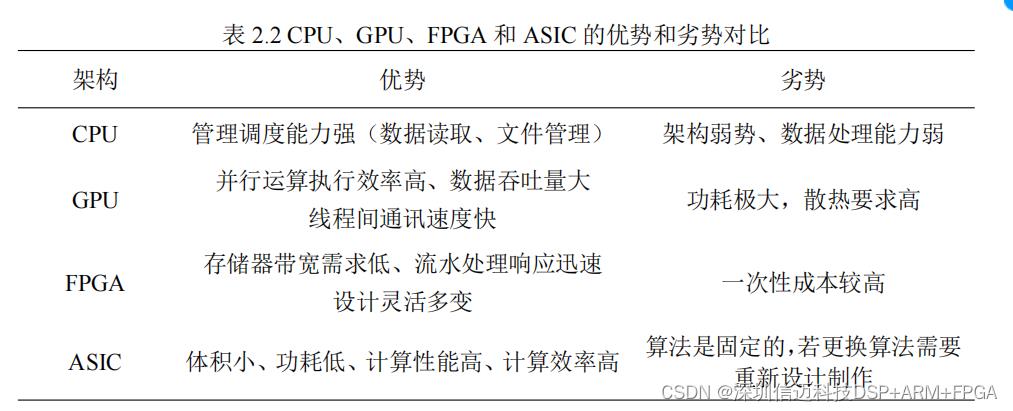

CPU

主要执行逻辑计算和控制两项任务。在构成

CPU

的晶体管中,

70%

用于构

建缓存,其余部分由控制单元用来处理复杂逻辑、提高指令的执行效率。因此,

CPU

架构的优点是计算通用性强,可以处理高复杂度的计算,延时低。其缺点是算力不

高。

GPU

由大面积的

ALU

构成,省去了繁琐的逻辑控制,专注于单一指令的并行

计算,适合大规模并发计算。

GPU

的优点是逻辑控制单元简单,并行计算能力强。

其缺点是缓存较小,读取数据延时较高,功耗较高。

FPGA

适用于多条指令并行执行,单数据流,常用于云端的“训练”阶段。由

于

FPGA

没有存取功能的原因,因此,计算速度快,运行功耗低,但整体的运算量

不大。客户可根据实际需求,通过编程改变用途,但量产成本较高。

ASIC

是制作完成并且只搭载一种算法形成专门用途的芯片架构。首次定制成本

高,但量产成本低,适用场景单一。目前自动驾驶算法仍在快速更迭和进化,

ASIC

不适合算法迭代开发,未来算法稳定后,

ASIC

具有优势。

对于智能车辆系统来说,单一芯片架构难以满足视频、图片、激光雷达点云等

非结构化数据的处理分析和多传感器数据融合。因此,智能车辆系统对车载处理器

的并行计算效率提出更高要求。通过上述分析,

CPU

、

GPU

、

FPGA

和

ASIC

优劣

势对比如表

2.2

所示。

CPU

主要执行逻辑计算和控制两项任务。在构成

CPU

的晶体管中,

70%

用于构

建缓存,其余部分由控制单元用来处理复杂逻辑、提高指令的执行效率。因此,

CPU

架构的优点是计算通用性强,可以处理高复杂度的计算,延时低。其缺点是算力不

高。

GPU

由大面积的

ALU

构成,省去了繁琐的逻辑控制,专注于单一指令的并行

计算,适合大规模并发计算。

GPU

的优点是逻辑控制单元简单,并行计算能力强。

其缺点是缓存较小,读取数据延时较高,功耗较高。

FPGA

适用于多条指令并行执行,单数据流,常用于云端的“训练”阶段。由

于

FPGA

没有存取功能的原因,因此,计算速度快,运行功耗低,但整体的运算量

不大。客户可根据实际需求,通过编程改变用途,但量产成本较高。

ASIC

是制作完成并且只搭载一种算法形成专门用途的芯片架构。首次定制成本

高,但量产成本低,适用场景单一。目前自动驾驶算法仍在快速更迭和进化,

ASIC

不适合算法迭代开发,未来算法稳定后,

ASIC

具有优势。

对于智能车辆系统来说,单一芯片架构难以满足视频、图片、激光雷达点云等

非结构化数据的处理分析和多传感器数据融合。因此,智能车辆系统对车载处理器

的并行计算效率提出更高要求。通过上述分析,

CPU

、

GPU

、

FPGA

和

ASIC

优劣

势对比如表

2.2

所示。

综上所述,四种芯片架构的计算能耗比为

ASIC > FPGA > GPU > CPU

。

ASIC和 FPGA

计算能耗比高于

CPU

、

GPU

,但是

ASIC

和

FPGA

存在一次性成本较高和 算法是固定的的缺点,相比之下,基于 CPU

和

GPU

的两个异构单元依然具有优势。 本文设计的智能车辆域控制器的目的是为了提供集成化、功能多样化的软硬件接口统一的开发平台,以支持多种算法的快速研究,基于 CPU+GPU

多芯片架构的更适合现阶段的智能车辆系统开发和算法迭代的设计要求。

综上所述,四种芯片架构的计算能耗比为

ASIC > FPGA > GPU > CPU

。

ASIC和 FPGA

计算能耗比高于

CPU

、

GPU

,但是

ASIC

和

FPGA

存在一次性成本较高和 算法是固定的的缺点,相比之下,基于 CPU

和

GPU

的两个异构单元依然具有优势。 本文设计的智能车辆域控制器的目的是为了提供集成化、功能多样化的软硬件接口统一的开发平台,以支持多种算法的快速研究,基于 CPU+GPU

多芯片架构的更适合现阶段的智能车辆系统开发和算法迭代的设计要求。

信迈提供自动驾驶控制器软硬一体化方案。

以上是关于基于nvidia xavier智能车辆自动驾驶域控制器设计与实现(一)的主要内容,如果未能解决你的问题,请参考以下文章

Nvidia AGX Xavier GMSL 自动驾驶控制器设计方案