jchdl - RTL实例 - MOS6502 ALU (Verilog)

Posted wjcdx

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了jchdl - RTL实例 - MOS6502 ALU (Verilog)相关的知识,希望对你有一定的参考价值。

https://mp.weixin.qq.com/s/jLUz757FQZjMEYzYb2AIww

MOS6502是简单,但是曾经相当流行的一款CPU。网上有很多模拟程序可供学习使用。这里使用一个较为精简的Verilog项目,介绍MOS6502这款CPU的运行机制,然后使用jchdl进行模拟。

参考项目:https://github.com/Arlet/verilog-6502

该项目只包含两个文件:alu.v, cpu.v。这里首先介绍alu.v。

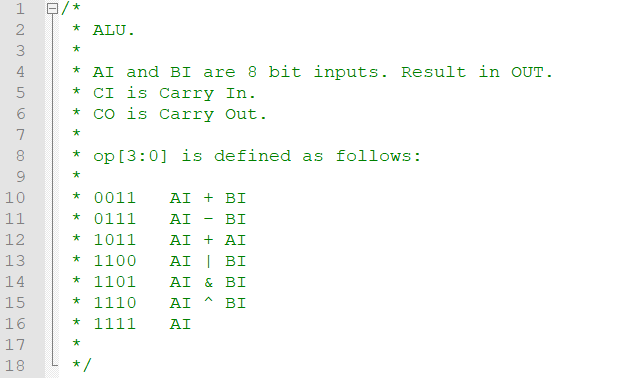

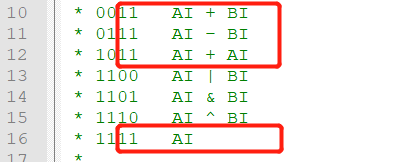

1. 注释部分简介了ALU的主要功能,根据op的不同,对AI/BI进行运算。

? ?

?

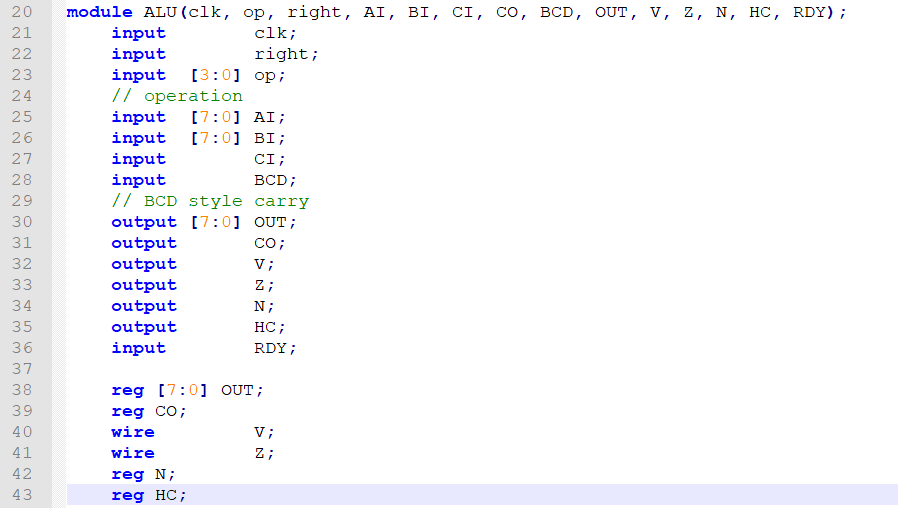

2. 输入输出接口

? ?

?

需要关注的有时钟(clk), 操作类型(op),运算数和进位输入(AI, BI, CI),运算结果和进位输出(OUT, CO),标志位输出(V, Z, N, HC)等

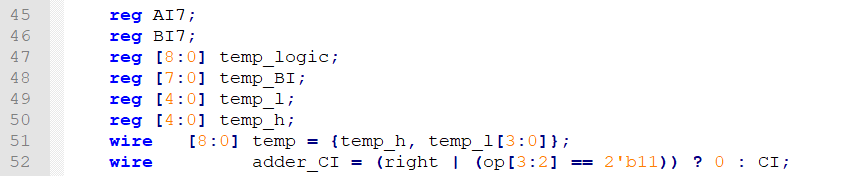

3. 内部变量

? ?

?

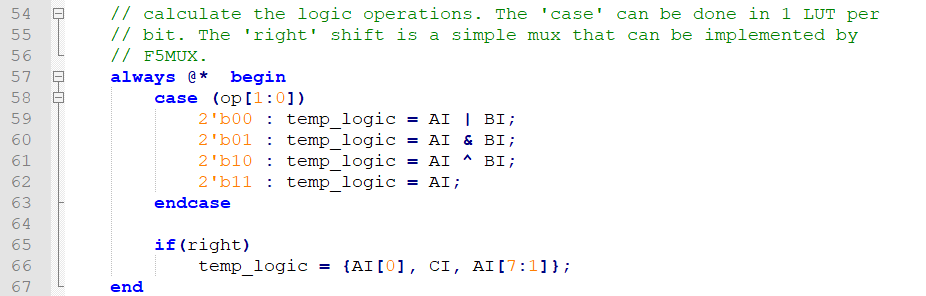

4. 计算逻辑运算的结果

? ?

?

op是经过精心设计的,如果op[1:0]等于2‘b11,则alu执行AI和BI的加减运算:

? ?

?

此时temp_logic中保存运算数AI,以期参与后续运算。

相反的,op[1:0]的另外集中组合,则temp_logic中直接存放逻辑运算结果。这几种情况下,op[3:2]都为2‘b11,不存在其他情况。

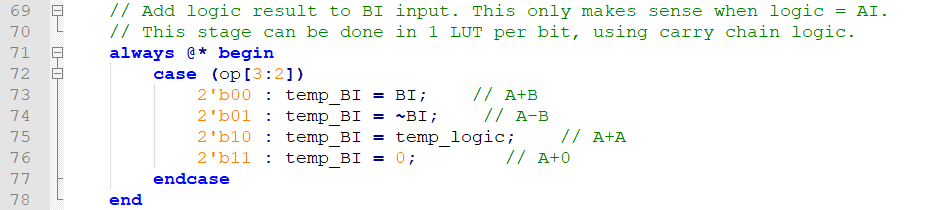

5. 计算算术运算结果

? ?

?

当op[3:2]为2‘b11时,temp_logic中已经是逻辑运算结果了,所以无需temp_BI参加运算,故而直接置零。

当op[3:2]为其他值时,则temp_BI缓存BI的值。根据op的设计,此种情况下,op[1:0]的值为2‘b11, temp_logic中保存的是AI。

- A+B: temp_BI直接缓存BI的值,后续参与运算。

- A-B:减法运算需要对BI求2的补码,即取反加一,这里先行取反。

- A+A:temp_BI缓存temp_logic的值,此时temp_logic中存的是AI的值,所以是A+A。

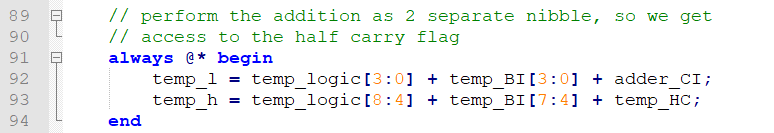

6. 计算运算结果

? ?

?

这里把temp_logic和temp_BI相加,计算最终结果。

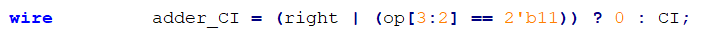

需要指出的是,当运算为A - B时,需要对BI取反加一以求补码。上面只进行了取反,而没有加一,所以要加的1只能来自于adder_CI。adder_CI来自于输入CI:

? ?

?

也没有表明当为减法是,adder_CI或CI为1。查询MOS6502文档之后得知,MOS6502若要执行减法,需要先执行一条把进位置1的指令。

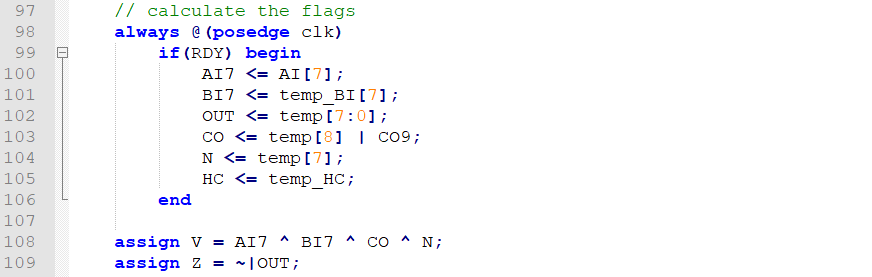

7. 更新进位

? ?

?

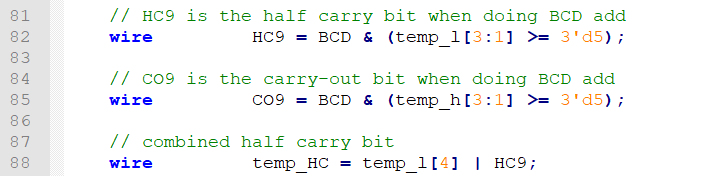

8. BCD的运算

MOS6502可以把AI, BI当成BCD格式(每四位表示一位十进制数)进行运算,并输出BCD格式的数字到OUT中。

BCD运算与二进制运算的区别,主要体现在进位上:

? ?

?

temp_l[3:1]大于等于5,即代表temp_l[3:0]大于等于10,在BCD格式下,需要进位。

其他部分这里不做解释。

以上是关于jchdl - RTL实例 - MOS6502 ALU (Verilog)的主要内容,如果未能解决你的问题,请参考以下文章

jchdl - RTL实例 - Adder

jchdl - RTL实例 - AndAnd

jchdl - RTL实例 - AndReg

jchdl - RTL实例 - Mux

jchdl - RTL实例 - Counter4

jchdl - RTL实例 - Adder4Carry