基于JZ2440开发板编写bootloader总结

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于JZ2440开发板编写bootloader总结相关的知识,希望对你有一定的参考价值。

凡走过必留下痕迹,学点什么都会有用的。

本系列博文总结了自己在学习嵌入式Linux编程过程中的收获,若有错误,恳请指正,谢谢!

——参考教材韦东山系列教材

bootloader 是一个用于启动linux内核的C程序,为了达到最终启动内核的目的需要完成以下几个步骤:

step1:硬件相关初始化,为启动内核准备硬件平台;

step2:将内核从NAND FLASH读取到SDRAM;

step3:设置需要传递给内核的启动参数;

step4:跳转到SDRAM,运行内核;

下面将详细讲述各个步骤细节:

第一步:硬件相关初始化,为启动内核准备硬件平台

基本流程见下图1

(1)禁看门狗

1 ldr r0, =0x53000000 //WTCON : WATCHDOG TIMER CONTROL REGISTER Address = 0x53000000 2 mov r1, #0 //bit 0 = 0 : Disable the reset function of the watchdog timer. 3 str r1, [r0] //将r1中的值存到r0所指定的地址中

(2)设置系统时钟

配置时钟之前先参考下芯片手册 S3C2440A_UserManual_Rev13,需要操作两个寄存器:

- MPLLCON 设置MPLL锁相环倍频因子;

MPLL计算公式 : Mpll = (2 * m * Fin) / (p * 2S) ; m = (MDIV + 8), p = (PDIV + 2), s = SDIV ;Fin取决于外部晶振频率,JZ2440开发板的 [OM2:OM3] 设置为 [0:0] ,因此

main clock和USB clock 依赖外部12MHZ 晶振。

2. CLKDIVN 设置 HCLK , FCLK,PCLK比例关系;

FCLK, HCLK, and PCLK

FCLK is used by ARM920T.

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD controller, the DMA and USB host block.

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,ADC, UART, GPIO, RTC and SPI.

#define S3C2440_MPLL_200MHZ ((0x5c<<12)|(0x01<<4)|(0x02))

/* 2. 设置时钟 */ //先设置各个时钟的比例对CLKDIVN赋值,之后设置系统时钟对MPLLCON赋值 ldr r0, =0x4c000014 //CLKDIVN : CLOCK DIVIDER CONTROL REGISTER Address = 0x4c000014 mov r1, #0x03 //FCLK:HCLK:PCLK=1:2:4, HDIVN=1,PDIVN=1 FCLK=200MHZ HCLK=100MHZ PCLK=50MHZ str r1, [r0] //将r1中的值存到r0所指定的地址中 /* 如果HDIVN非0,CPU的总线模式应该从“fast bus mode”变为“asynchronous bus mode” */ mrc p15, 0, r1, c1, c0, 0 /* 读出控制寄存器 */ orr r1, r1, #0xc0000000 /* 设置为“asynchronous bus mode” */ mcr p15, 0, r1, c1, c0, 0 /* 写入控制寄存器 */ /* MPLLCON = S3C2440_MPLL_200MHZ */ ldr r0, =0x4c000004 //MPLLCON Address = 0x4c000004 ldr r1, =S3C2440_MPLL_200MHZ // S3C2440_MPLL_200MHZ值比较复杂,使用ldr伪汇编 str r1, [r0]

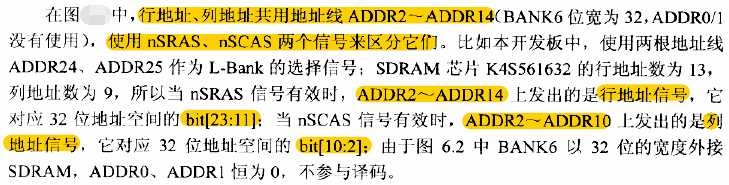

(3)初始化SDRAM

在使用SDRAM之前,有必要了解下什么是SDRAM。请参阅《高手进阶_终极内存技术指南——完整》,这篇文章解释了SDRAM的基本原理。系统上电需要对SDRAM进行初始化,完成对模式寄存器(MR,Mode Register)的配置。主要设置操作模式、CAS潜伏期时间、突发传输方式和突发长度,完成配置后可以根据地址读写SDRAM。本文操作的SDRAM型号是K4S561632N,S3C2440提供标准的总线接口(BANK6),用于操作SDRAM,因此建立了硬件连接之后,操作S3C2440相应的控制寄存器即可完成对SDRAM的配置和读写,具体操作参阅《[嵌入式Linux应用开发完全手册]》第6章 存储控制器。

1 /* 3. 初始化SDRAM */ 2 ldr r0, =MEM_CTL_BASE //SDRAM控制器寄存器首地址,总计需要对13个寄存器配置完成SDRAM的初始化工作 3 adr r1, sdram_config //读取sdram_config的当前地址到r1,此地址取决于当前PC值,是相对跳转 4 add r3, r0, #(13*4) //r3=r0+52 r3值代表了全部控制寄存器所占地址空间大小,总计52字节 5 1: 6 ldr r2, [r1], #4 //从r1所指的地方加载指存入r2,之后r1=r1+4,地址加4字节,32位 7 str r2, [r0], #4 //将r2的值存入r0所指的地方,之后r0=r0+4 8 cmp r0, r3 9 bne 1b //b表示back

1 sdram_config: 2 .long 0x22011110 //BWSCON 3 .long 0x00000700 //BANKCON0 4 .long 0x00000700 //BANKCON1 5 .long 0x00000700 //BANKCON2 6 .long 0x00000700 //BANKCON3 7 .long 0x00000700 //BANKCON4 8 .long 0x00000700 //BANKCON5 9 .long 0x00018005 //BANKCON6 10 .long 0x00018005 //BANKCON7 11 .long 0x008C04F4 //REFRESH 12 .long 0x000000B1 //BANKSIZE 13 .long 0x00000030 //MRSRB6 14 .long 0x00000030 //MRSRB7

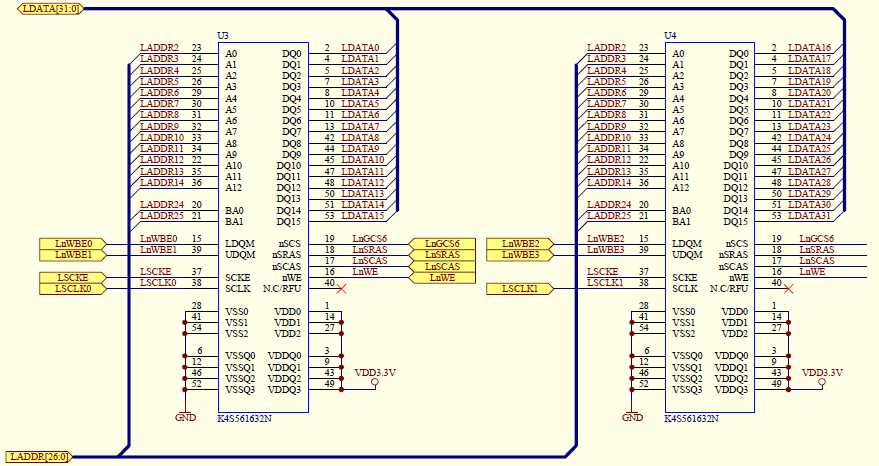

下图是SDRAM的原理图,由两片32M的SDRAM级联成64M,访问一次传递4字节数据。

SDRAM 原理图

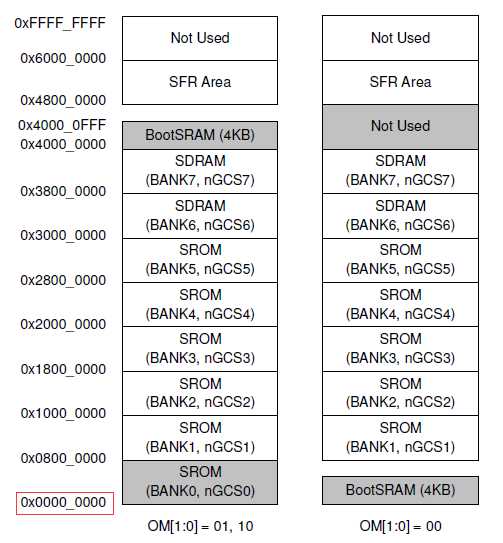

SDRAM由BANK6控制,bank6地址空间为0x30000000~0x38000000,共计128MB。上图所示SDRAM存储空间为64M,因此SDRAM地址空间为0X30000000~0X33FFFFFF。

(4)重定位代码

将启动代码从片内SRAM复制到SDRAM中,使用C代码编写。调用C代码需要设置栈,至于为什么要设置栈请参阅http://www.cnblogs.com/xmphoenix/archive/2012/04/28/2475399.html。这里涉及到三个参数:从哪去读取启动代码,将代码复制到哪去,启动代码多大。

- 从哪去读取启动代码(源地址)

启动代码烧写在NAND,待系统上电后,片内SRAM会加载NAND的起始4K内容。因此启动代码起始地址为:0x00000000

- 读到哪去(目的地址)

在链接文件中指定了启动代码在SDRAM的中存放地址:0x33f80000,启动代码存到SDRAM顶端512k的地址空间中。

- 读多少(大小)

启动代码大小 = 代码段+只读数据段+数据段。BSS段不包含在启动代码中,bss段存放没有初始化的全局变量,或者初始化为0的全局变量,程序运行前将bss段清零。

1 /* 4. 重定位 : 把bootloader本身的代码从flash复制到它的链接地址去 */ 2 ldr sp, =0x34000000 //设置栈,copy函数使用C语言写,调用C代码之前需要设置栈 3 bl nand_init 4 5 mov r0, #0 //传递参数给 copy_code_to_sdram, 对于NOR 启动 6 ldr r1, =_start //链接地址即为代码存储区的首地址 _start = 0x33f80000; 7 ldr r2, =__bss_start //代码段不包括bss段 8 sub r2, r2, r1 //除去BSS段外的所有代码的空间大小 9 10 bl copy_code_to_sdram //参数依次为r0,r1,r2 11 bl clear_bss

完成以上4个步骤后,CPU会转到SDRAM中取指令执行。

以上是关于基于JZ2440开发板编写bootloader总结的主要内容,如果未能解决你的问题,请参考以下文章

S3C2440-裸机篇-01 | JZ2440开发板快速上手

内核搭建完整的mini2440开发板驱动开发环境(仿照JZ2440驱动开发环境搭建)