CPU数据通路设计

Posted ttct

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CPU数据通路设计相关的知识,希望对你有一定的参考价值。

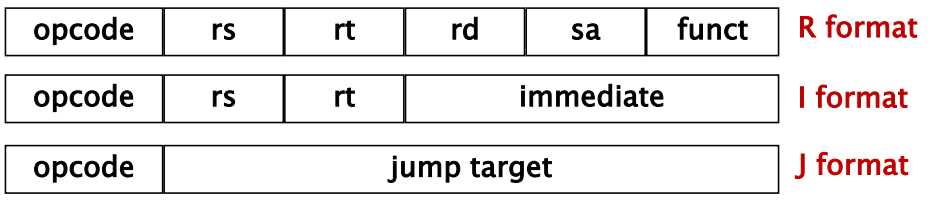

指令的格式如下:

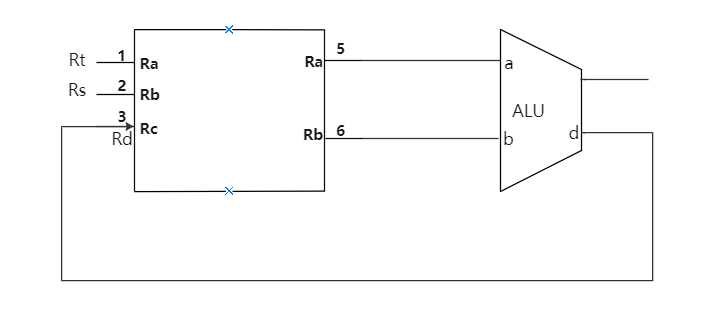

对于R型指令:

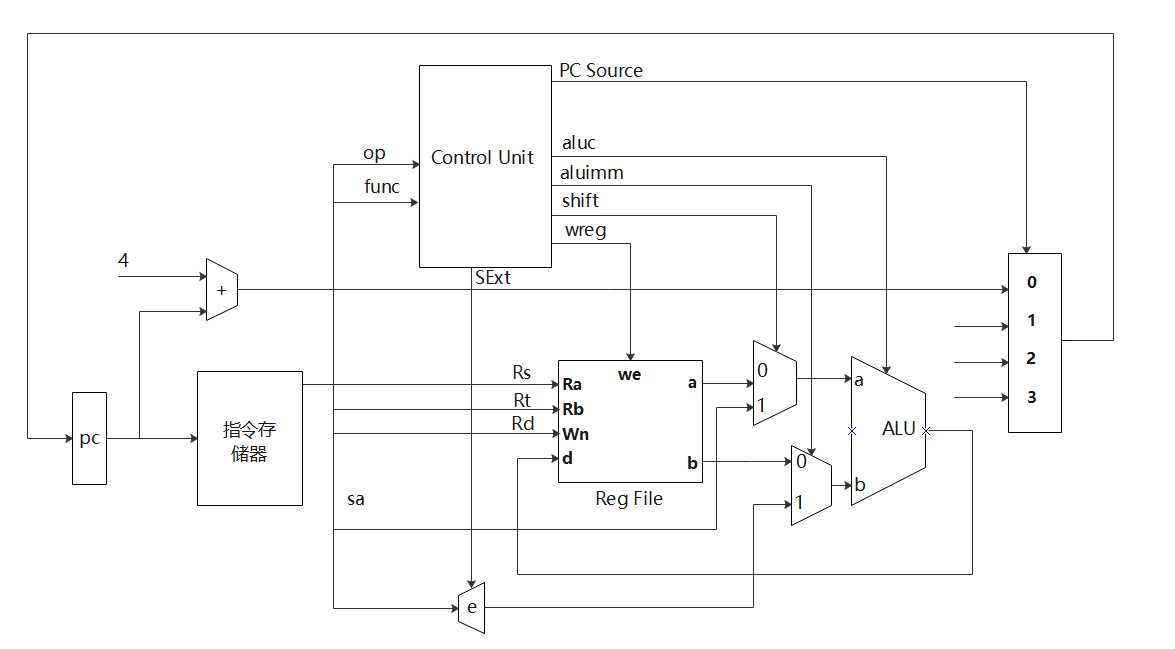

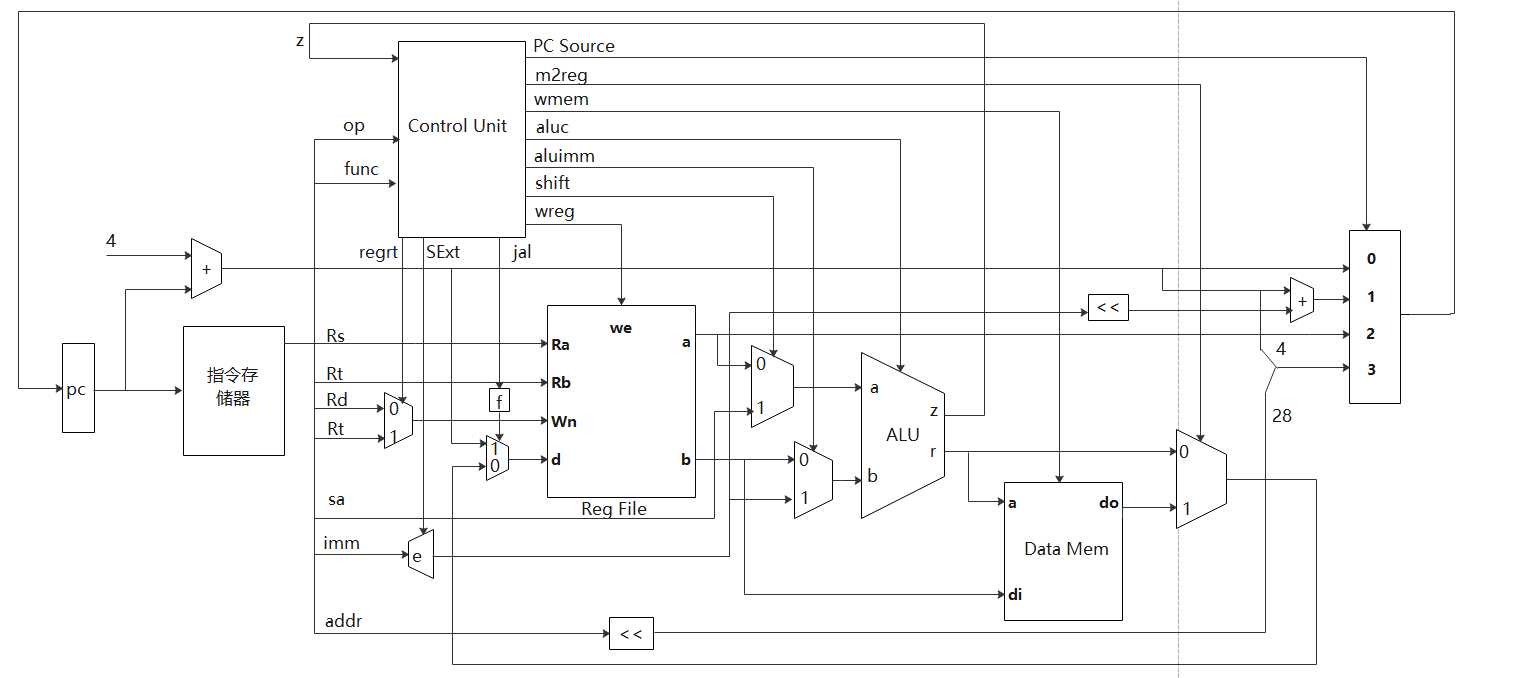

可以完成的功能包括add、sub、and、or、xor等指令,用三个寄存器:rs、rt、rd进行运算,rd用来数据结果的存储,rs,rt则存运算的两个数据,简单的数据通路设计如下:

对于R指令op字段提供类型(R,I,J),func字段提供具体的运算类型,每个操作都有一个具体的类型码,通过这两个字段,控制单元产生对应的信号。

aluc:运算器控制信号 wreg:寄存器写信号

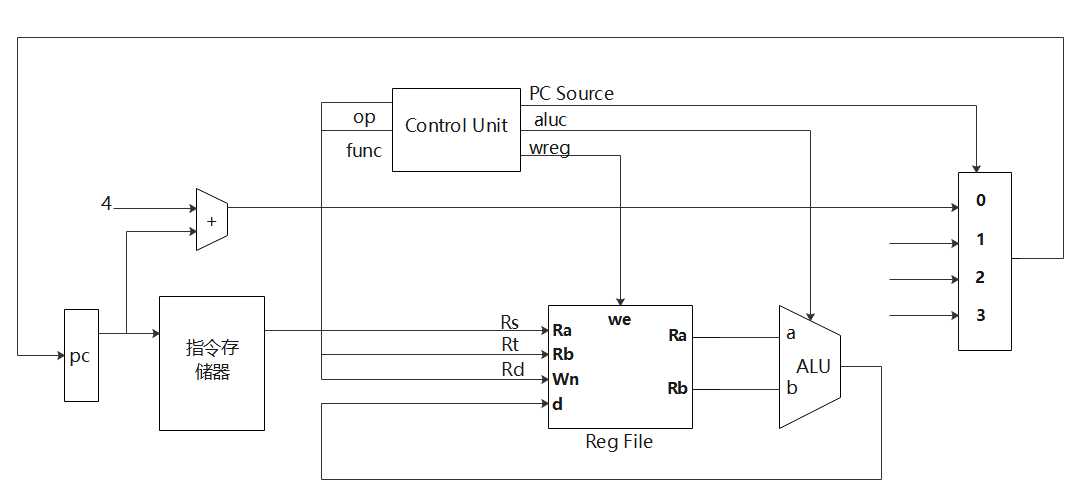

对于R型移位指令,移位位数由指令字段给出,两个操作数分别为Rt和sa给出,通过写寄存器指令将结果写到寄存器Rd中。PC为指令,其中含有指令格式,PC将op与func子段的值给控制单元,控制单元产生指令对应的信号,下一条指令的PC=PC+4。

shift:产生移位信号,控制多路选择器选择移位的数据还是正常的数据。

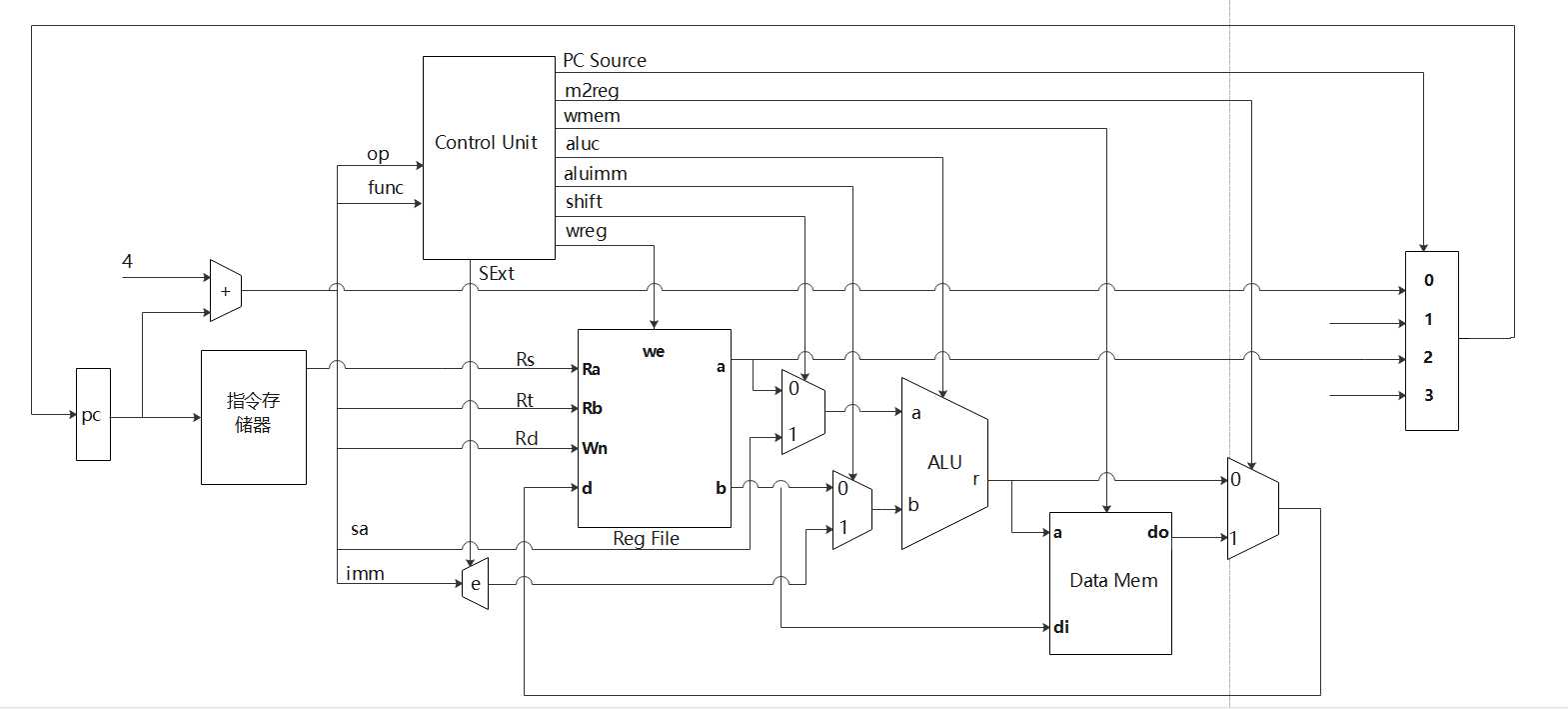

对于I型指令:

![]()

操作数两位由Rs与立即数给出,结果存放在rt中。imm只有16位所以对于的位用0或符号扩展法进行扩展。

e:控制符号扩展或者0扩展 aluimm:控制信号,表明进行立即数的运算

对于I型指令的访存与写回指令:

地址=逻辑地址+物理地址

LW:将存储器某一地址单元的数据加载到寄存器Rt中

SW:将寄存器Rt数据写到存储器某一地址单元中

对于寄存器寻址的计算方法:某一通用寄存器的值Rs+16位符号扩展的立即数=ADDR

wmem:写存储器信号 m2reg:存储器向寄存器写信号

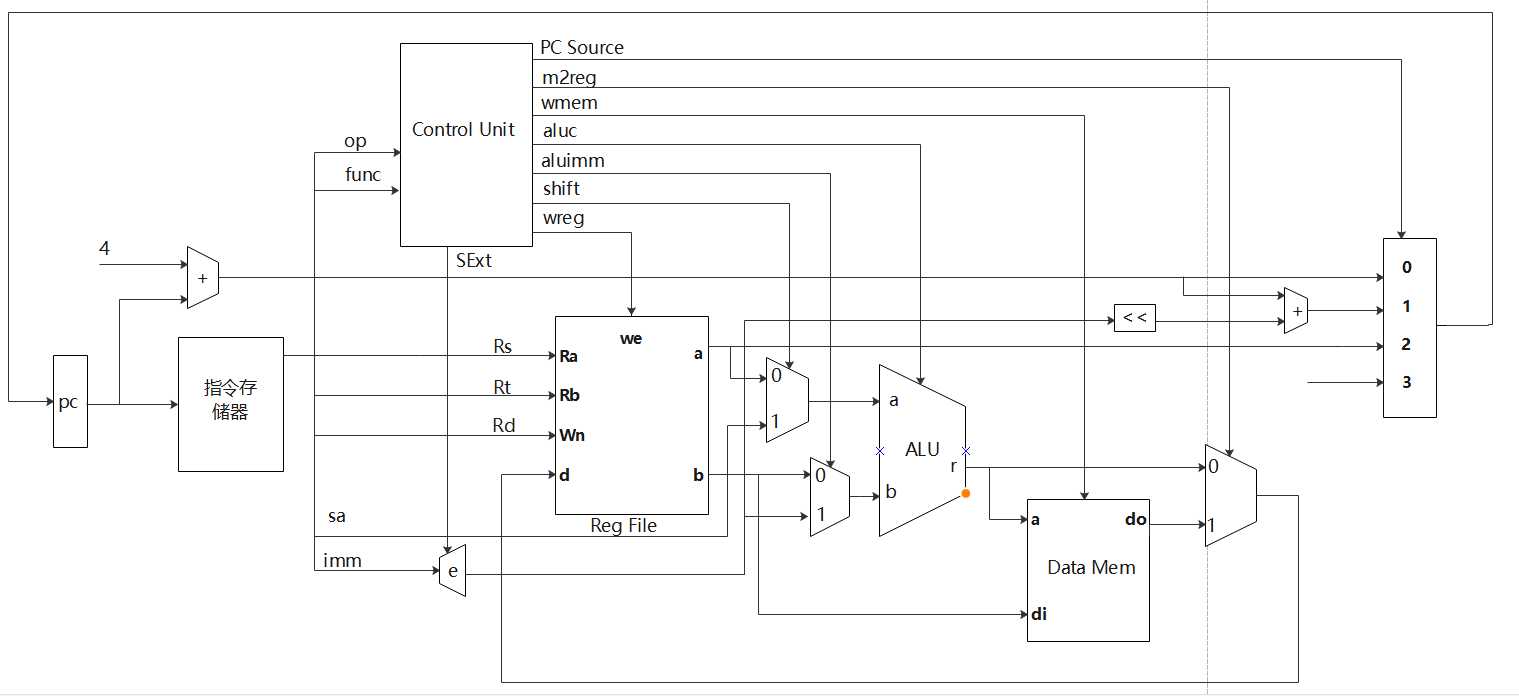

0:PC+4

1:分支指令

2:寄存器寻址指令,寄存器Rt的值为PC执行的地址

3:跳转指令

对于I型指令中的条件转移指令,跳转的PC值=PC+4+SignEXT(imm),但是计算的时候我们还要对扩展后的imm进行左移两位的操作,其原因为:mips的指令长度为4个字节,所以指令地址一定为4的倍数,因而地址后两位一定为0,因此offset左移两位使偏移量变为4的倍数,保持地址最后两位为0。

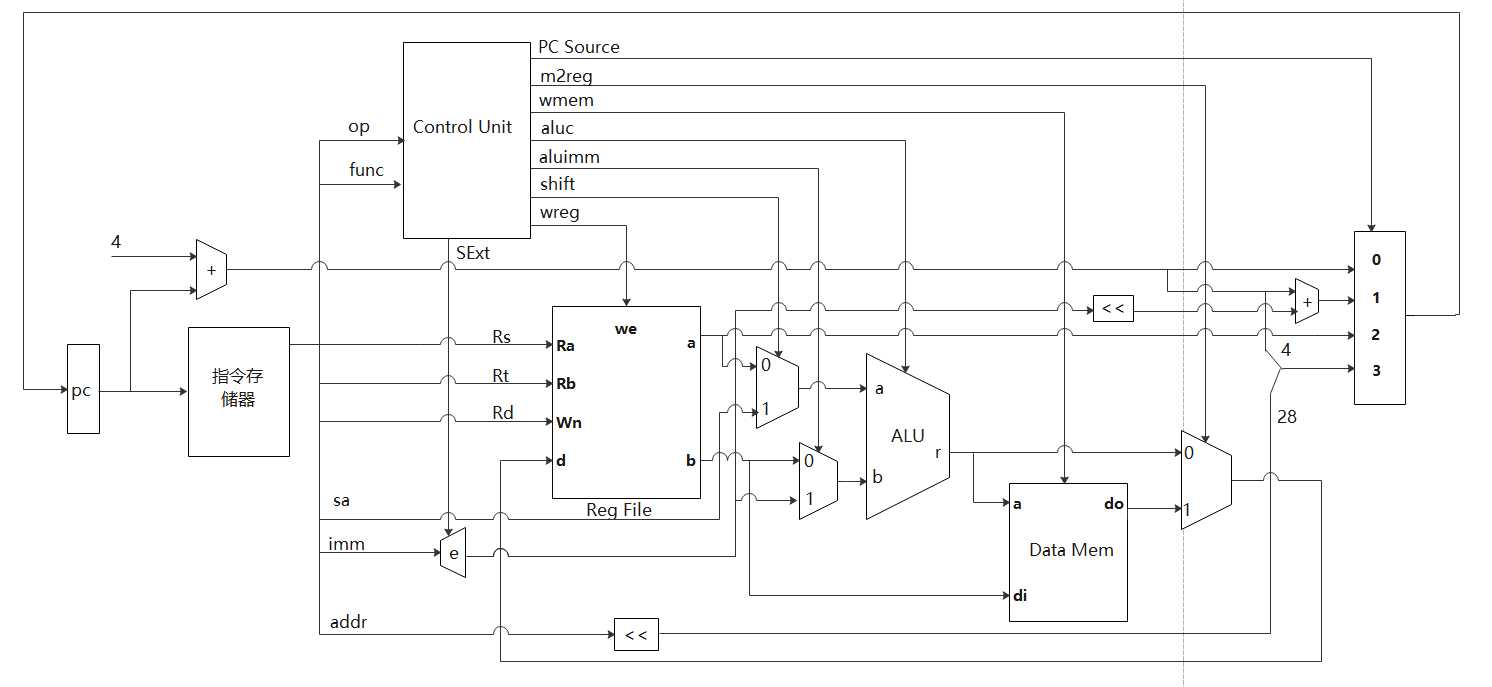

对于J型指令,跳转的目标地址有target给出,jump target 是26位的。

![]()

j指令,跳转指令,跳到target给出的目标地址,高地址4位由PC给出,低地址由addr给出,二者拼接成为32位地址。addr是26位,通过左移两位成28位,因为所有指令在内存中都是4字节对齐的,因此最低的2个比特位是无需存储的,最低为“00”。

jal指令与jr指令与子程序调用返回有关系。jr指令是使用寄存器跳转是R型指令。jal进行函数调用,函数完成后要返回到指令之前进行的位置,所以要把跳转之前的下一条指令的地址存储起来,即将PC+4存到寄存器中。

regrt:控制将结果写到Rt还是Rd中 jal:控制是否进行函数调用,若进行调用,将PC的值存到寄存器中

以上是关于CPU数据通路设计的主要内容,如果未能解决你的问题,请参考以下文章