中央处理器——数据通路之单总线结构

Posted 流楚丶格念

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了中央处理器——数据通路之单总线结构相关的知识,希望对你有一定的参考价值。

数据通路

数据通路:数据在功能部件之间传送的路径。

也就是信息从哪里开始中间经过哪些部件最后传到哪里,由控制部件产生的控制信号建立数据通路

数据通路的基本结构可分为三类:

- CPU内部单总线方式。

- CPU内部多总线方式。

- 专用数据通路方式。

CPU内部单总线方式

内部总线是指同一部件,如CPU内部连接各寄存器及运算部件之间的总线;

系统总线是指同一台计算机系统的各部件,如CPU、内存、通道和各类I/O接口间互相连接的总线。

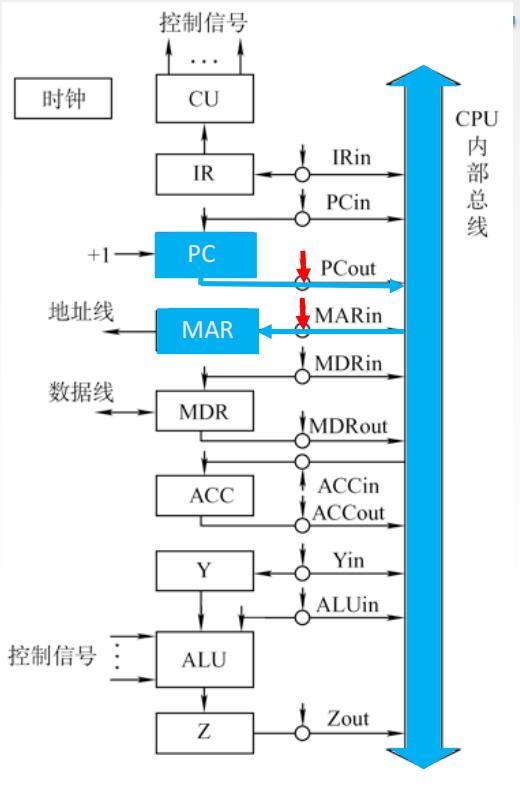

1.寄存器之间数据传送

比如把PC内容送至MAR,实现传送操作的流程及控制信号为:

(PC)→Bus PCout有效,PC内容送总线

Bus→MAR MARin有效,总线内容送MAR

也可写为: (PC)→Bus→MAR

也有的教材写为: PC→Bus→MAR

重要的是描述清楚数据流向

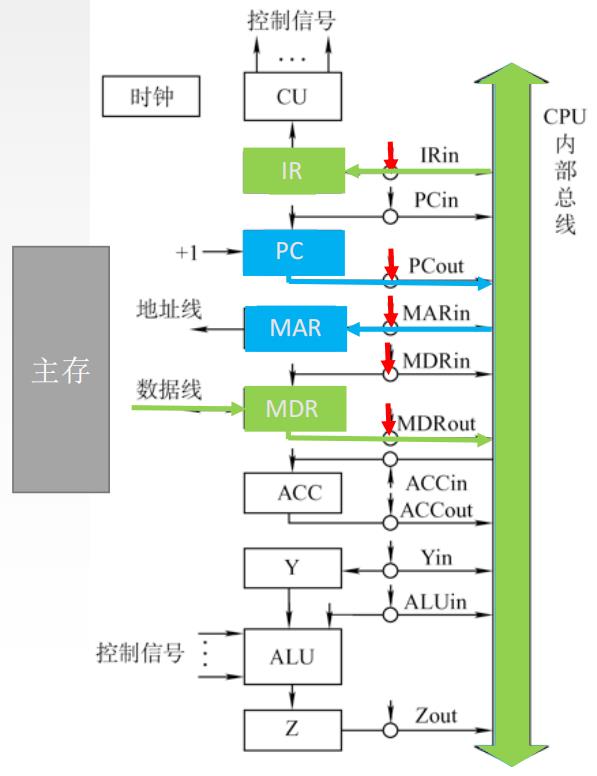

2.主存与CPU之间的数据传送

比如CPU从主存读取指令,实现传送操作的流程及控制信号为:

(PC)→Bus→MAR PCout和MARin有效,现行指令地址→MAR

1→R CU发读命令(通过控制总线发出,图中未画出)

MEM(MAR)→MDR MDRin有效

MDR→Bus→IR MDRout和IRin有效,现行指令→IR

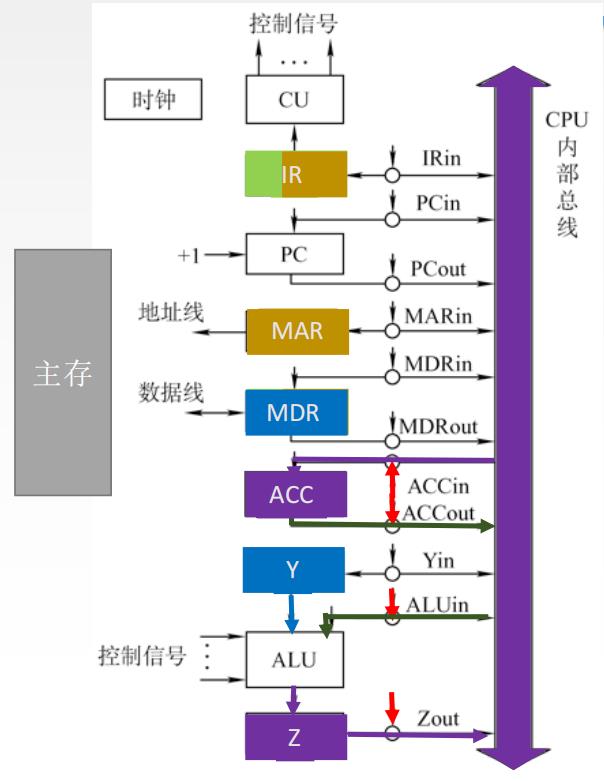

3.执行算术或逻辑运算

比如一条加法指令,微操作序列及控制信号为:

Ad(IR)→Bus→MAR MDRout和MARin有效(或AdIRout和MARin有效)

1→R CU发读命令

MEM(MAR)→数据线→MDR MDRin有效

MDR→Bus→Y MDRout和Yin有效,操作数→Y

(ACC)+(Y)→Z ACCout和ALUin有效,CU向ALU发送加命令

Z→ACC Zout和ACCin有效,结果→ACC

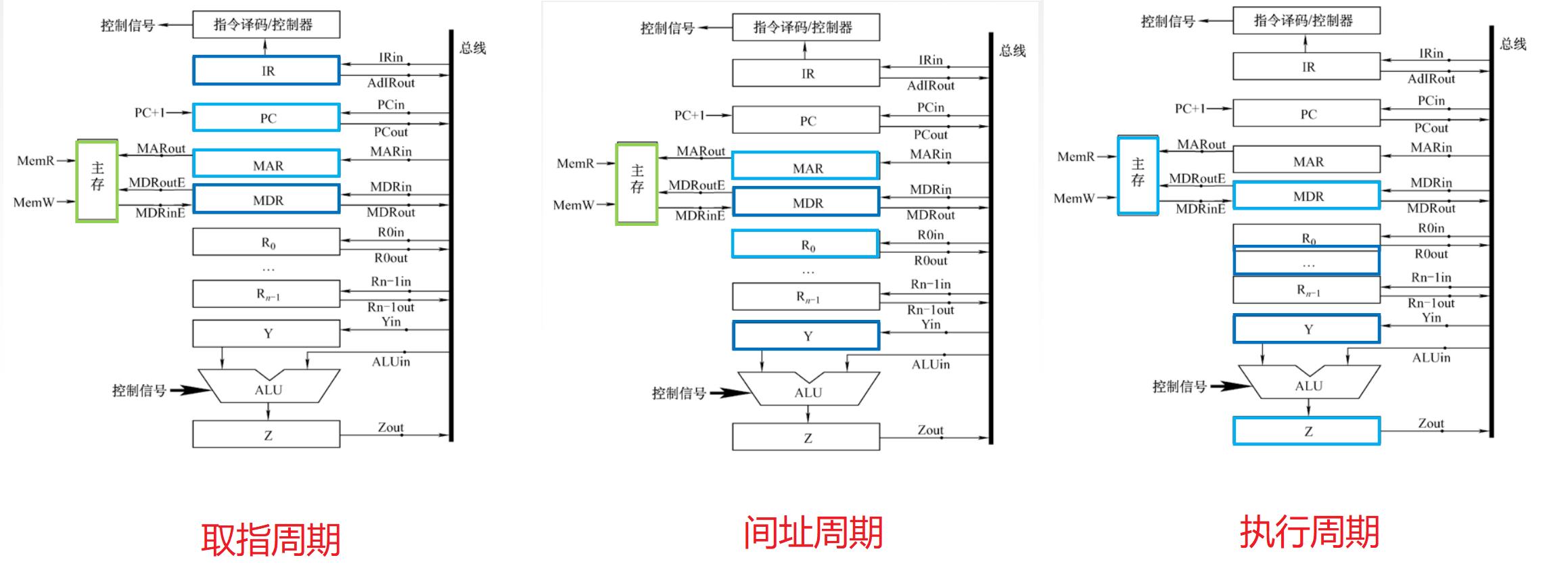

CPU内部单总线方式——例题

设有如图所示的单总线结构,分析指令ADD (R0),R1 的指令流程和控制信号。

解答:

-

分析指令功能和指令周期

功能:((R0))+(R1)→(R0)

取指周期、间址周期、执行周期 -

写出各阶段的指令流程

取指周期:公共操作

| 时序 | 微操作 | 有效控制信号 |

|---|---|---|

| 1 | (PC)→MAR | PCout,MARin |

| 2 | M(MAR)→MDR ,(PC)+1→PC | MemR,MARout,MDRinE |

| 3 | (MDR)→IR | MDRout,IRin |

| 4 | 指令译码 | - |

| 5(可省) | (PC)+1→PC | - |

间址周期:完成取数操作,被加数在主存中,加数已经放在寄存器R1中。

| 时序 | 微操作 | 有效控制信号 |

|---|---|---|

| 1 | (R0)→MAR | R0out,MARin |

| 2 | M(MAR)→MDR | MemR,MARout,MDRinE |

| 3 | (MDR)→Y | MDRout,Yin |

执行周期:完成取数操作,被加数在主存中,加数已经放在寄存器R1中。

| 时序 | 微操作 | 有效控制信号 |

|---|---|---|

| 1 | (R1)+(Y)→Z | R1out,ALUin,CU向ALU发ADD控制信号 |

| 2 | (Z)→MDR | Zout,MDRin |

| 3 | (MDR)→M(MAR) | MemW,MDRoutE,MARout |

各个周期之执行数据流程图如下:

以上是关于中央处理器——数据通路之单总线结构的主要内容,如果未能解决你的问题,请参考以下文章