组成原理-处理器数据通路

Posted Mount256

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了组成原理-处理器数据通路相关的知识,希望对你有一定的参考价值。

文章目录

1 数据通路的结构和组成

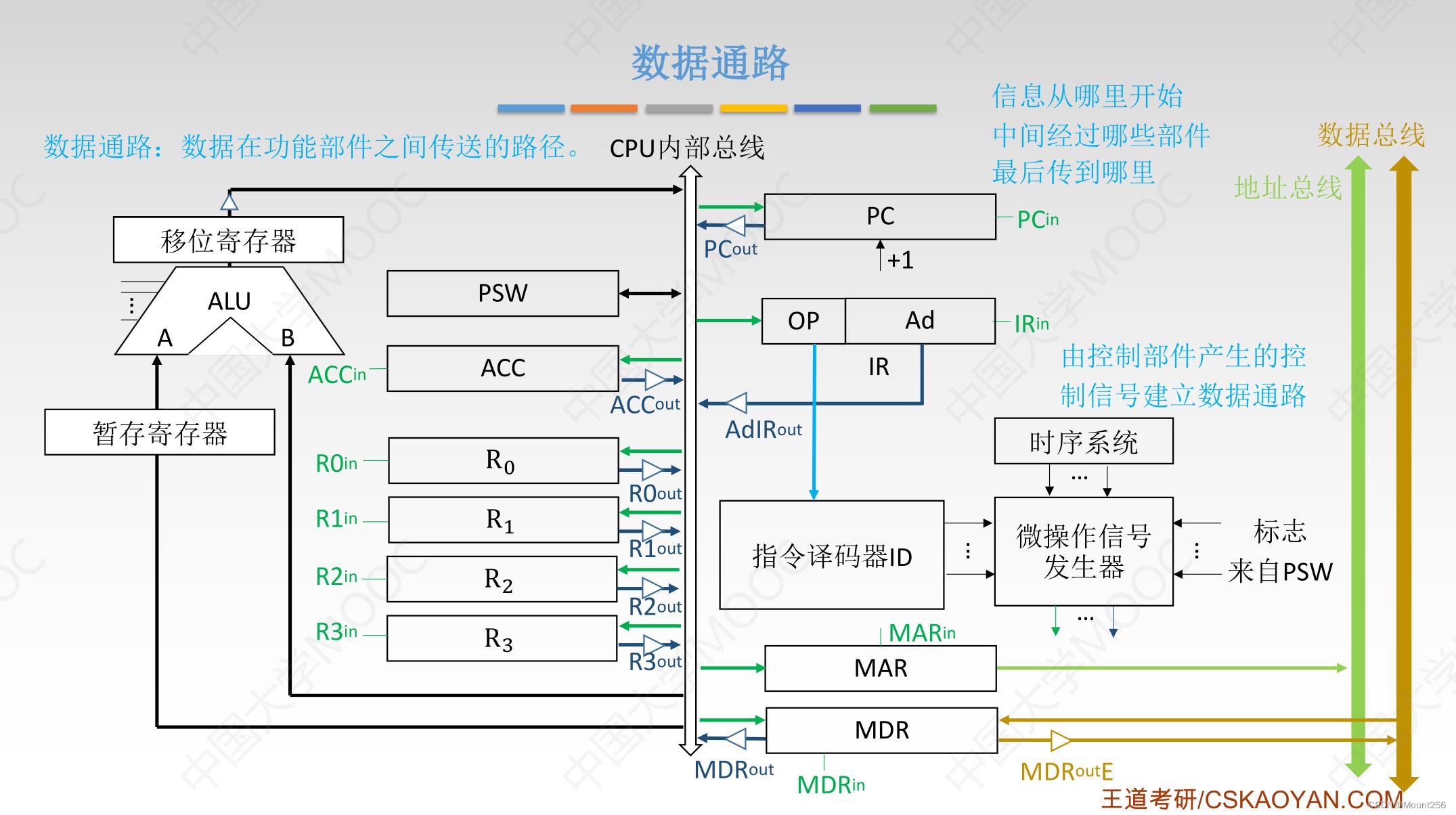

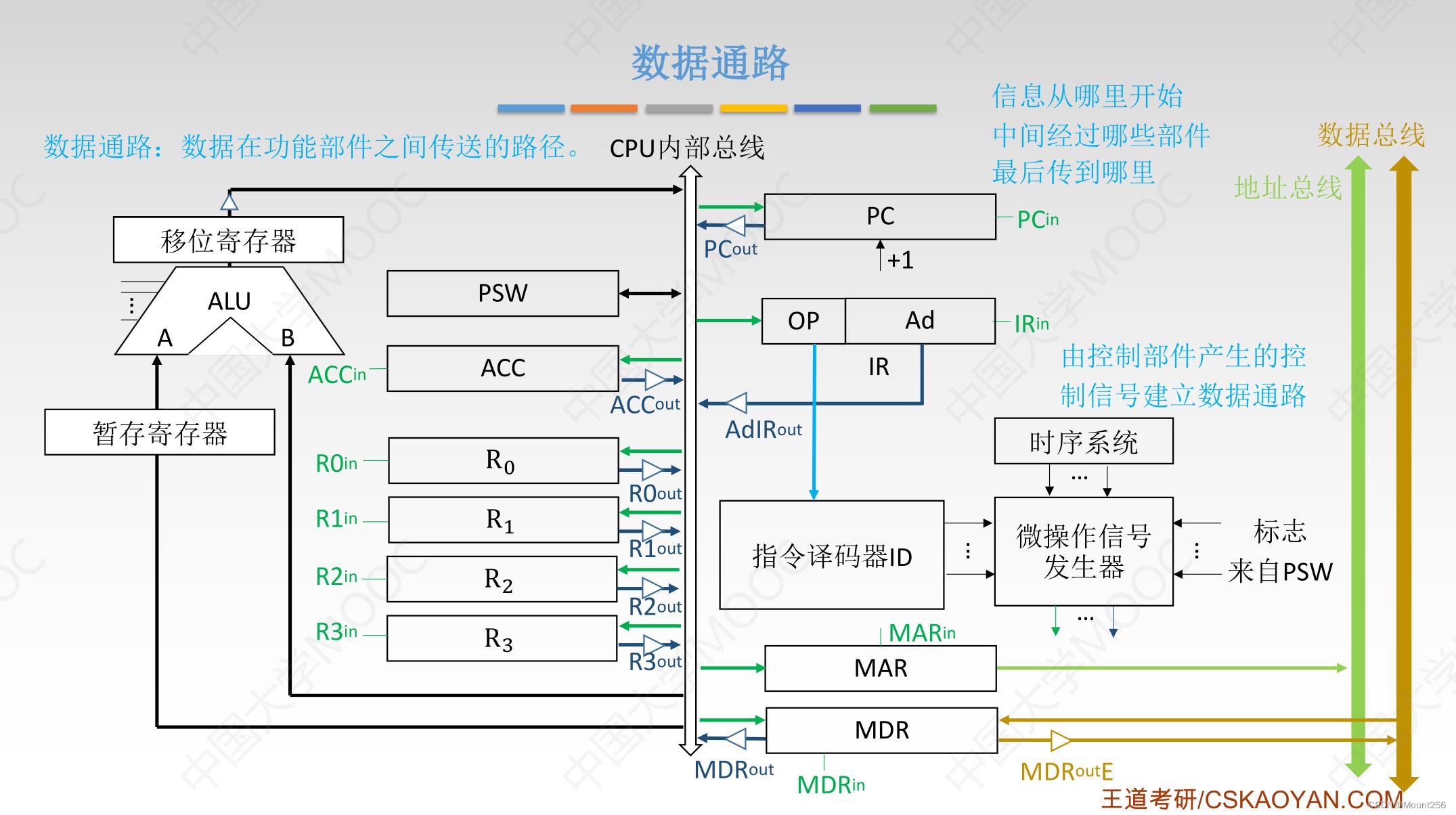

数据在功能部件之间传送的路径称为数据通路,包括数据通路上流经的部件,如 ACC、ALU、状态寄存器。通用寄存器等。

1.1 数据通路的基本结构

数据通路的基本结构分为两种:

(1)内部总线结构(可参考“总线”章节)

- CPU 内部单总线方式(常考,类似看图说话)

- CPU 内部双总线方式

- CPU 内部三总线方式

(2)专用数据通路方式(有一定几率考,但做题方法与单总线的相同):不使用共享的总线

1.2 数据通路的基本组成(单总线结构)

- “in”:允许数据从内部总线输入到该部件的信号

- “out”:允许数据从该部件输出到内部总线的信号

1.2.1 指令相关

| 寄存器/部件 | (从 CU 发出的)控制信号 |

|---|---|

| 程序计数器 PC | PCin、PCout |

| 指令寄存器 IR | IRin |

| 指令寄存器中存储的指令的地址码部分 Ad(IR) | AdIRout |

1.2.2 运算相关

| 寄存器/部件 | (从 CU 发出的)控制信号 |

|---|---|

| 累加寄存器 ACC | ACCin、ACCout |

| 暂存输入寄存器 Y | Yin |

| 暂存输出寄存器 Z | Zout |

| 算术逻辑单元 ALU | ALUin |

| 通用寄存器 Rx | Rxin、Rxout |

1.2.3 存储相关

- “E”:表示允许控制该部件往主存输入数据/从主存接收数据的信号

- 未加“E”:表示允许控制该部件往内部总线输入数据/从内部总线接收数据的信号

- MemR:允许从主存读出数据

- MemW:允许往主存写入数据

| 寄存器/部件 | (从 CU 发出的)控制信号 |

|---|---|

| 存储器地址寄存器 MAR | MARin、MARout;MARoutE |

| 存储器数据寄存器 MDR | MDRin、MDRout;MDRinE、MDRoutE |

| 将寄存器内的数据当做地址,往主存的该地址读或写数据 M(MAR)、M(MDR) | MemR、MemW |

2 数据通路中的数据传送(单总线结构)

2.1 取指周期

| 功能 | 控制信号 | 描述 |

|---|---|---|

| (PC)–>MAR | PCout, MARin | 指令对应的地址放入 MAR 中 |

| M(MAR)–>MDR | MemR, MDRinE | 从主存的相应地址读出指令并存入 MDR 中 |

| (MDR)–>IR | MDRout, IRin | MDR 存储的指令放入 IR 中 |

| 指令译码 | 无 | 无 |

| (PC)+1–>PC | PC+1 | 程序计数器加 1 个指令字长 |

数据通路:PC–>MAR–>Mem–>MDR–>IR

2.2 间址周期

2.2.1 间接寻址

| 功能 | 控制信号 | 描述 |

|---|---|---|

| Ad(IR)–>MAR 或 Ad(MDR)–>MAR | MDRout, MARin | 读出指令的地址码部分,送入 MAR 中(注意没有 IRout) |

| M(MAR)–>MDR | MemR, MDRinE | 从主存的相应地址读出数据并存入 MDR 中 |

| (MDR)–>Y | MDRout, Yin | MDR 存储的数据放入暂存输入寄存器 Y 中 |

数据通路:IR(或 MDR)–>MAR–>Mem–>MDR–>Y

2.2.2 寄存器间接寻址

| 功能 | 控制信号 | 描述 |

|---|---|---|

| (R0)–>MAR | R0out, MARin | 读出 R0 的数据,送入 MAR 中 |

| M(MAR)–>MDR | MemR, MDRinE | 从主存的相应地址读出数据并存入 MDR 中 |

| (MDR)–>Y | MDRout, Yin | MDR 存储的数据放入暂存输入寄存器 Y 中 |

数据通路:R0–>MAR–>Mem–>MDR–>Y

2.3 执行周期

以ADD (R0), R1为例,功能为((R0))+(R1)–>(R0),说明执行指令流程和控制信号。

| 功能 | 控制信号 | 描述 |

|---|---|---|

| (Y)+(R1)–>Z | Yout, R1out, Zin, ALUin | Y 中数据和 R1 中数据相加,经过 ALU 计算的结果存入 Z 中(注意没有 ALUout) |

| (Z)–>MDR | Zout, MDRin | 将计算结果放入 MDR 中 |

| (MDR)–>M(MAR) | MDRoutE, MemW | 将 MDR 数据放入到主存相应地址中,注意此时 MAR 仍存储着 R0 的数据 |

数据通路:Y, R1–>ALU–>Z–>MDR–>Mem

以上是关于组成原理-处理器数据通路的主要内容,如果未能解决你的问题,请参考以下文章