高层次综合器(Vivado HLS)的设计流程[原创www.cnblogs.com/helesheng]

Posted 一个电子爱好者的工作记录

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了高层次综合器(Vivado HLS)的设计流程[原创www.cnblogs.com/helesheng]相关的知识,希望对你有一定的参考价值。

介绍高层次综合器(Vivado HLS)的使用流程

介绍高层次综合器(Vivado HLS)的使用流程

最近在写一本Xilinx的FPGA方面的书,现将HLS部分内容在这里分享给大家,希望大家喜欢,也欢迎批评指正。以下原创内容欢迎网友转载,但请注明出处: https://www.cnblogs.com/helesheng

下面用一个简单实例来演示使用高层次综合器进行硬件设计的流程,带领读者以点带面的掌握Vivado HLS的设计方法。

有限冲击响应滤波器,简称FIR(Finite Impulse Response)滤波器,是数字信号处理系统中最常见的算法之一。相比无限冲激响应滤波器(IIR)滤波器而言,FIR滤波器虽然计算效能较低,但它具有以下两个明显优势:

(1)严格线性相位;

(2)冲击响应长度有限,永远稳定。

可编程逻辑器件的高并行性、计算速度快的优势,正好克服了FIR滤波器计算量大的劣势。下面以FIR滤波器的实现为例,介绍HLS的开发和优化流程。实验内容及步骤如下:

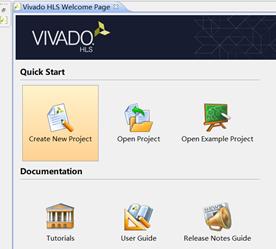

1、打开Vivado HLS(Vivado HLS是一个单独的应用程序,可以不依赖于Vivado打开),如图8.2.1所示,单击开始界面的Create New Project。

图8.2.1 新建Vivado HLS工程界面

2、如图8.2.2所示,输入新建的工程名称,指定路径,单击Next。

图8.2.2 在指定目录创建工程

3、在如图8.2.3和8.2.4所示的界面,分别添加已有的设计文件和测试脚本。(初次创建工程,可以不添加任何文件或脚本,单击Next跳过)

图8.2.3 添加已有的设计文件

图8.2.4 添加已有的测试脚本

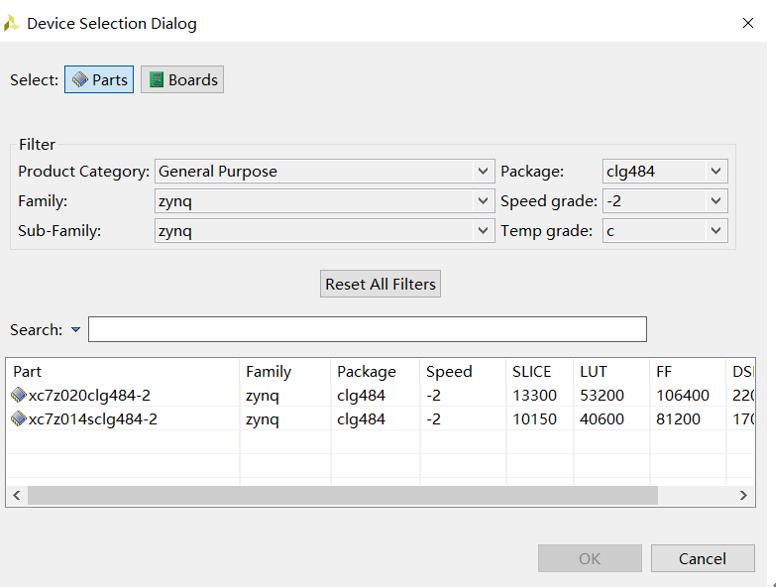

4、在图8.2.5所示的方案配置界面中,设置默认的时钟周期为10ns,单击Part Select区域右侧的选择按钮,并在弹出的图8.2.6所示界面中筛选工程中使用的器件。返回方案配置界面,单击Finish完成新建工程。

图8.2.5 配置方案界面

图8.2.6 选择工程中使用的器件

5、右键单击工程主界面左侧的Explorer栏的Source,选择New File,新建一个fir.h文件和一个fir.c文件。

头文件内容:

#ifndef FIR_H_ #define FIR_H_ #define N 11 typedef int coef_t; typedef int data_t; typedef int acc_t; void fir ( data_t *y, coef_t c[N+1], data_t x ); #endif

C语言源码:

#include "fir.h" void fir(data_t *y,data_t x) coef_t C[N] = 53,0,-91,0,313,500,313,0,-91,0,53; data_t shift_reg[N]; acc_t acc; int i; acc=0; Shift_Accum_Loop: for (i=N-1;i>=0;i--) if (i==0) shift_reg[0]=x; data = x; else shift_reg[i]=shift_reg[i-1]; data = shift_reg[i]; acc+=data*c[i];; *y=acc;

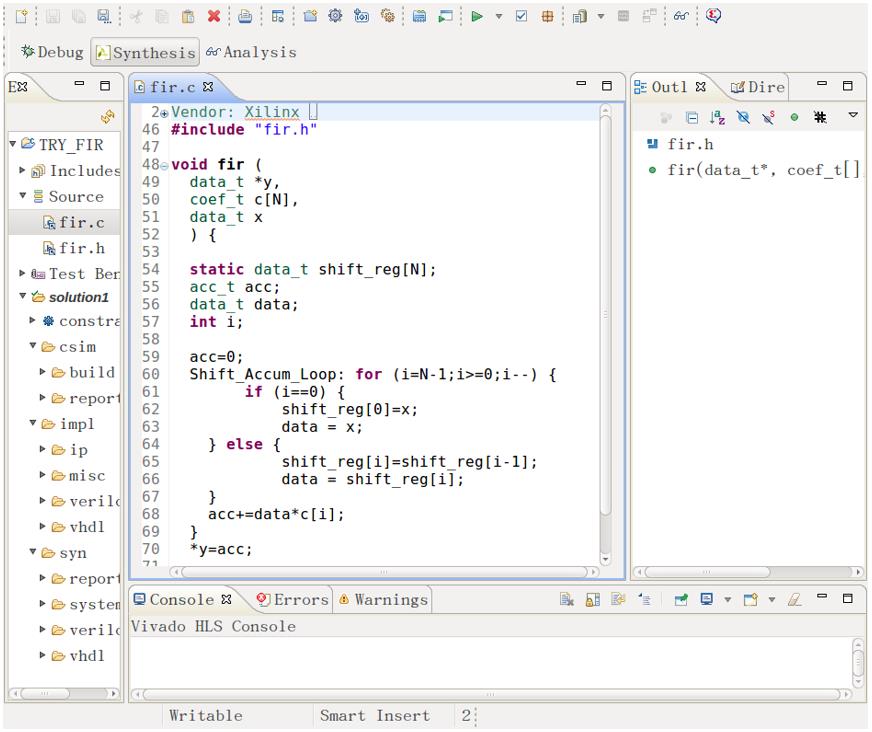

此时Vivado HLS的界面如图8.2.7所示。

图8.2.7 Vivado HLS工作界面

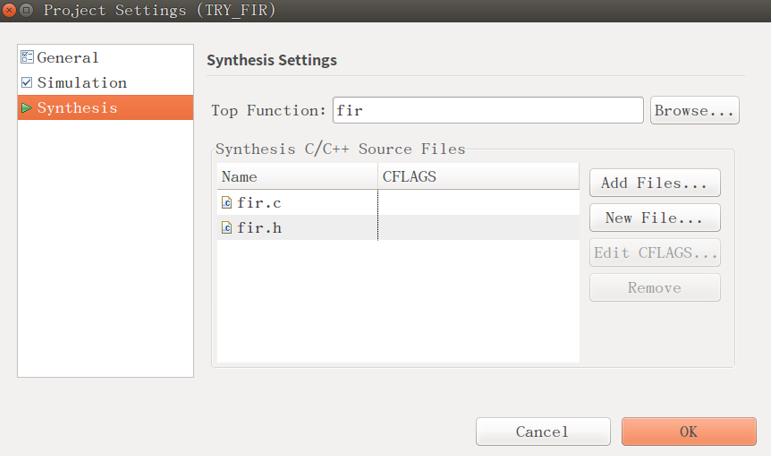

6、单击上图界面中的Project菜单,选择Project Setting…,在弹出的图8.2.8界面左侧选择Synthesis,并在右侧的Synthesis Setting界面中配置本工程的顶层函数为fir.c文件中的fir函数,随后单击右下角的OK按钮,确认选择。

图8.2.8 配置工程的顶层函数

7、单击工程界面上方的运行C语言综合按钮(图8.2.7所示界面上方的绿色三角形按钮),Vivado HLS将对C语言源文件进行分析和综合,产生硬件描述语言的文件输出。

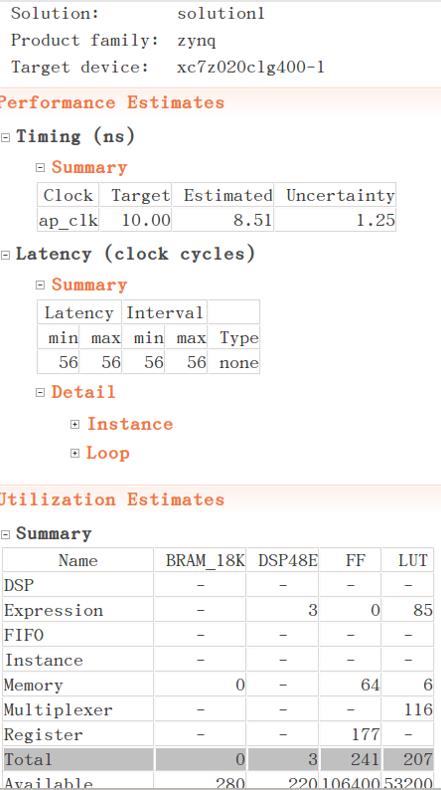

8、等待Vivado HLS完成综合,综合完成后会弹出图8.2.9所示的综合报告,其中显示了未做任何优化配置情况下,图8.2.7所示的C语言源码描述的有限冲击响应滤波器所占用的可编程逻辑器件资源、时钟、设计延迟、吞吐量等详细信息。

图8.2.9 综合报告

9、右键单击Explore栏的Test Bench,新建一个测脚本文件,命名为fir_test.c(该文件是图8.1.2所示的“C测试集文件”)。其源码如下。

#include <stdio.h> #include <math.h> #include "fir.h" int main () const int SAMPLES=600; FILE *fp; data_t signal, output; coef_t taps[N] = 0,-10,-9,23,56,63,56,23,-9,-10,0,; int i, ramp_up; signal = 0; ramp_up = 1; fp=fopen("out.dat","w"); for (i=0;i<=SAMPLES;i++) if (ramp_up == 1) signal = signal + 1; else signal = signal - 1; // Execute the function with latest input fir(&output,taps,signal); if ((ramp_up == 1) && (signal >= 75)) ramp_up = 0; else if ((ramp_up == 0) && (signal <= -75)) ramp_up = 1; // Save the results. fprintf(fp,"%i %d %d\\n",i,signal,output); fclose(fp); printf ("Comparing against output data \\n"); if (system("diff -w out.dat out.gold.dat")) fprintf(stdout, "*******************************************\\n"); fprintf(stdout, "FAIL: Output DOES NOT match the golden output\\n"); fprintf(stdout, "*******************************************\\n"); return 1; else fprintf(stdout, "*******************************************\\n"); fprintf(stdout, "PASS: The output matches the golden output!\\n"); fprintf(stdout, "*******************************************\\n"); return 0;

10、将图8.1.3中所示的“黄金参考”(即算法计算产生的标准答案)out.gold.dat文件拷贝到工程文件中。并用单击Explore栏的Test Bench,将黄金参考添加到工程中。

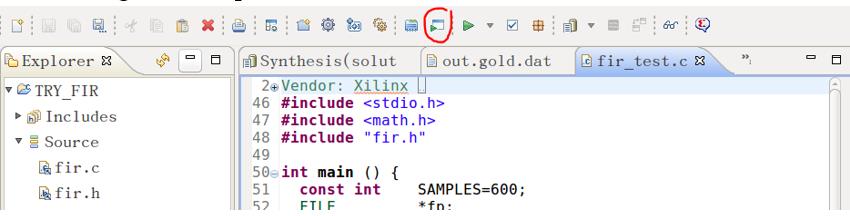

11、单击工程界面上方的Run C Simulation按钮,进行代码测试。根据上面的fir_test.c测试代码,若代码的运行结果与黄金参考一致,界面下方的Console窗口中将打印出PASS: The output matches the golden output! 的字样。

图8.2.10 C语言测试

12、至此为止,编写的代码所实现的算法如果功能正确,且在占用资源、设计延迟、吞吐量等方面都已经达到了设计目标,则可以导出高层次高层次综合器产生的硬件描述语言代码,以供Vivado在工程中调用该算法。

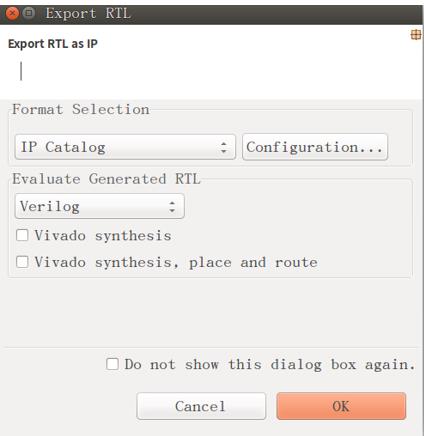

在Solution菜单中选择Export RTL,在弹出的界面如图8.2.11所示,选择最常用的生成IP方式导出,单击OK,Vivado HLS将产生可供Vivado调用的IP。界面下方的Console窗口中输出Finished export RTL时,就可以在…\\solution1\\impl\\ip文件夹下看到生成的IP.zip文件。

图8.2.11 输出硬件描述语言RTL配置界面

[原创www.cnblogs.com/helesheng]

以上是关于高层次综合器(Vivado HLS)的设计流程[原创www.cnblogs.com/helesheng]的主要内容,如果未能解决你的问题,请参考以下文章

基于高层次综合器(Vivado HLS)的硬件优化[原创www.cnblogs.com/helesheng]

数字信号处理相关3(Vivado HLS 开发流程简介(高级综合)(FPGA))

数字信号处理相关12(vivado高层次综合(high-level synthesis,HLS)学习日记 )