数字信号处理相关12(vivado高层次综合(high-level synthesis,HLS)学习日记 )

Posted Times_poem

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字信号处理相关12(vivado高层次综合(high-level synthesis,HLS)学习日记 )相关的知识,希望对你有一定的参考价值。

来自:https://blog.csdn.net/hehequan/article/details/78742117

参考xilinx文档:

ug902

ug998

https://china.xilinx.com/support/documentation/sw_manuals/ug998-vivado-intro-fpga-design-hls.pdf

一、前言

架不住老大的淫威,本作者很不情愿的开始了HLS学习,这篇学习日记实际是重新表述文件1(详见后面的参考列表)中的一些重点内容。我认为高层次综合还是没有纯verilog来的爽,虽然纯Verilog耗时耗力,但是设计自由度很高,再有我比较怀疑HLS到底能不能设计出最优方案,设计效率到底有多高?

二、学习日记

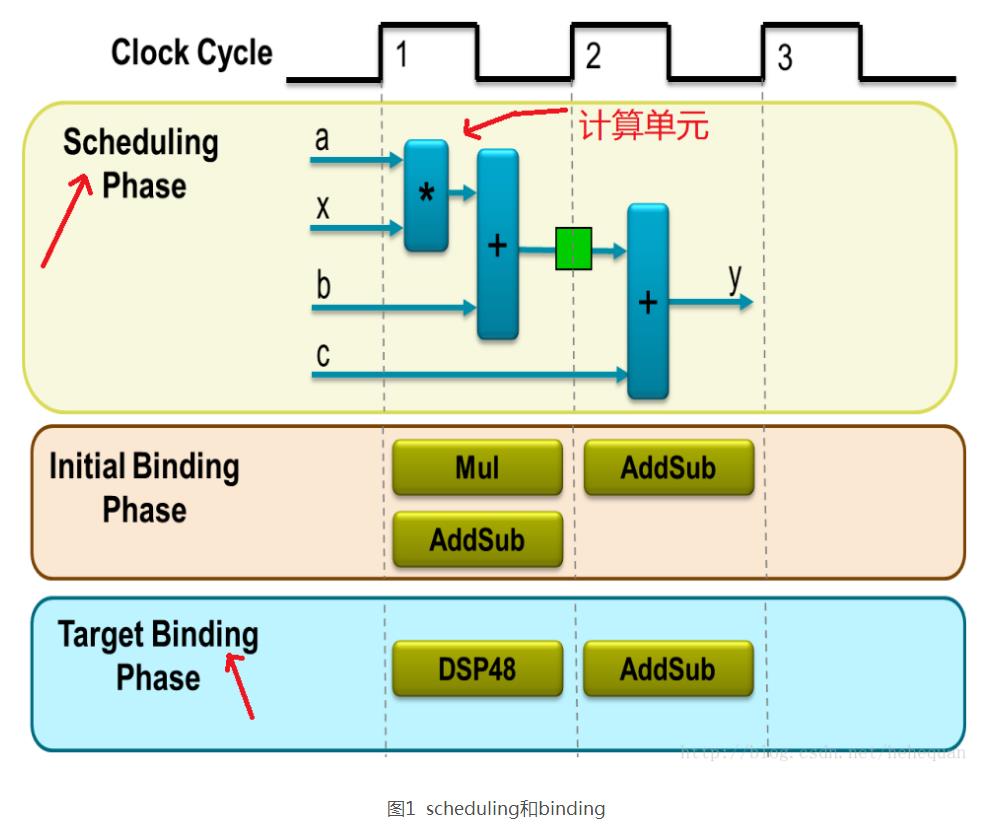

1、高层次综合中两个重要的process:scheduling 和binding

scheduling 和binding暂时理解为部署和捆绑。部署应该是把算法中的加减乘除等计算单元拆解出来然后依照计算顺序安排到对应的clock cycle,如图1所示。捆绑则是使用具体的硬件资源实现这些计算单元。

2、对于for循环的实现

For循环的实现有这么几个特点:

(1) 函数的形参被看作是verilog module的input和output,如图2所示。

(2) 综合后的层次结构跟综合前层次结构相同,也就是说如果主函数包含一个子函数,那么,综合后对应一个主模块和一个子模块,并且也是包含关系。

(3) for循环变成滚动计算(rolled),也就是说在for循环中每一次循环的计算过程都是相同的,那么只要用硬件实现一次,然后时分复用。

(4) 数组被综合成block ram,如果数组是函数的形参,那么它会被综合成block ram的接口。

3、设计方案的性能衡量指标

Area

Latency

Initiation interval(缩写成II)

以上指标的具体说明请参考文件1(详见后面的参考列表)p10页。

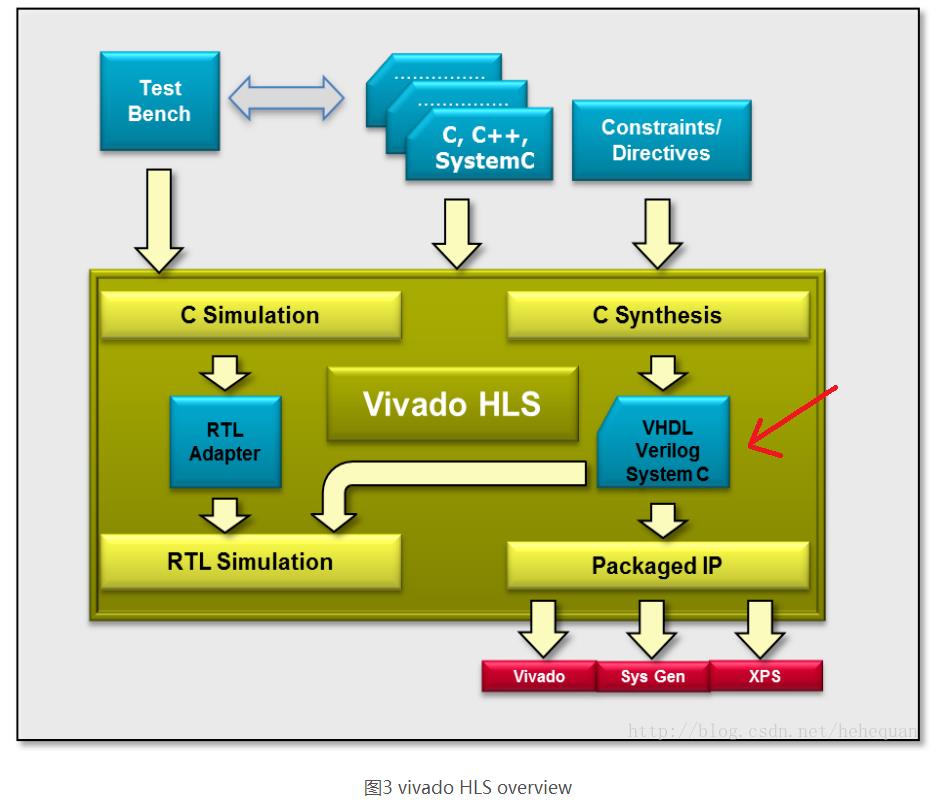

4、将C或C++ 翻译成 VHDL或Verilog

从图3中可以看出C、C++被翻译成了VHDL或Verilog,毕竟HDL语言是最贴近RTL级的描述。

5、不支持的C语言语法

(1)system calls。一些依赖操作系统的函数是不能被综合的,比如printf,还有文件操作函数open()、time()、sleep()等。

(2)动态内存分配。例如malloc()、alloc()、free()。

(3)递归函数。

(4)指针的限制:通常不支持指针类型强制转换(pointer casting),除了pointer casting between native C types(不会翻译..);指针数组必须指向一个大小一定的空间。

(5)不支持标准模板库(standard templatelibraries),因为模板库中常常包含递归函数和动态内存分配。

三、总结

了解到这里,得出的结论是HLS还是比较麻烦的,没我想的这么智能,FPGA内部大型算法可以尝试用HLS,至于外部接口等等还是Verilog吧。

四、参考列表

文件1 ug902-vivado-high-level-synthesis(xilinx官网可下载)

以上是关于数字信号处理相关12(vivado高层次综合(high-level synthesis,HLS)学习日记 )的主要内容,如果未能解决你的问题,请参考以下文章