存储系统

Posted yimumengke

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了存储系统相关的知识,希望对你有一定的参考价值。

第三章 存储系统

【复习提示】

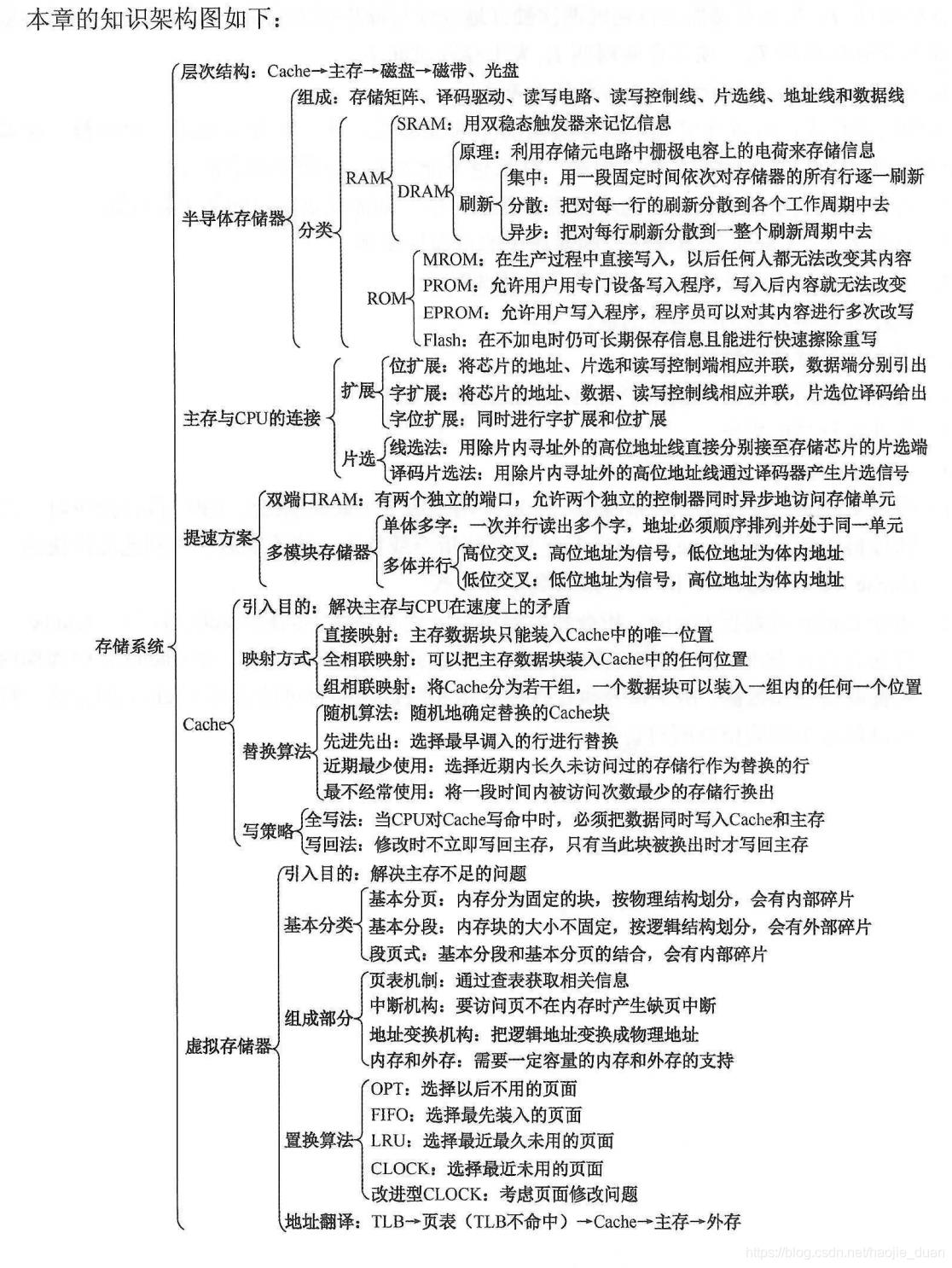

本章是历年考査的重点,特别是有关 Cache和存储器扩展的知识点容易出综合题。此外,存储器的分类与特点,存储器的扩展(芯片选择、连接方式、地址范围等),低位交叉存储器,Cache的相关计算与替换算法,虚拟存储器与快表也容易出选择题。读者应在掌握基本原理和理论的基础上,多结合习题进行练习复习,以加深和巩固。另外,读者还需掌握存在 Cache和TLB的计算机中的地址翻译与 Cache映射问题,该问题在《操作系统考研复习指导》中有详细说明。

本章有两个难点:一是 ache映射规律、容量计算及替换特性;二是交又存储器访问时间和访问效率。二者都可与第5章的大题综合,或与第6章总线访问内存时间的计算问题综合。

在学习本章时,请读者思考以下问题:

- 1)存储器的层次结构主要体现在何处?为何要分这些层次?计算机如何管理这些层次?

- 2)存取周期和存取时间有何区别?

- 3)在虚拟存储器中,页面是设置得大一些好还是设置得小一些好?

请读者在学习本章的过程中寻找答案,本章末尾会给出参考答案。

3.1 存储器概述

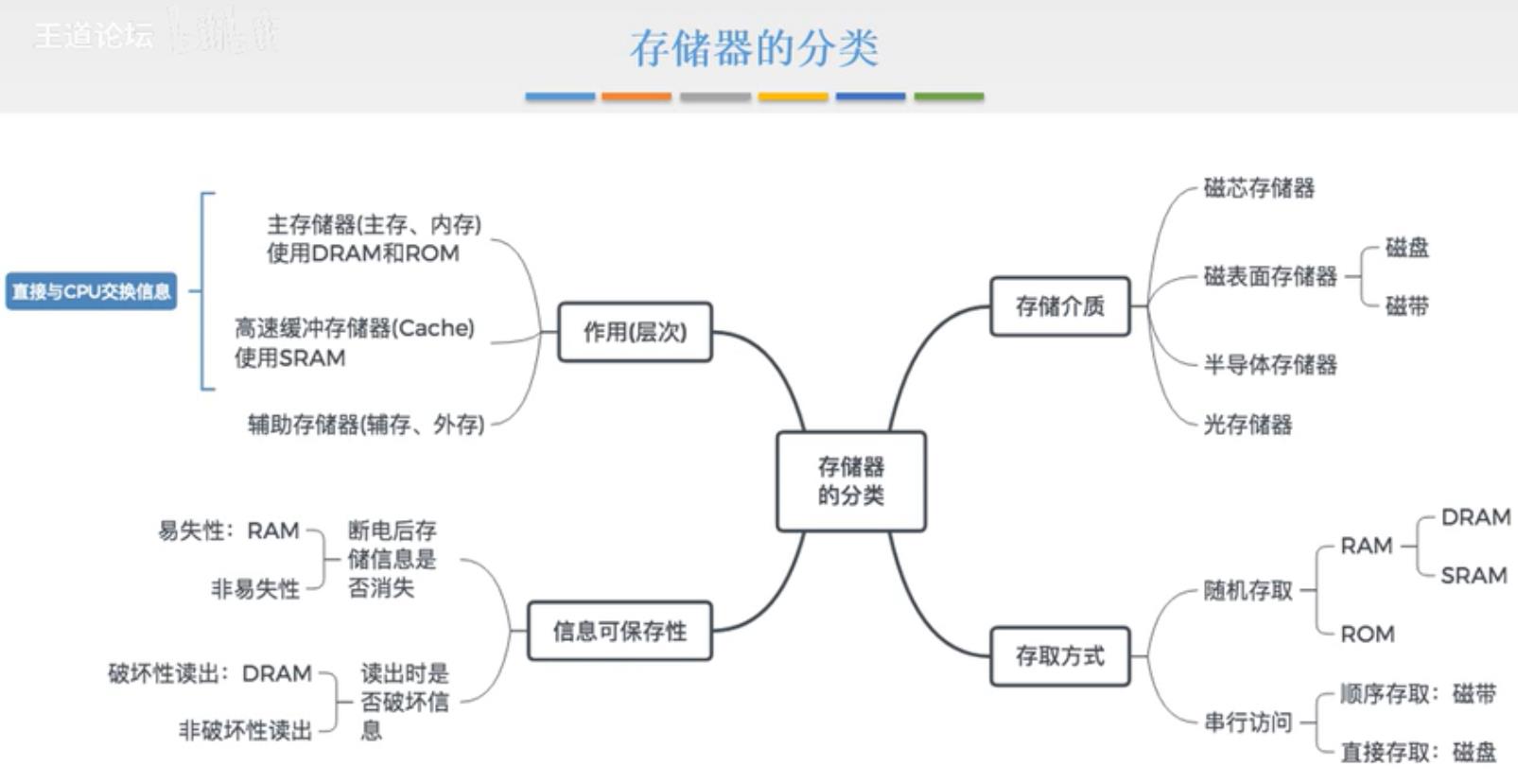

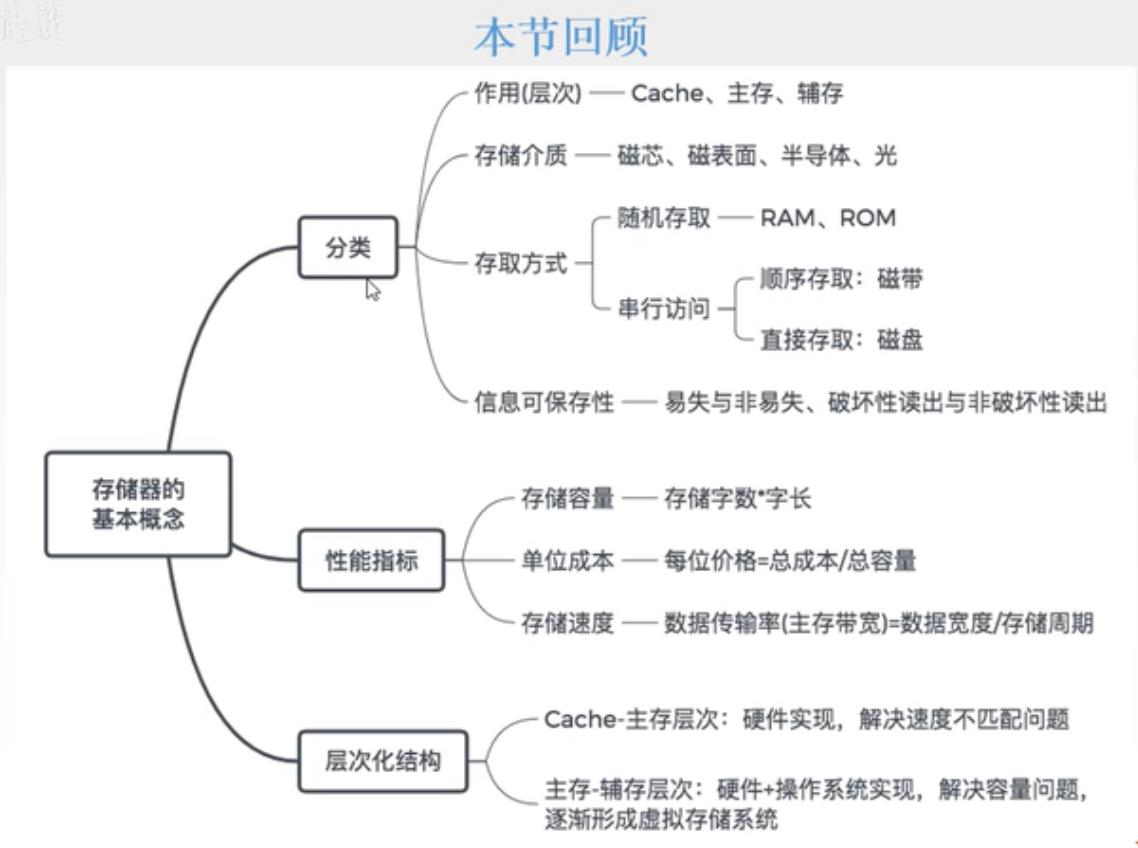

3.1.1 存储器的分类

相联存储器的基本原理是把存储单元所存内容的某一部分作为检索项(即关键字项)去检索该存储器,并将存储器中与该检索项符合的存储单元内容进行读出或写入。所以它是 按内容或地址进行寻址的,价格较为昂贵。 一般用来制作TLB、相联 Cache等。

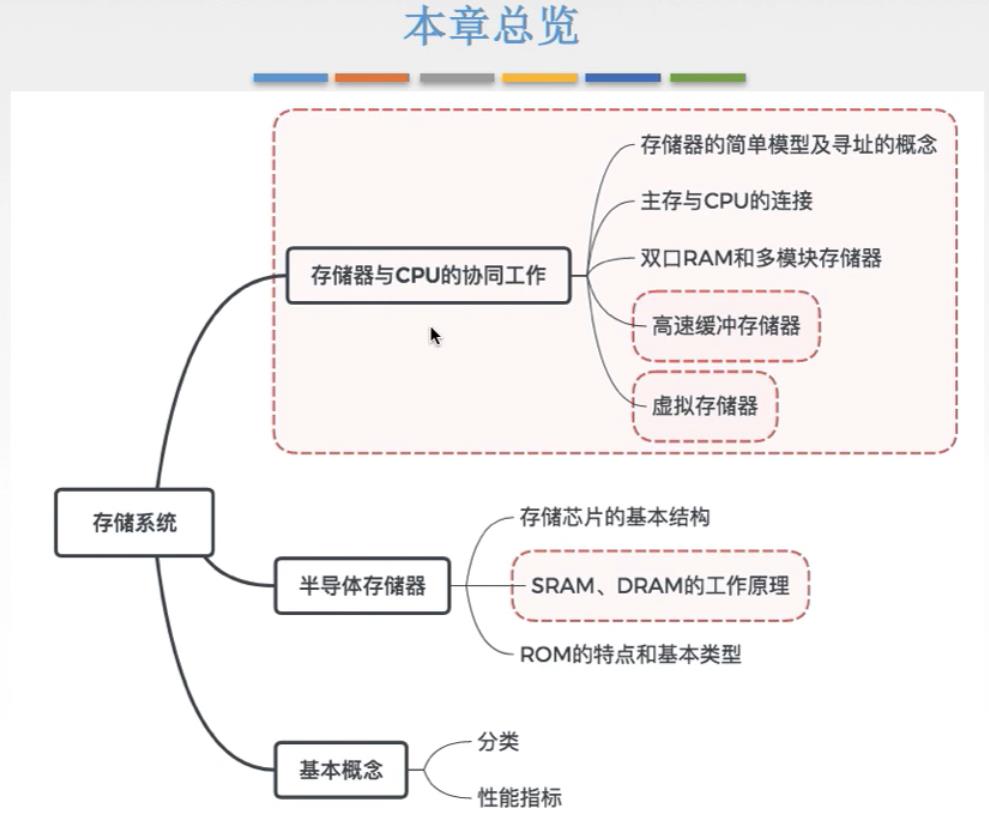

按在计算机中的作用对存储器分类:

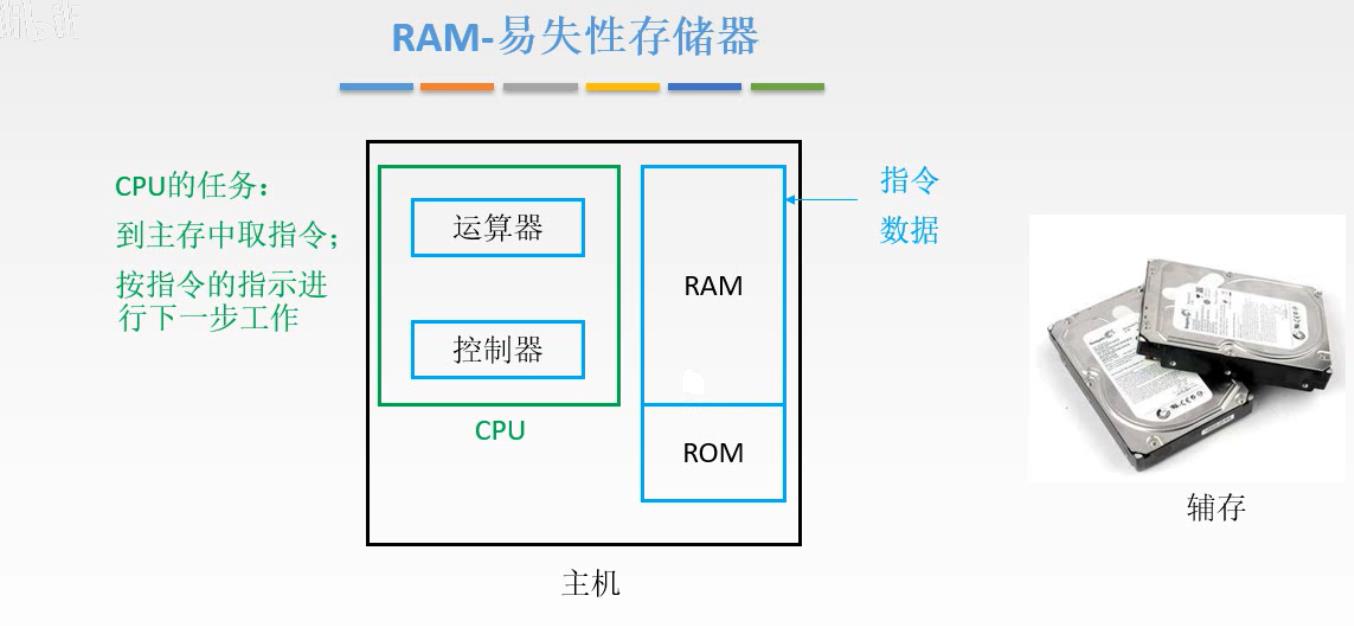

- 1> 主存储器,简称主存。CPU可以直接随机地对其进行访问,也可以和高速缓存器及辅助存储器交换数据。

- 2> 辅助存储器,简称辅存,不能与CPU直接相连,用来存放当前暂时不用的程序和数据

- 3> 高速缓冲存储器,位于主存和CPU之间,用来存放正在执行的程序段和数据

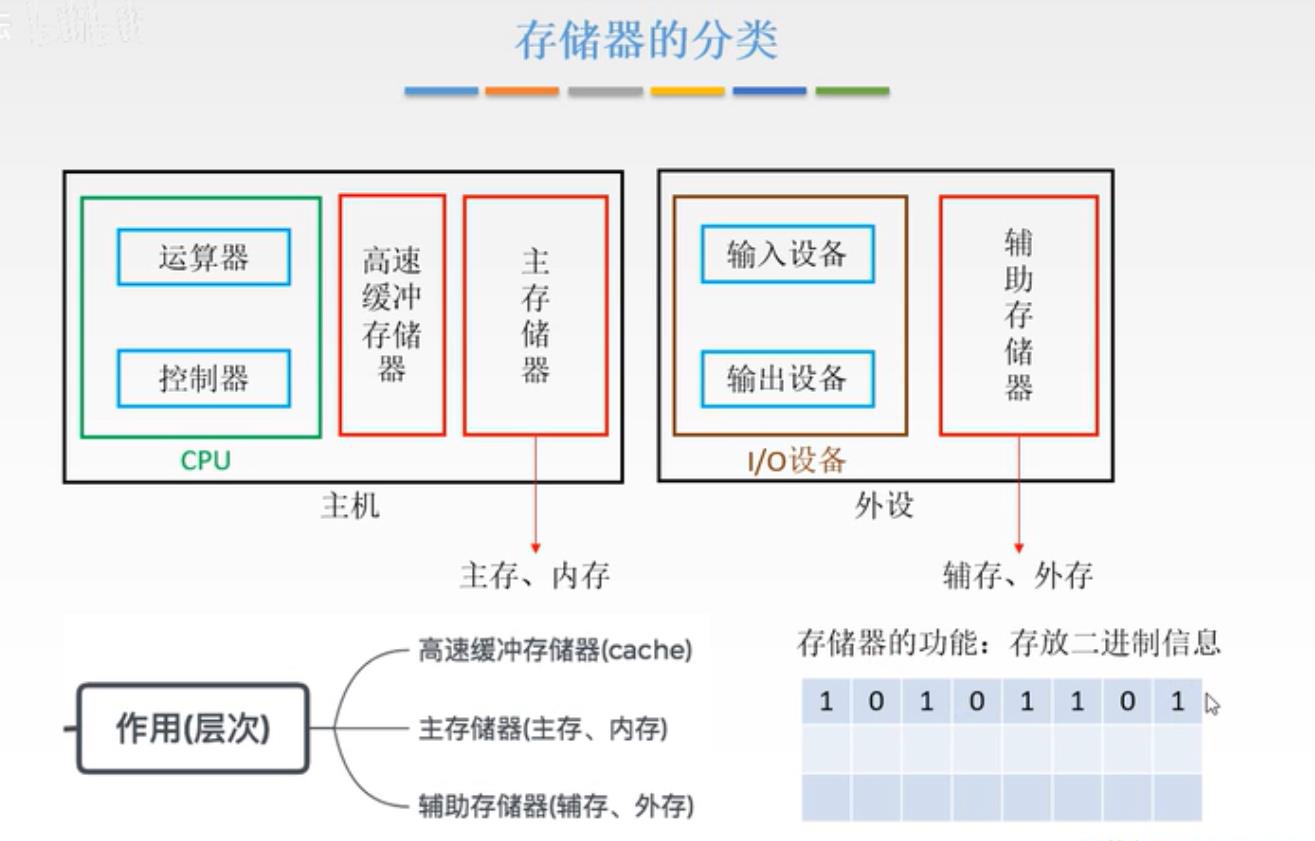

按存储介质分类:

- 磁表面存储器(磁盘,磁带),磁心存储器半导体存储器(MOS型存储器,双极存储器)和光存储器(光盘)。

按存取方式分类:

- 1> 随机存储器(RAM)。存储器的任何一个存储单元的内容都可以随机存取,而且存取时间与存取单元的物理位置无关,主要用作主存或高速缓冲存储器。

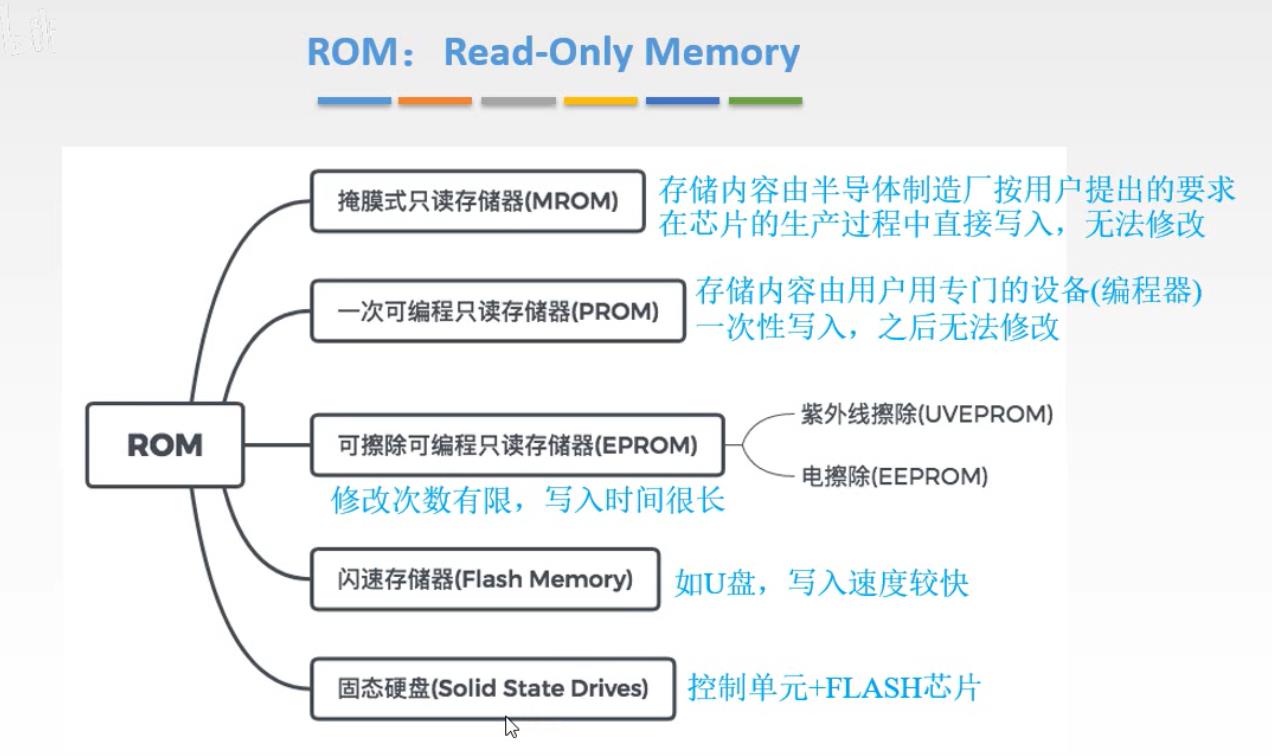

- 2> 只读存储器(ROM)。存储器的内容只能随机读出而不能写入。。即使断电,内容也不会丢失。

- 3> 串行访问存储器。对存储单元进行读/写操作时,需按其物理位置的先后顺序寻址,包括顺序存取存储器(如磁带)与直接存取存储器(如磁盘)。

按信息的可保存性分类:

- 断电后,存储信息即消失的存储器,称为易失性存储器,如RAM。断电后信息仍然保持的存储器,称为非易失性存储器,如ROM,磁表面存储器和光存储器。若某个存储单元所存储的信息被读出时,原存储信息被破坏,则称为破坏性读出;若读出时,被读单元原存储信息不被破坏,则称为非破坏性读出。具有破坏性读出性能的存储器,每次读出操作后,必须紧接一个再生的操作,以便恢复被破坏的信息。

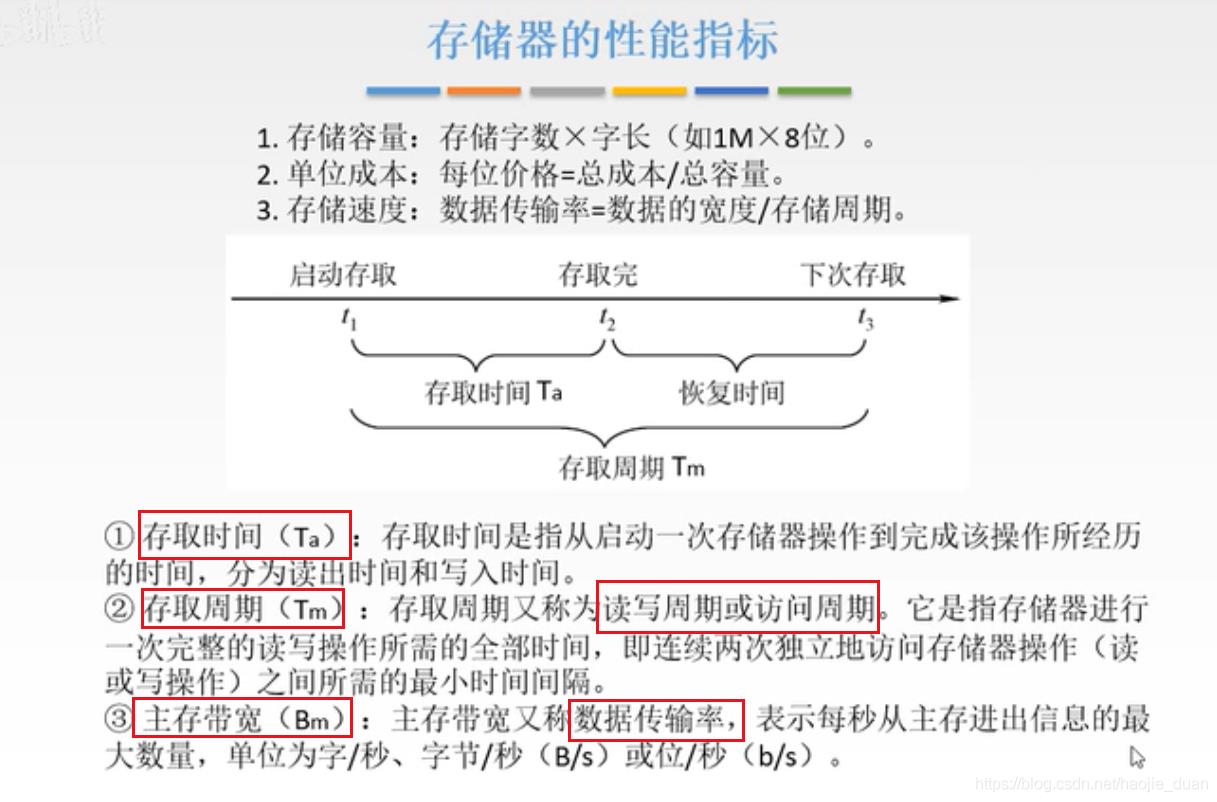

3.1.2 存储器的性能指标

存储器的性能指标,有3个主要的性能指标,存储容量,单位成本和存储速度

- 1> 存储容量:存储字数*字长

- 2> 单位成本:每位价格=总成本/总容量

- 3> 存储速度:数据传输率=数据的宽度/存储周期

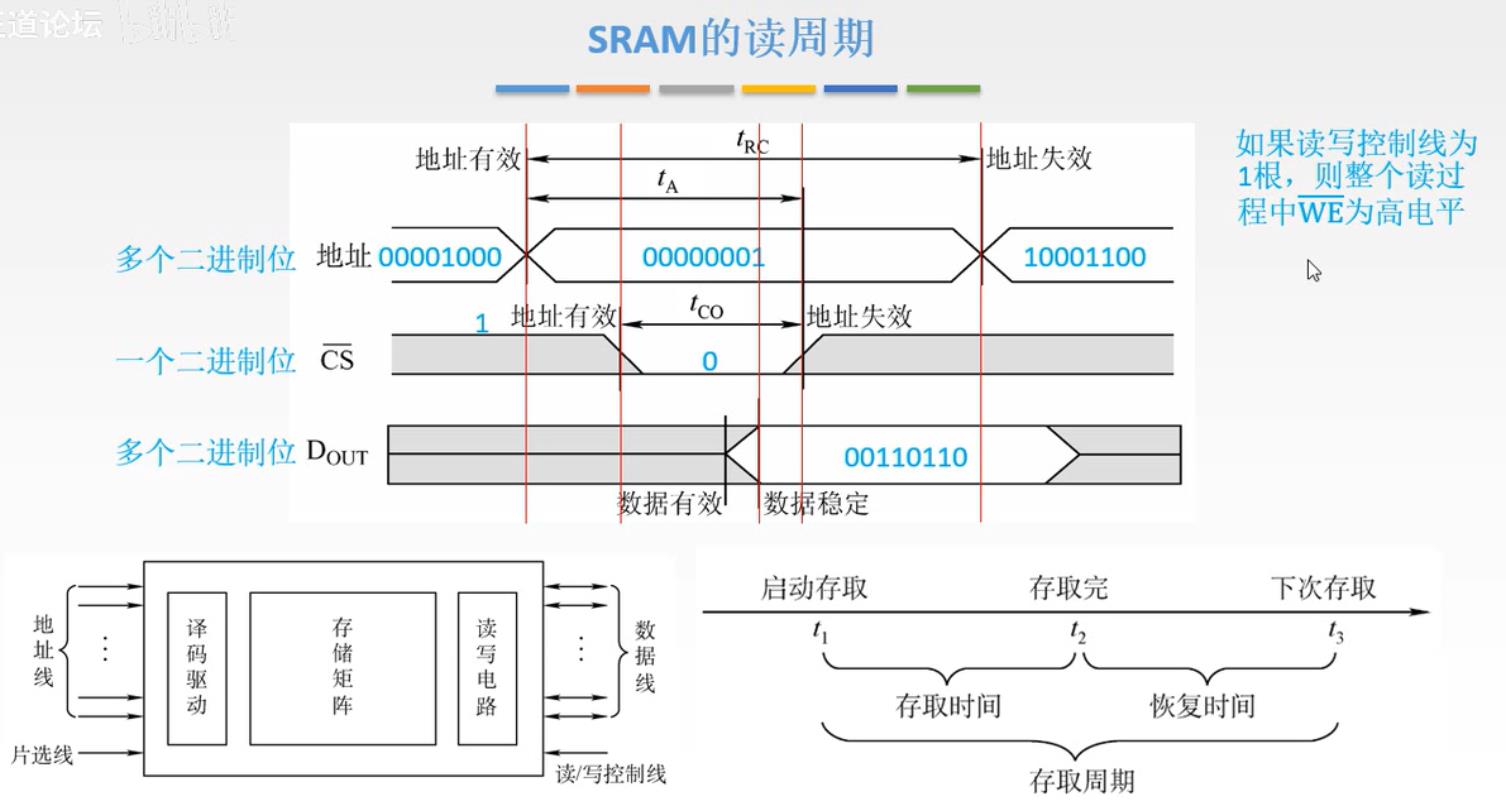

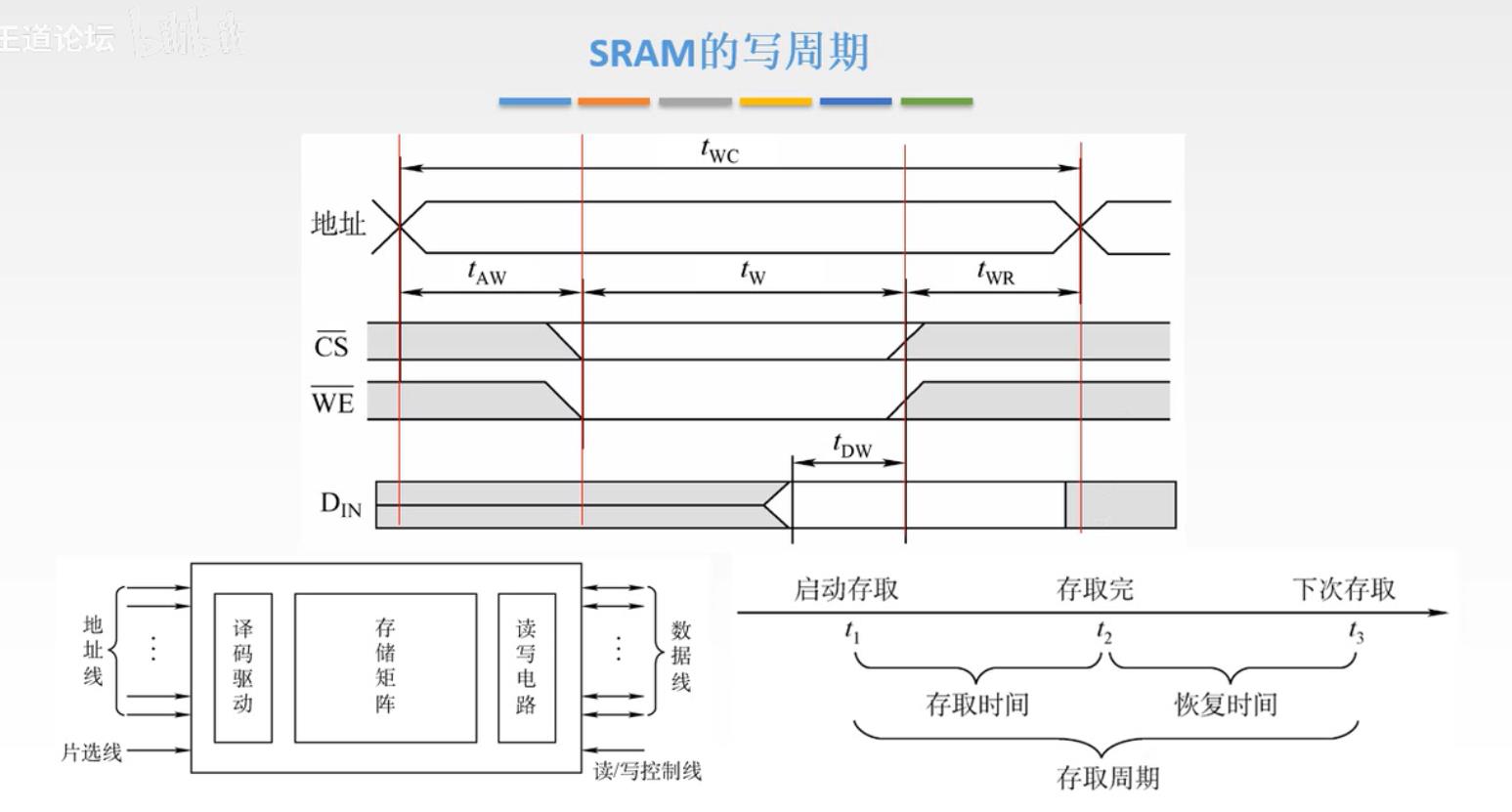

存取时间:存取时间时指从启动一次存储器操作到完成该操作所经历的时间,分为读出时间和写入时间。

存取周期:它是指存储器进行一次完整的读写操作所需的全部时间,即连续两次独立访问存储器操作(读或写操作)之间所需的最小时间间隔。

主存带宽:主存带宽又称数据传输率,表示每秒从主存进出信息的最大数量,单位为字/秒,字节/秒

存取时间不等于存储周期,通常存储周期大于存取时间。因为任何一种存储器,在读写操作之后,总要有一段恢复内部状态的复原时间。

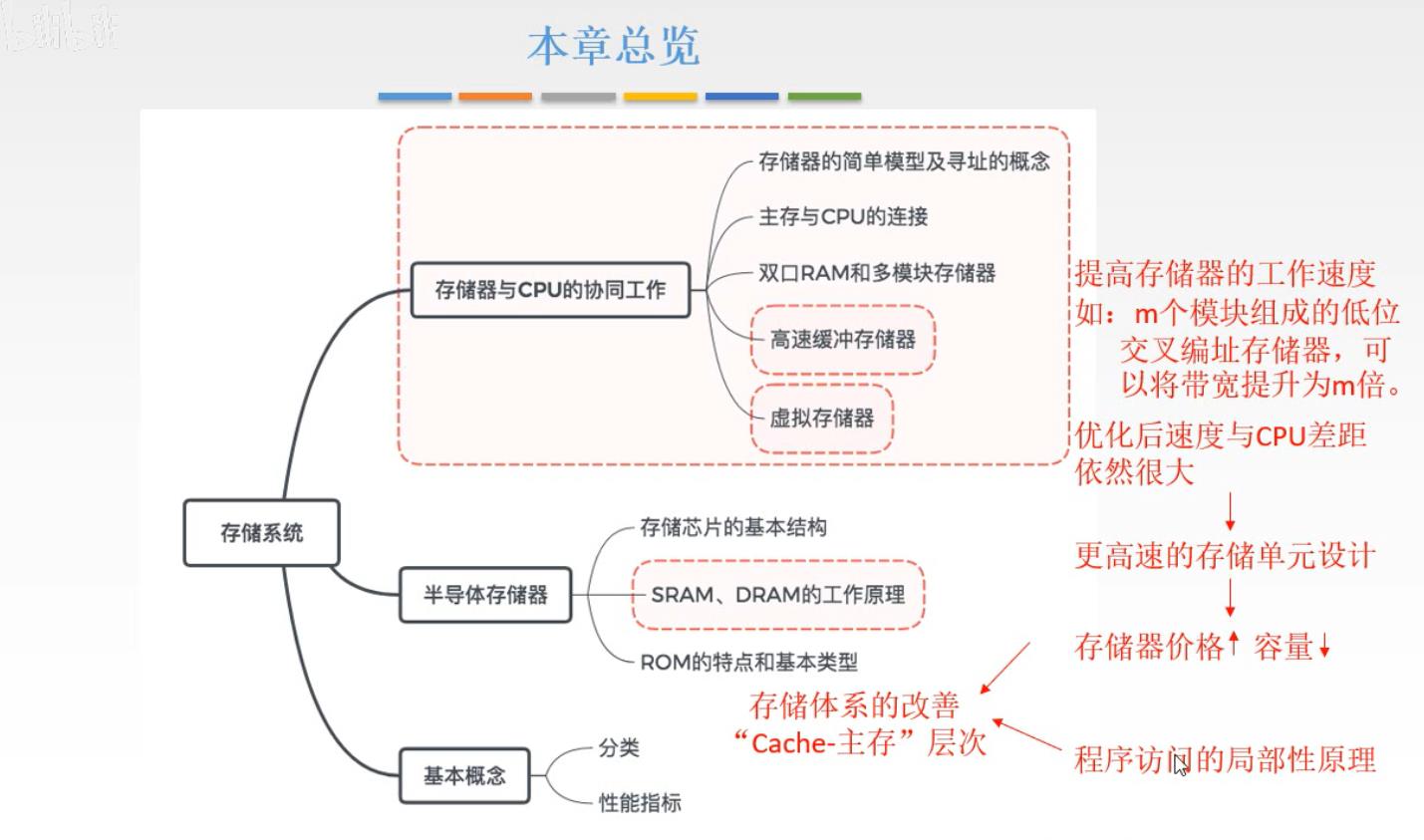

3.2 存储器的层次结构

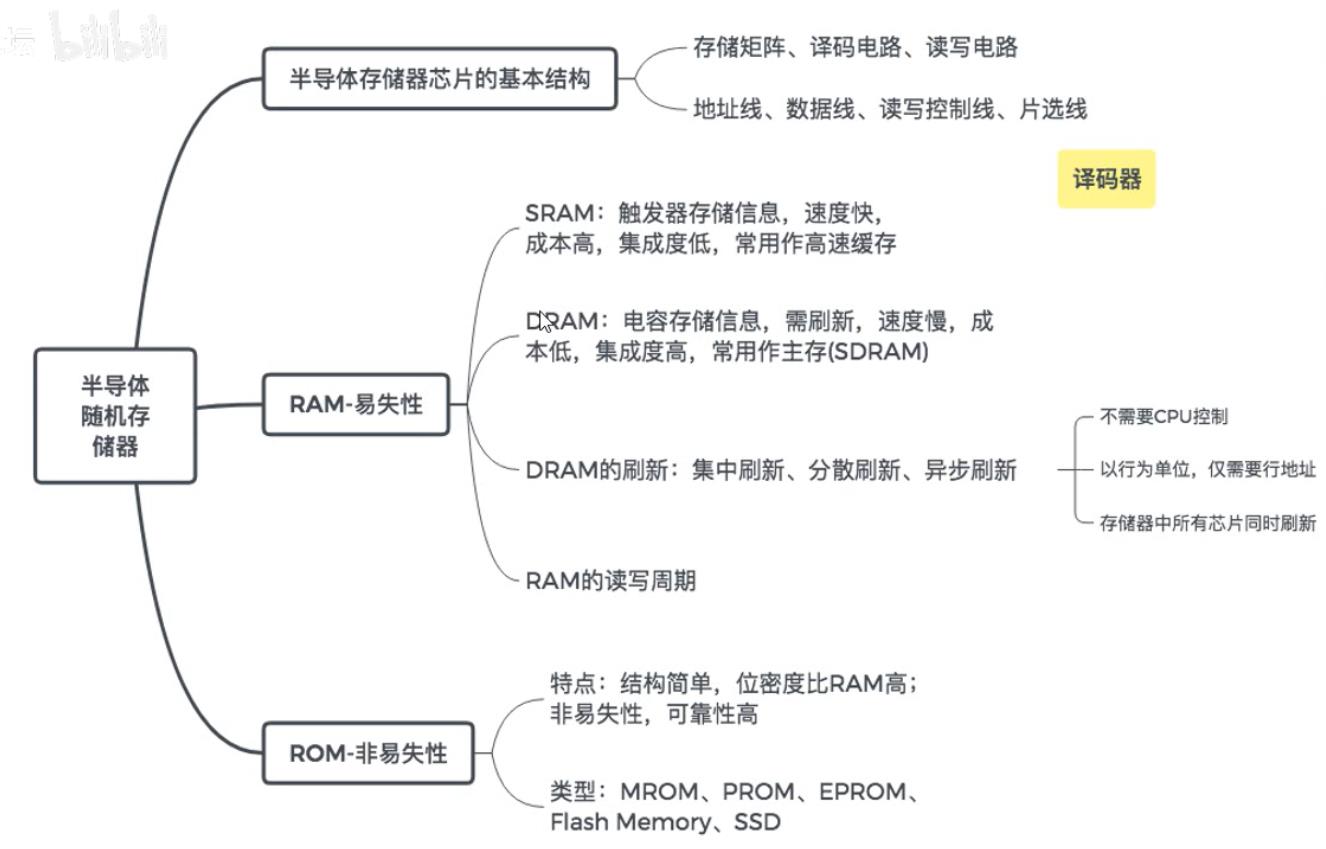

3.3 半导体随机存储器

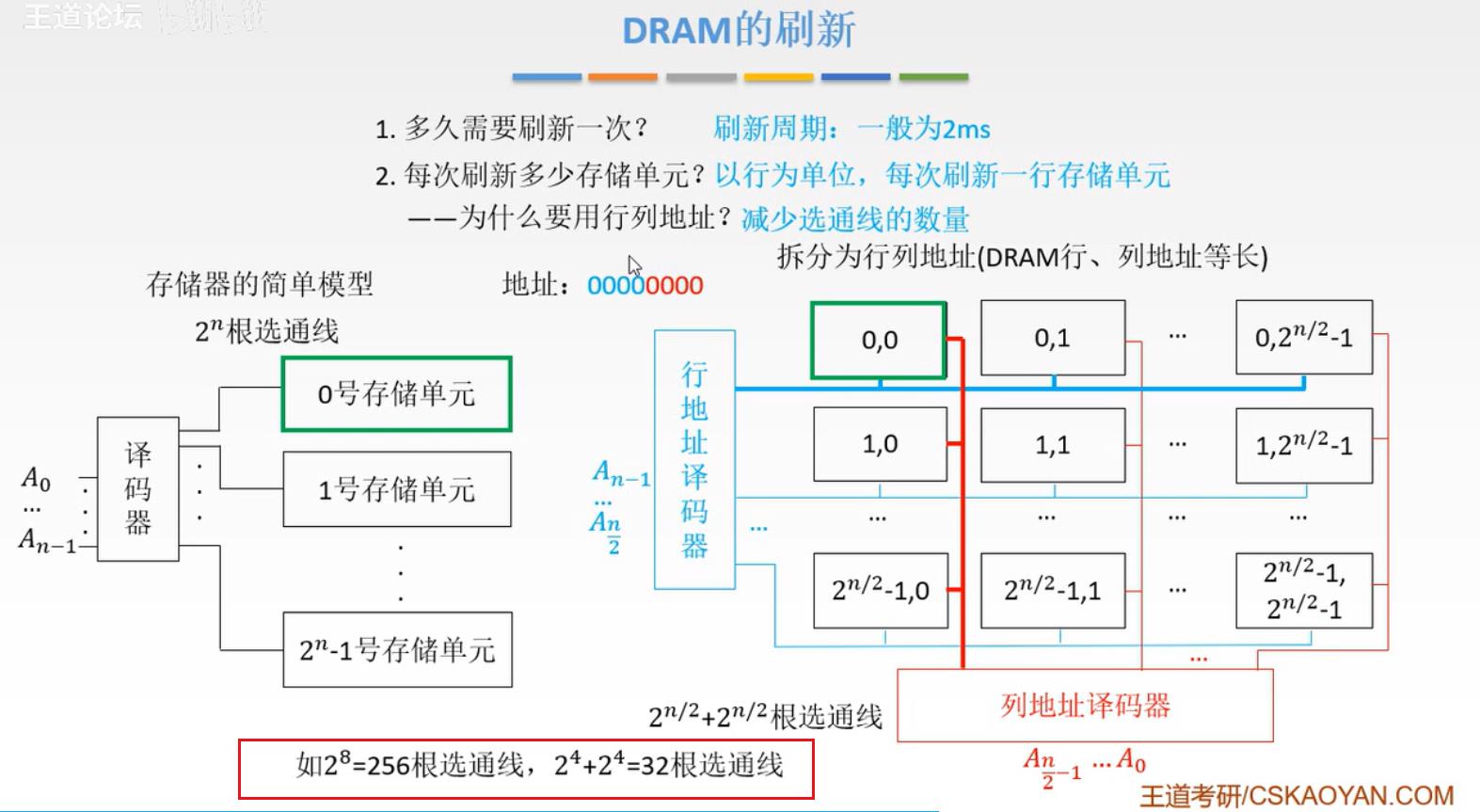

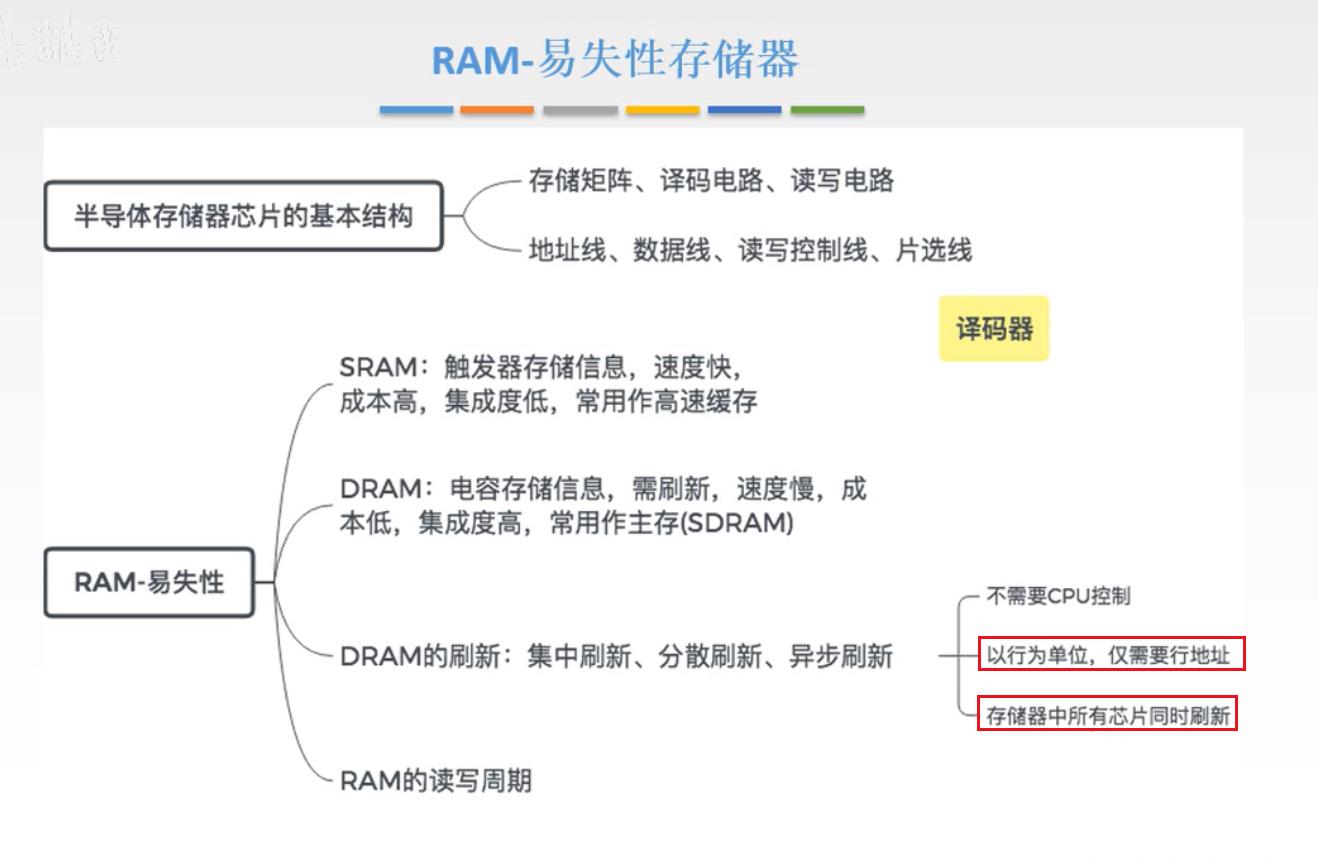

3.3.1 SRAM和DRAM

3.3.2 只读存储器

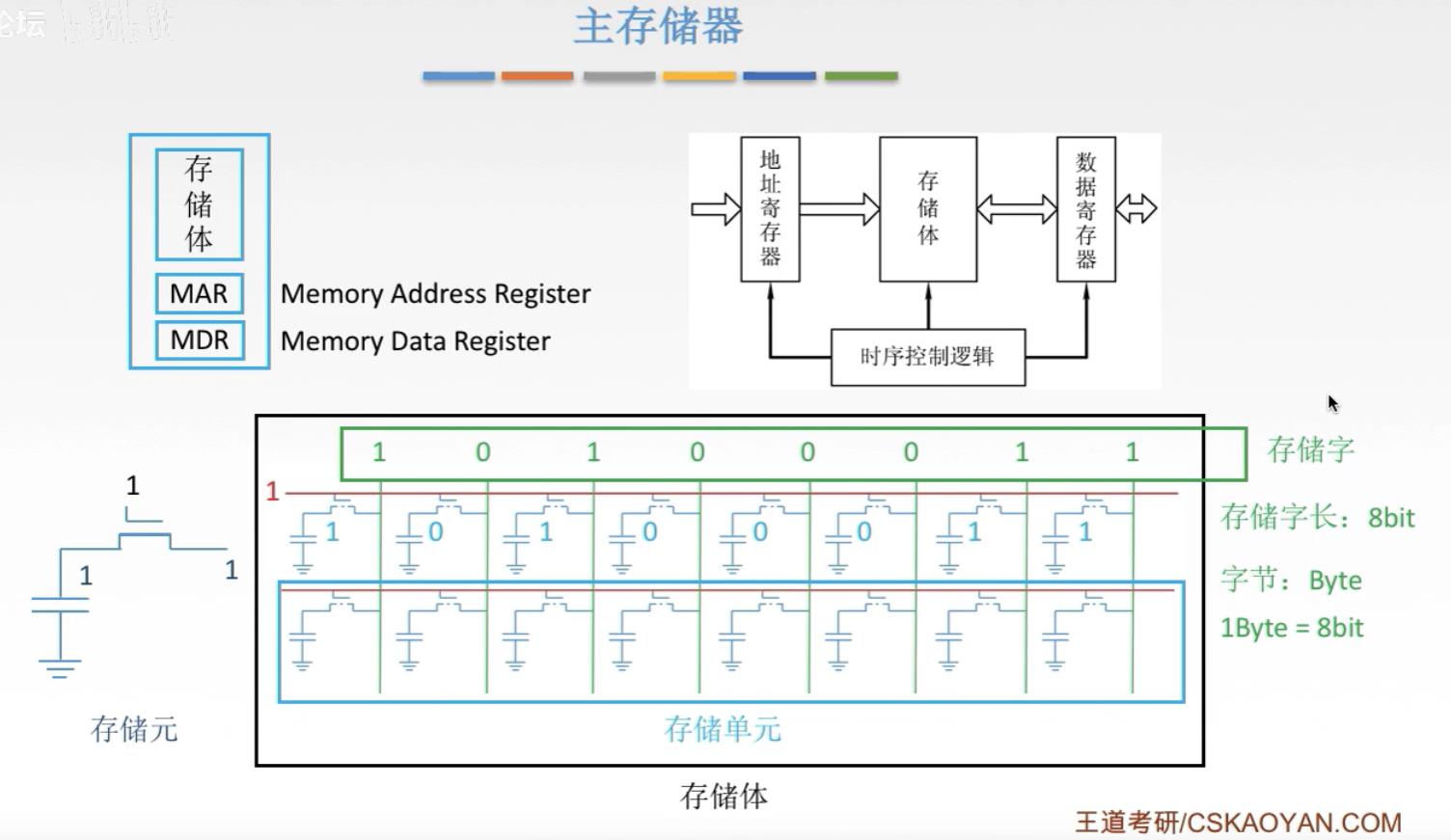

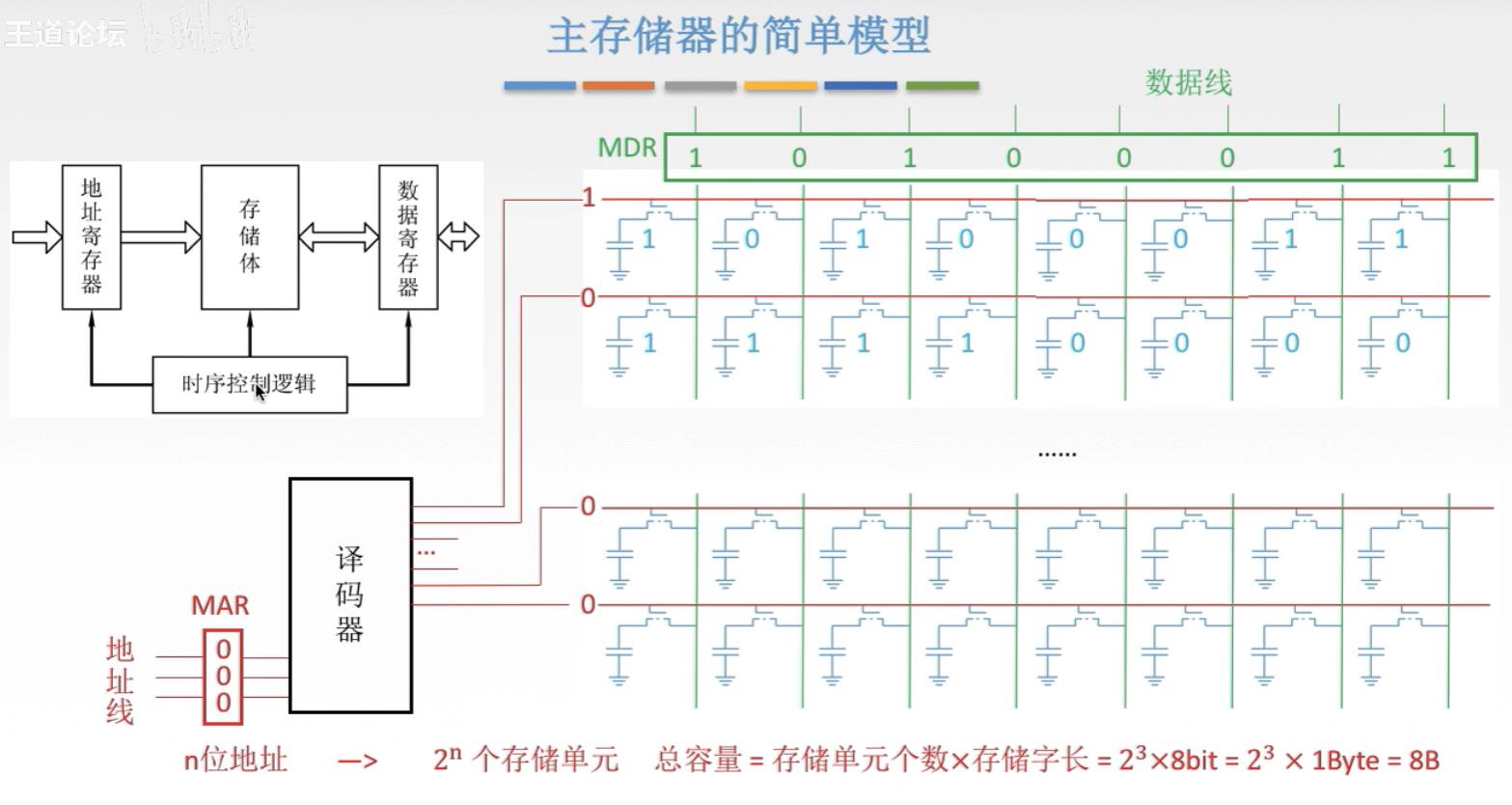

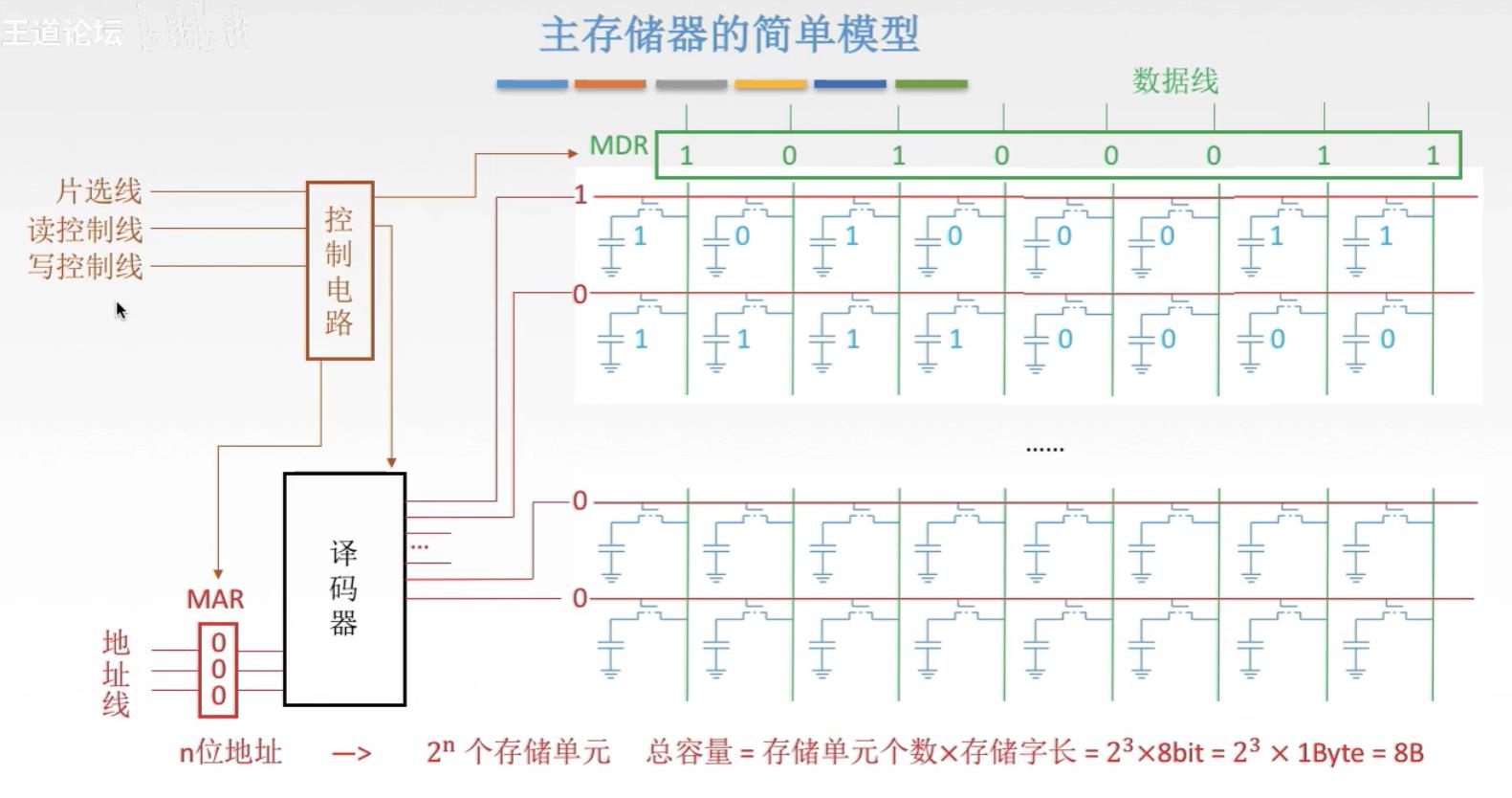

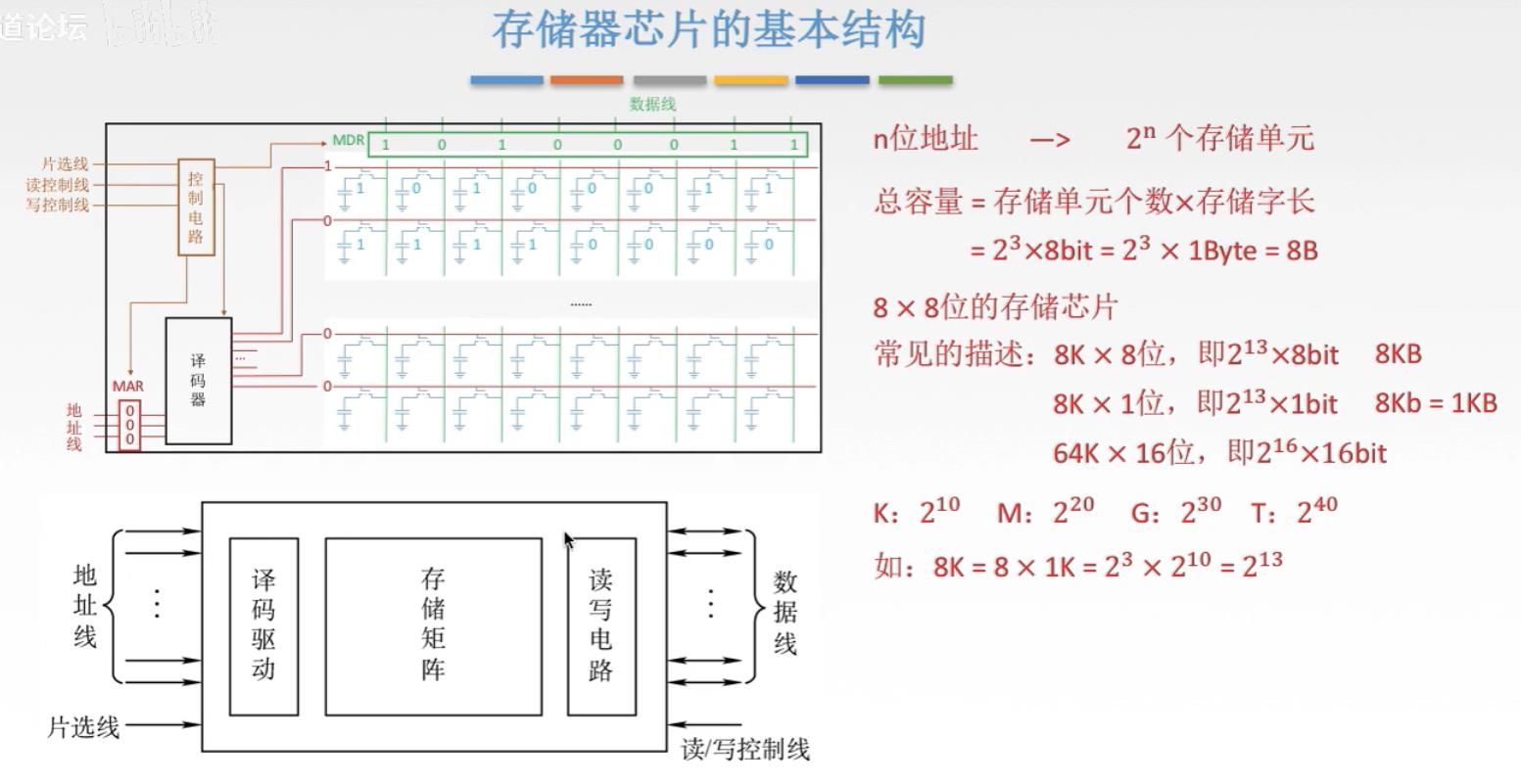

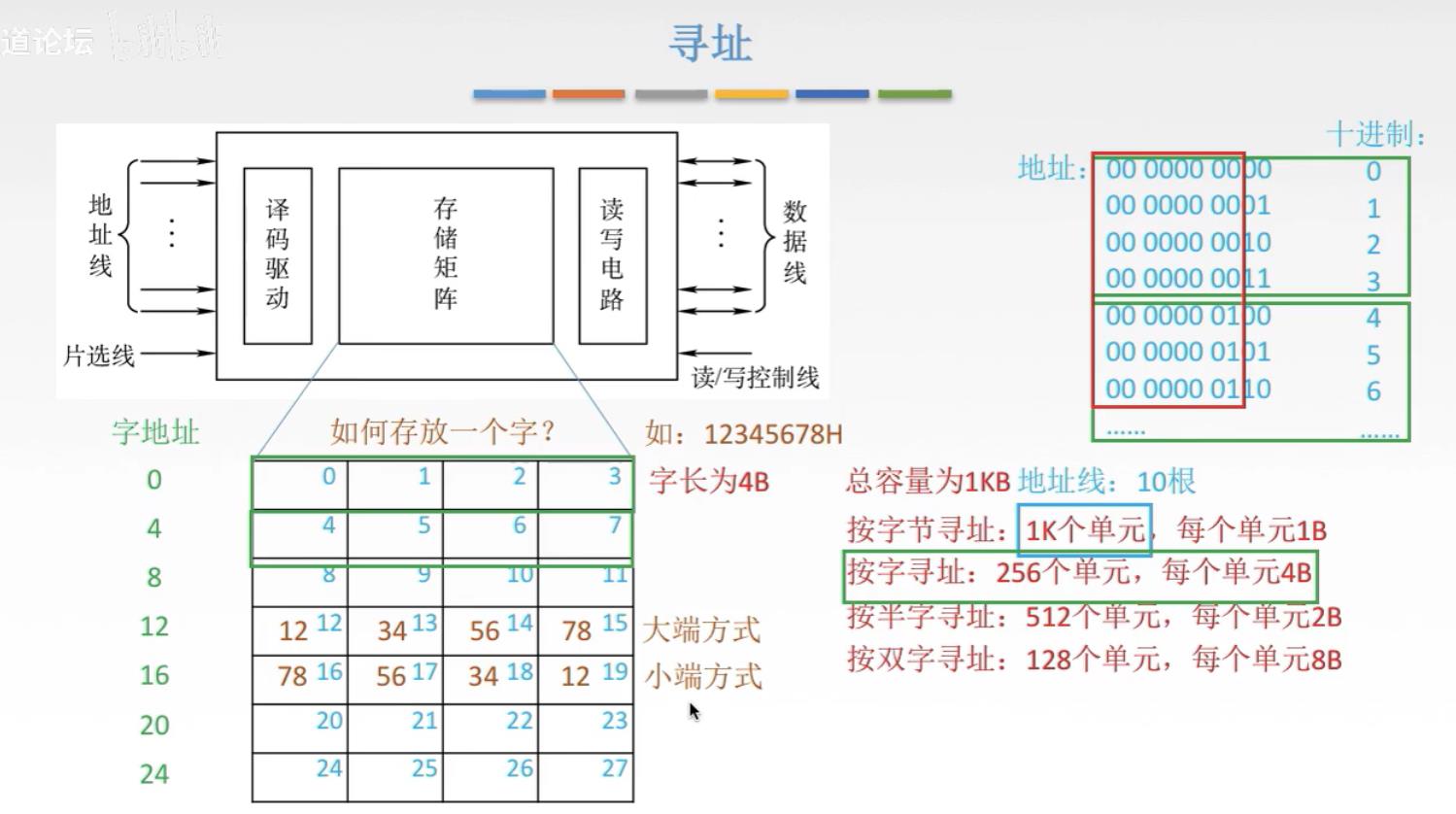

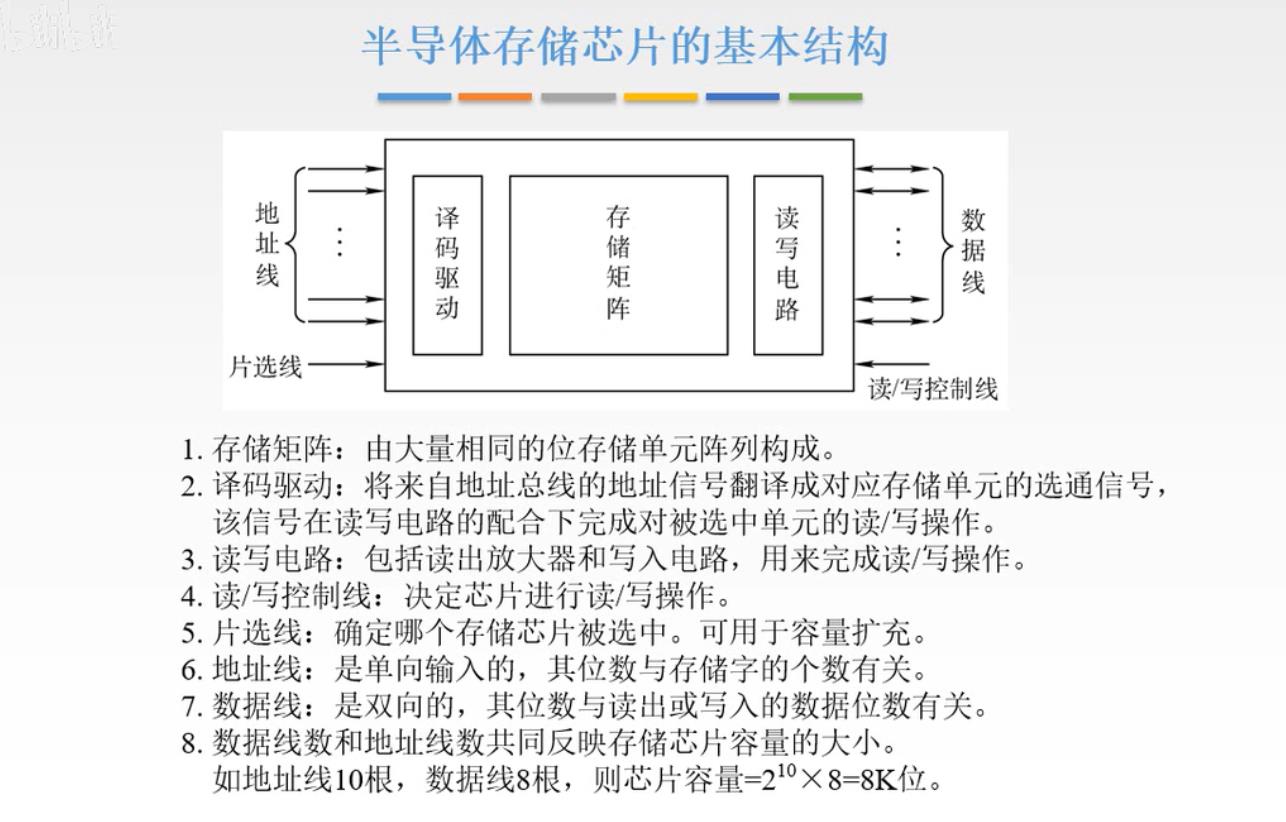

3.3.3 主存的基本组成(存储系统)

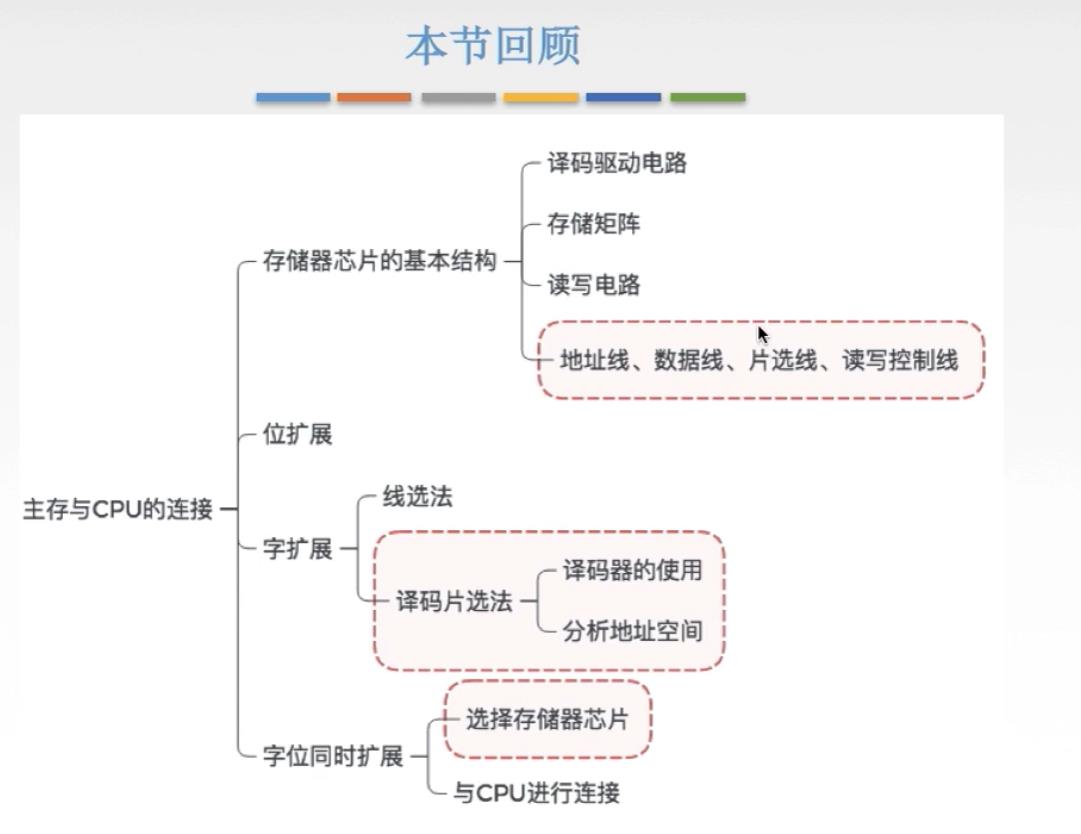

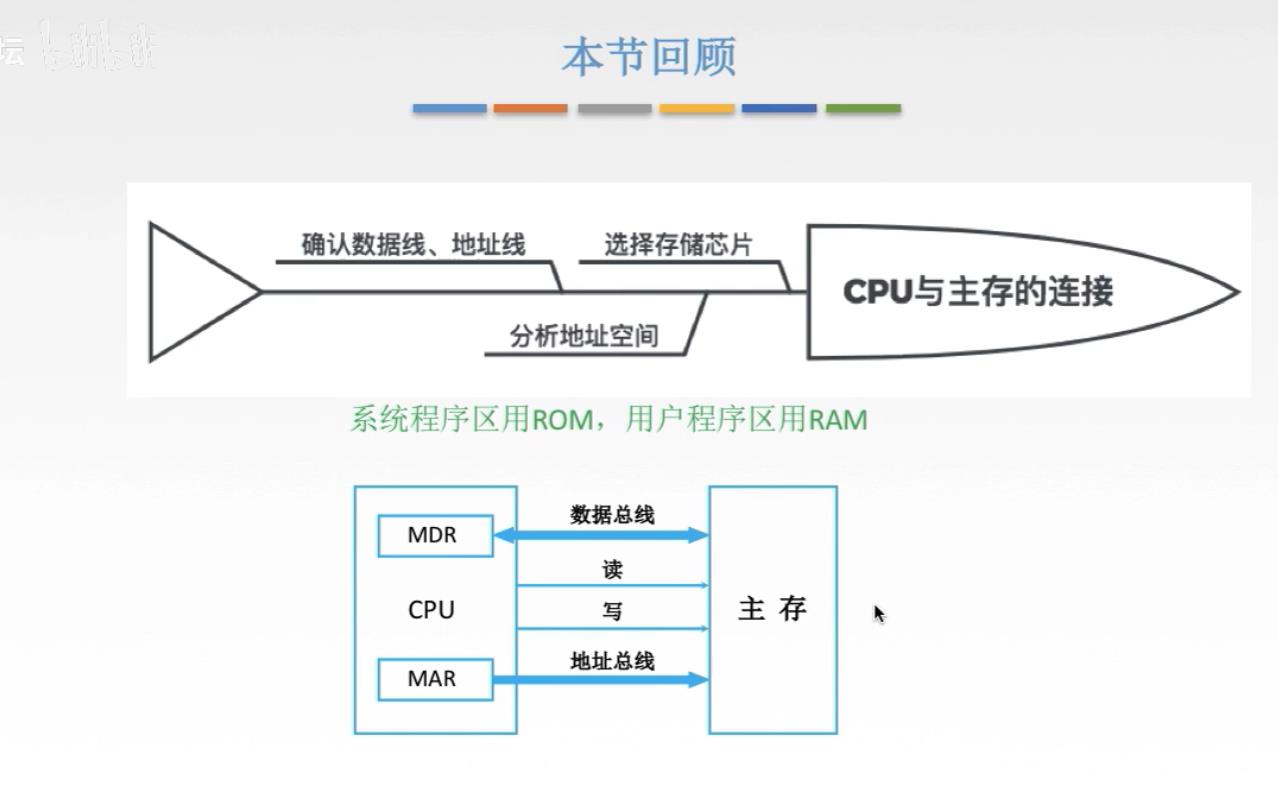

3.4 主存储器与CPU的连接

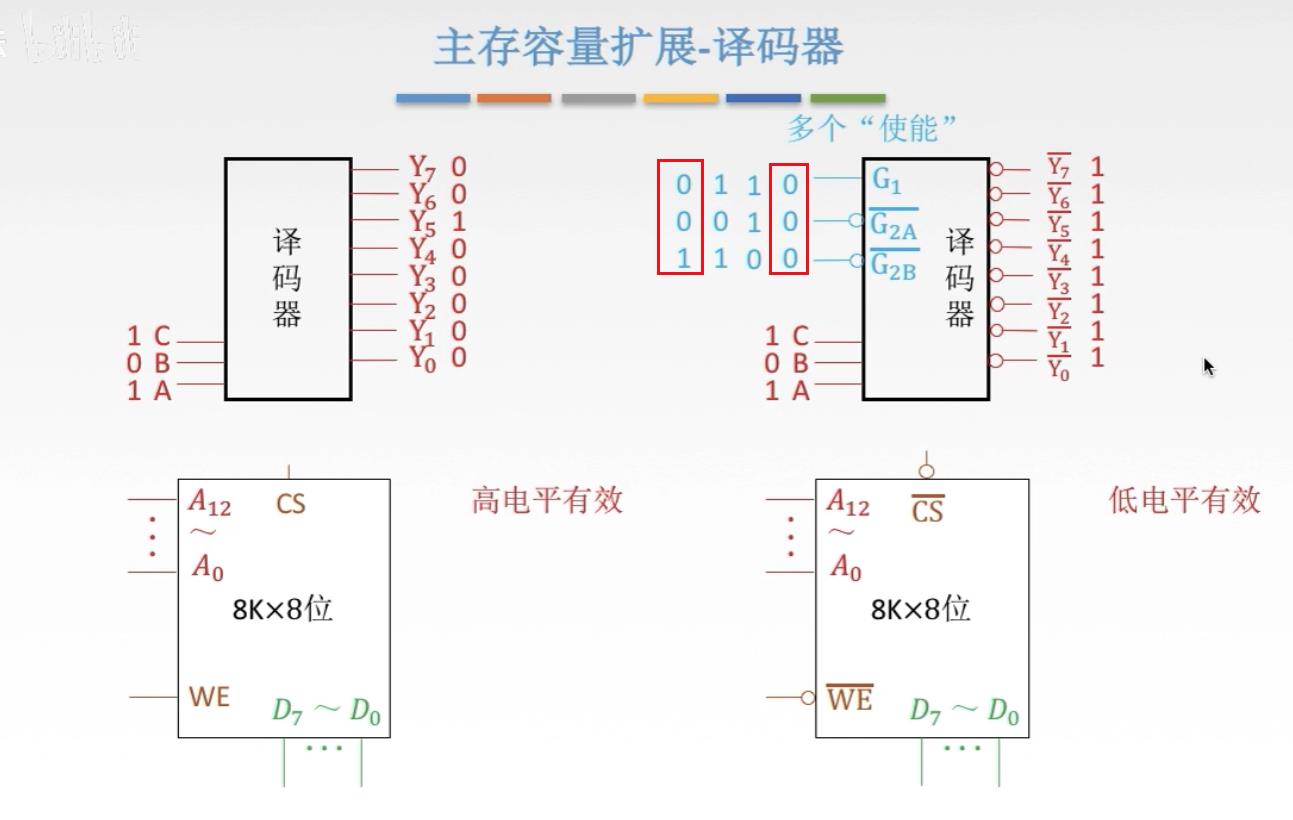

3.4.2 主存容量的扩展

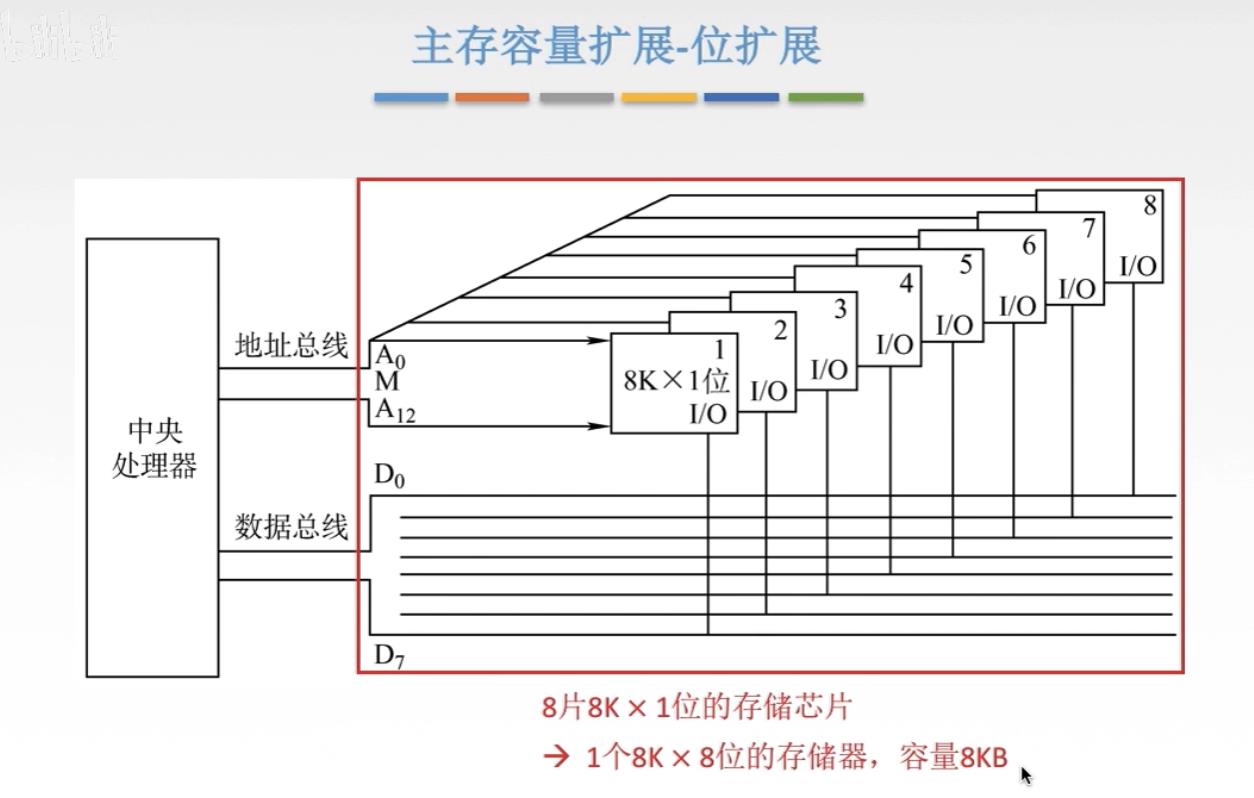

1.位扩展

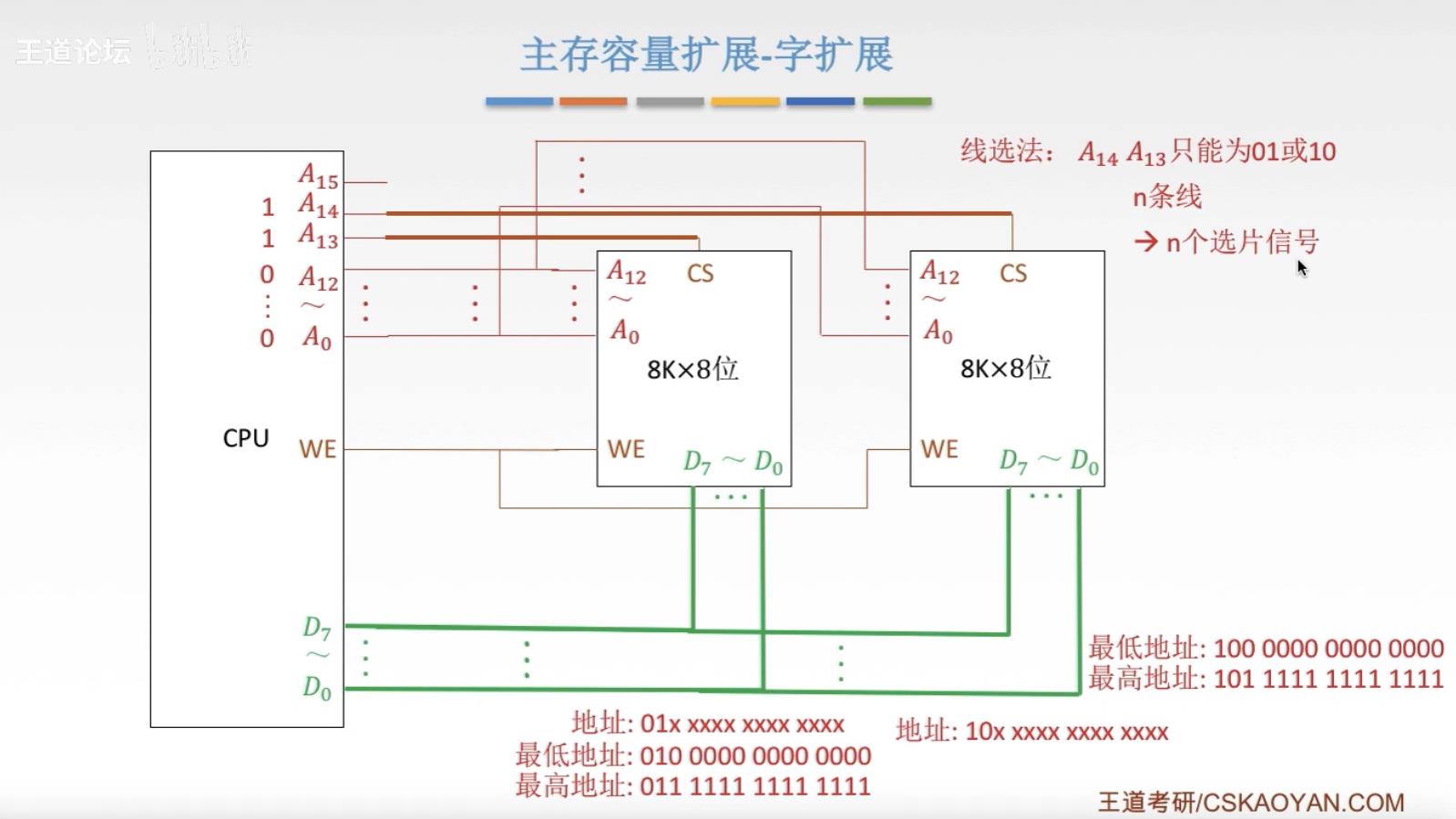

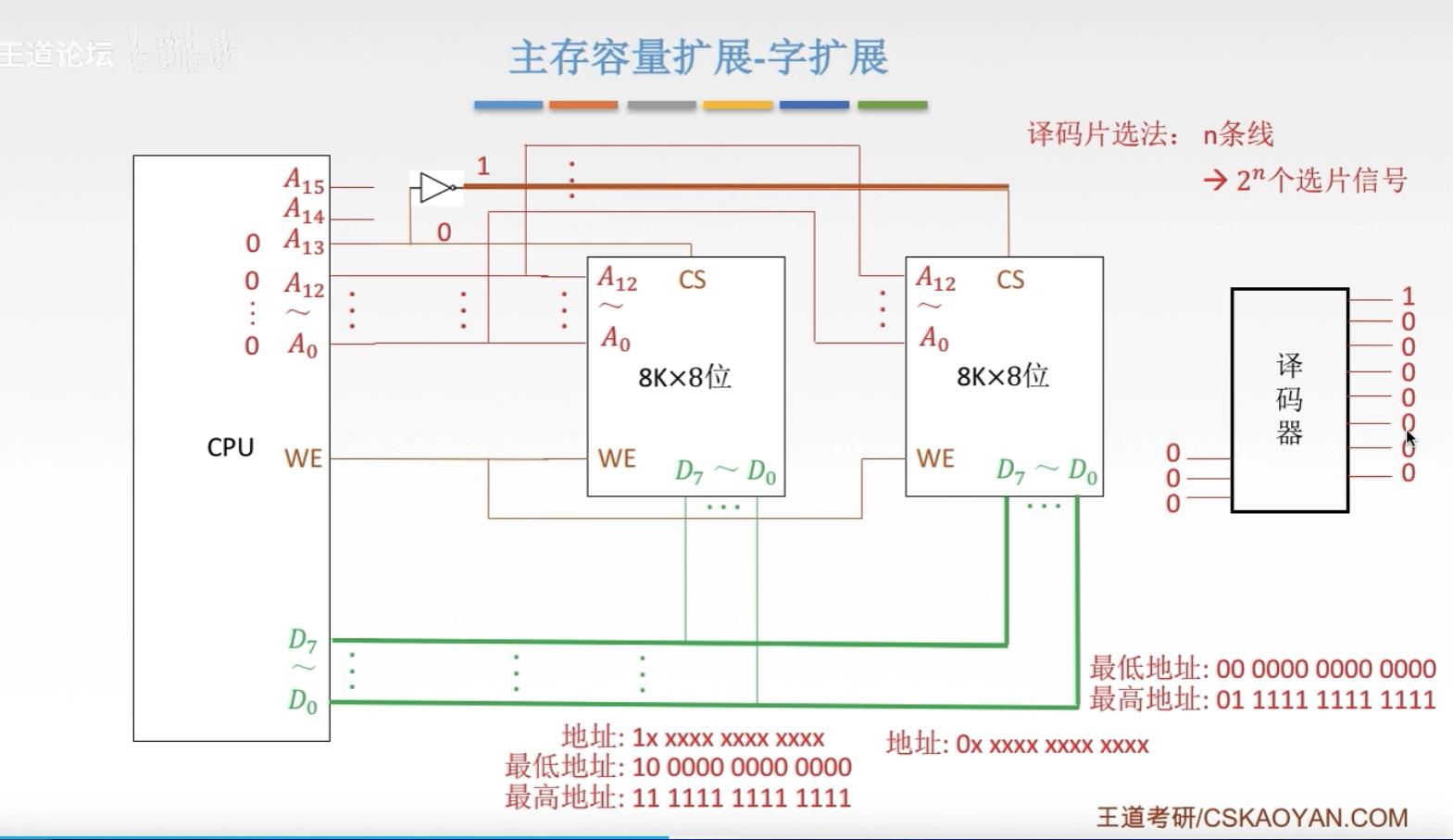

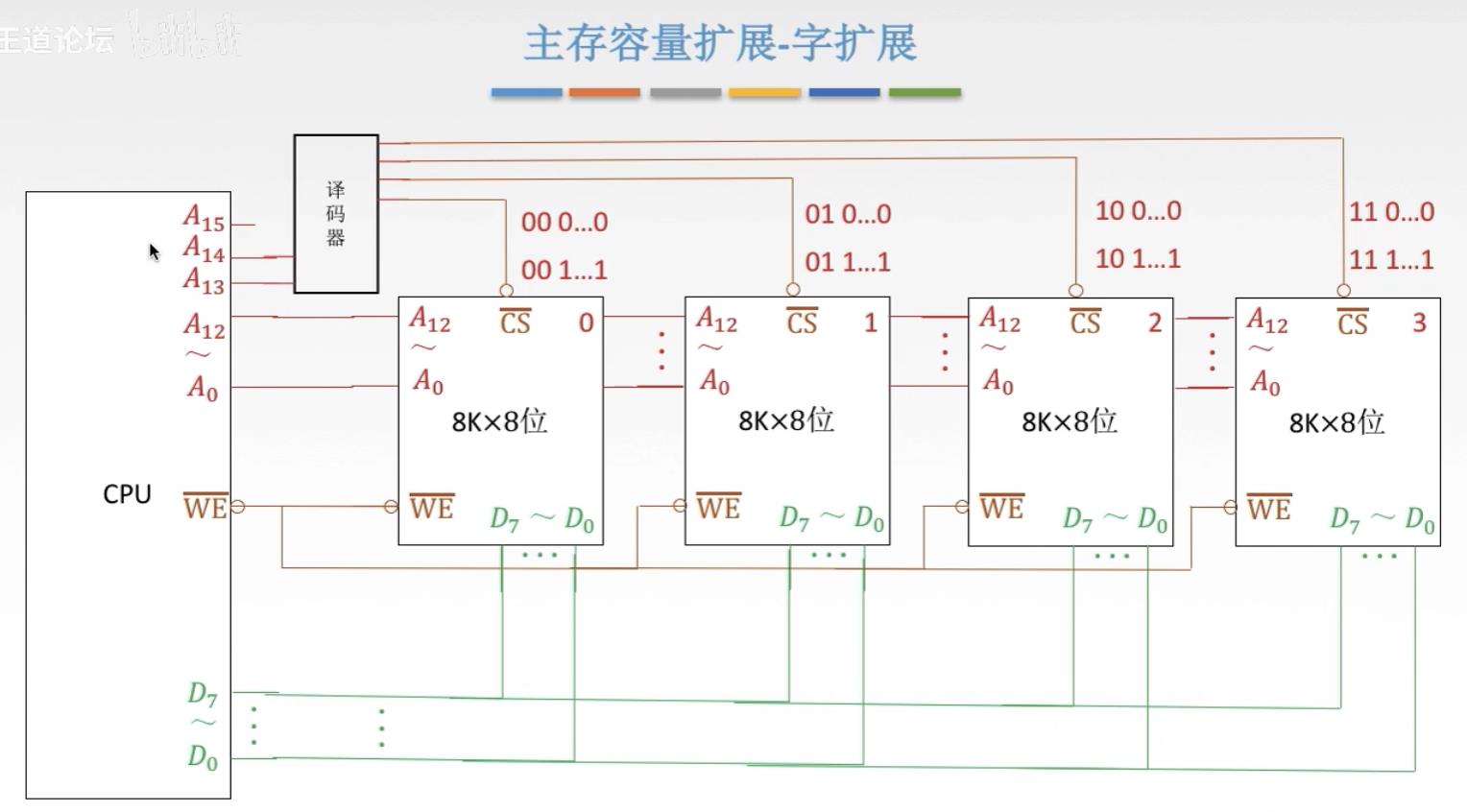

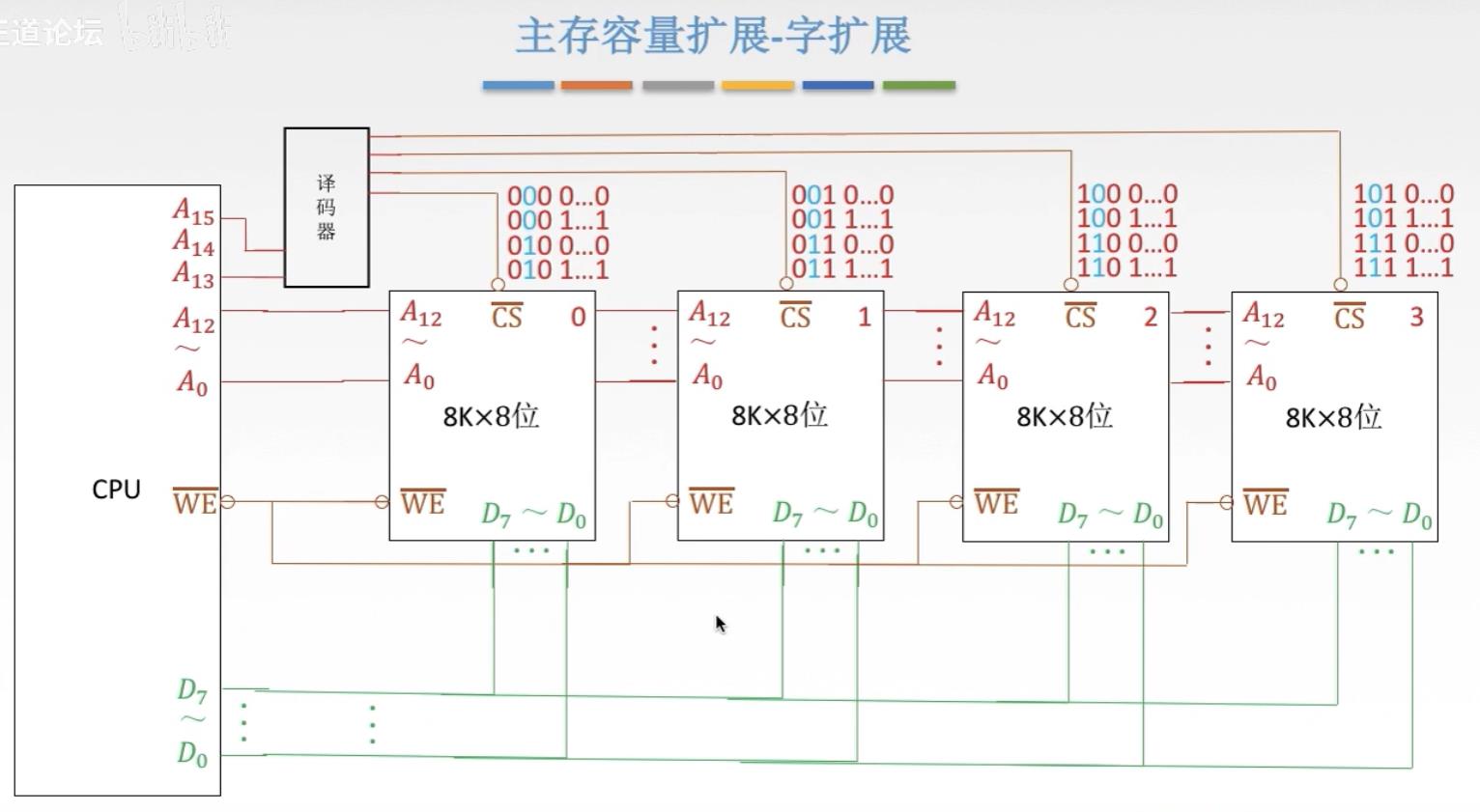

2.字扩展

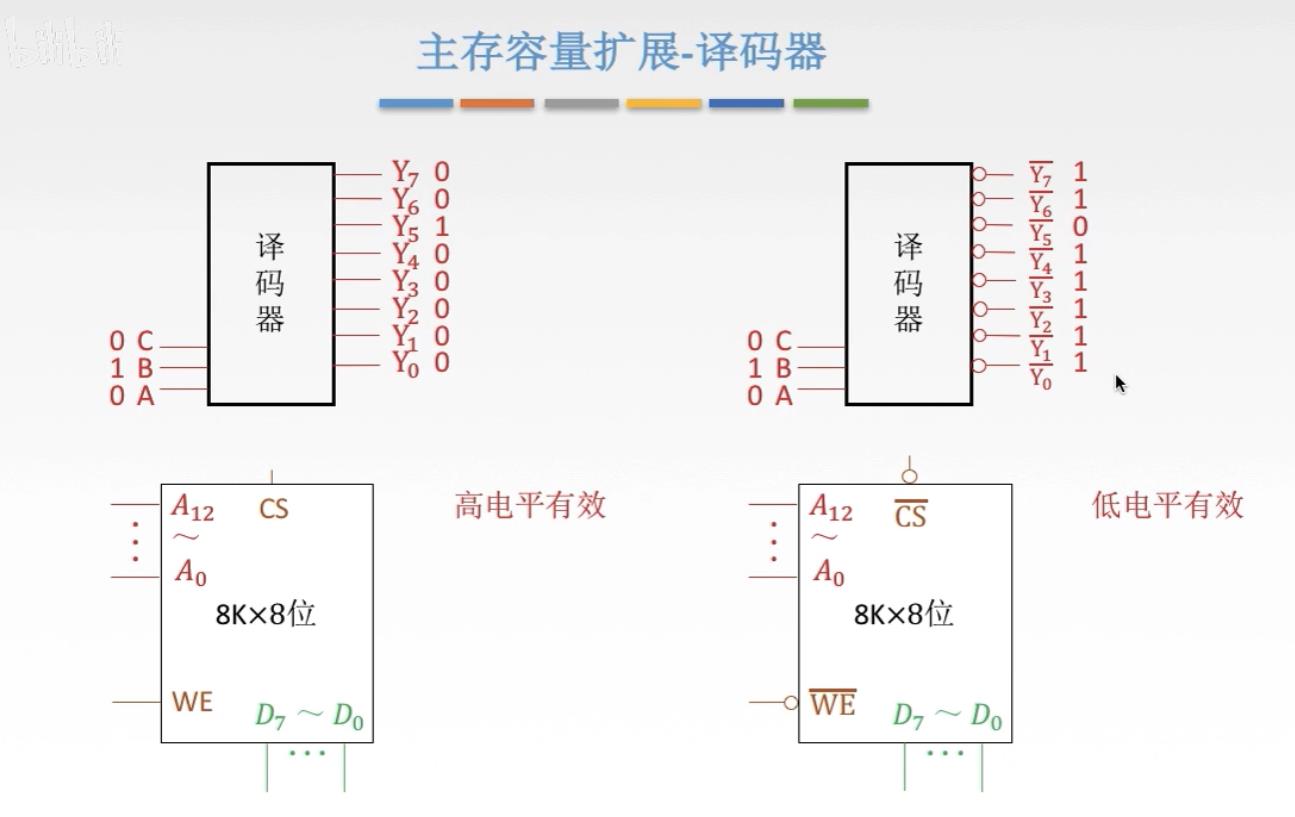

原来译码器的功能在这里可以使用!

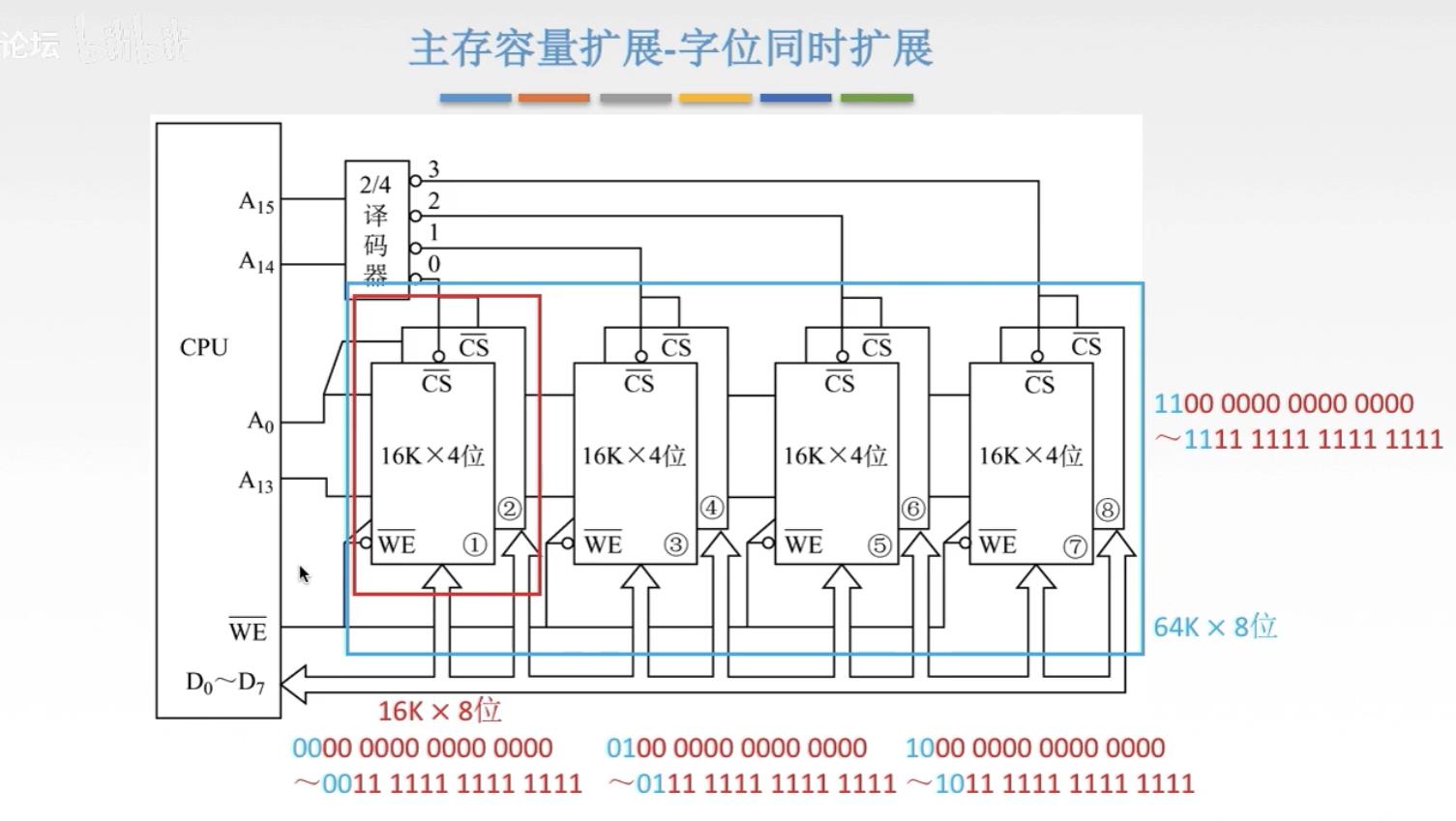

3.字位同时扩展法

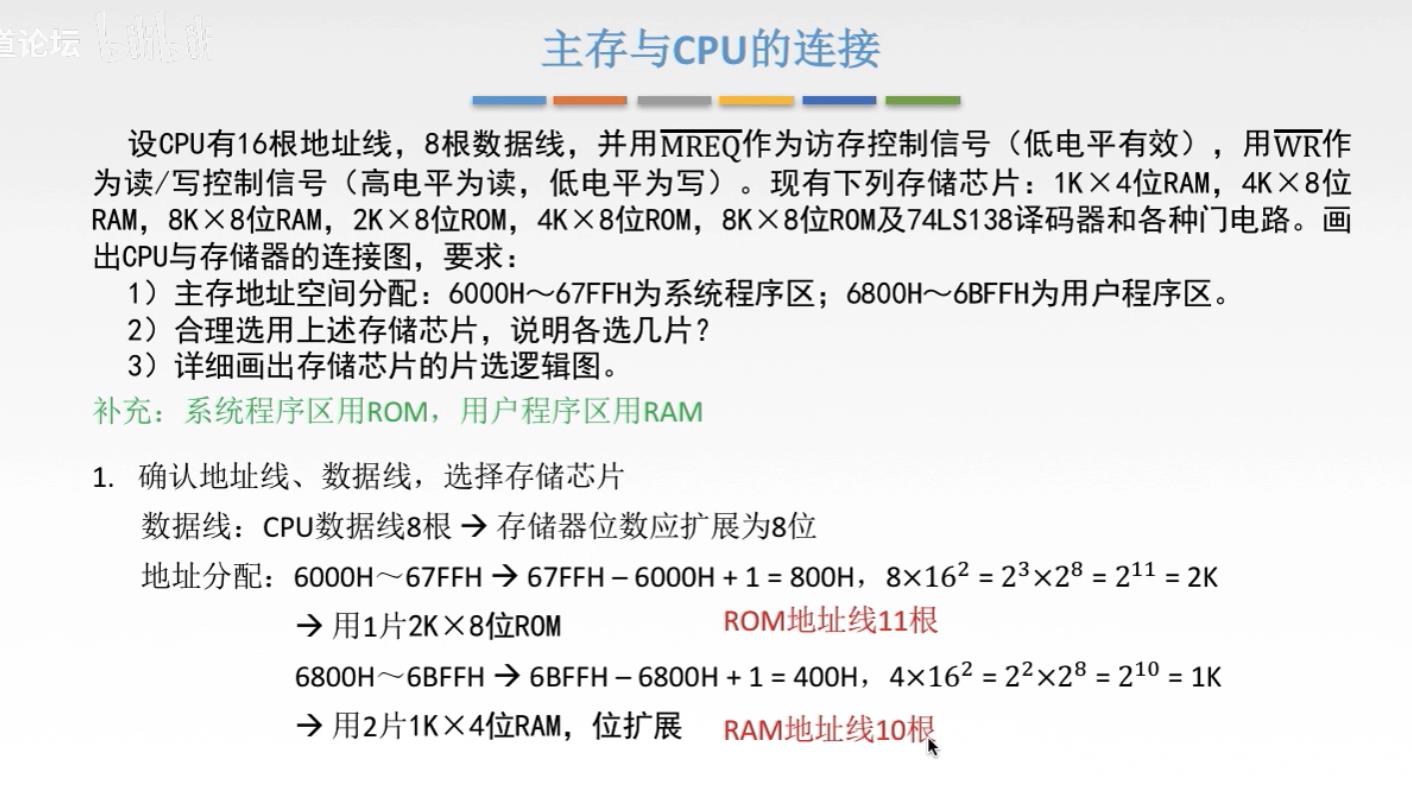

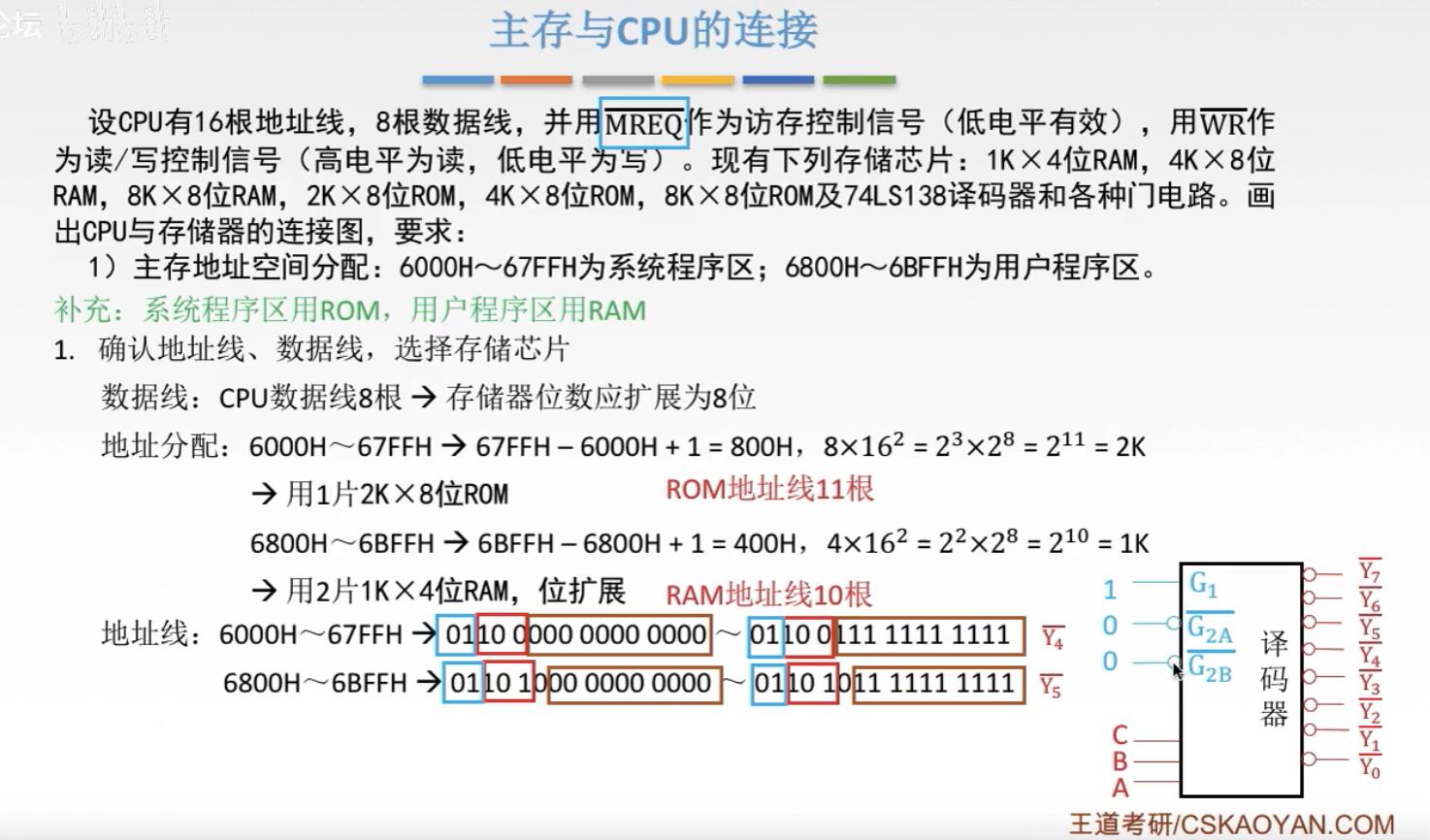

设CPU有16根地址线,8根数据线,并用MREQ作为访存控制信号(低电平有效),用WR作为读/写控制信号(高电平为读,低电平为写)。现有下列存储芯片:1K×4位RAM,4K×8位RAM,8K×8位RAM,2K×8位ROM,4K×8位ROM,8K×8位ROM及74LS138译码器和各种门电路。画出CPU与存储器的连接图,要求:

1)主存地址空间分配:6000H~67FFH为系统程序区;6800H~6BFFH为用户程序区。

2)合理选用上述存储芯片,说明各选几片?

3)详细画出存储芯片的片选逻辑图。

补充:系统程序区用ROM,用户程序区用RAM

MAR和MDR是直接做在CPU芯片上面的!

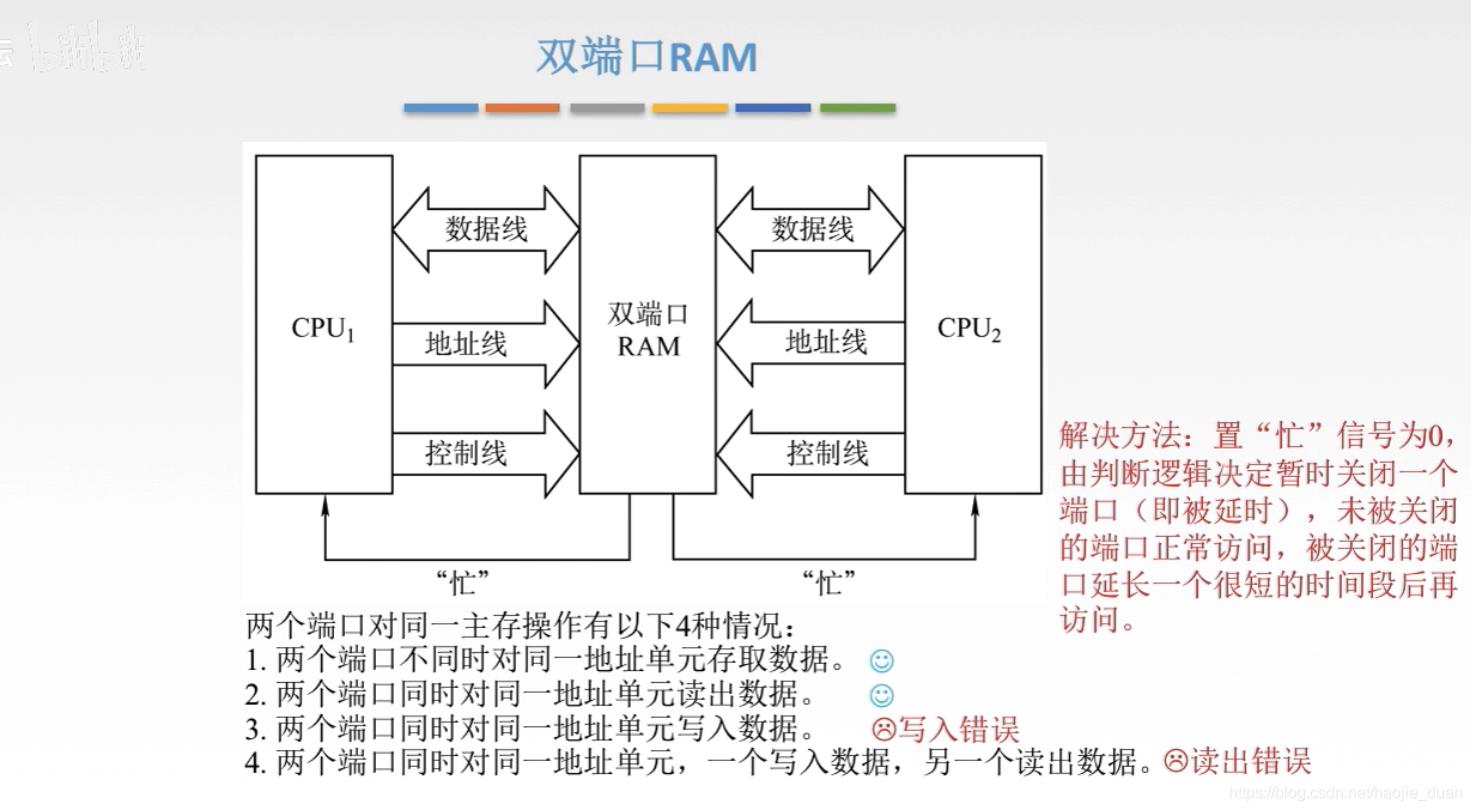

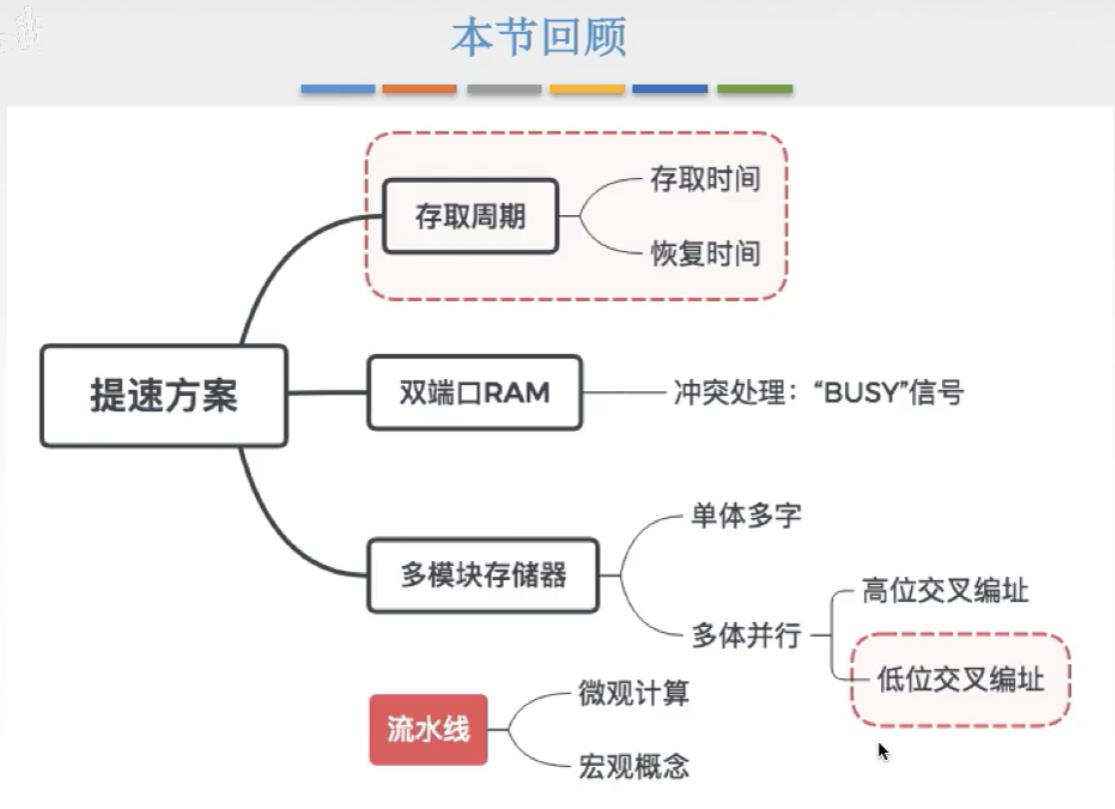

3.5 双端口RAM和多模块存储器

3.5.1 双端口RAM

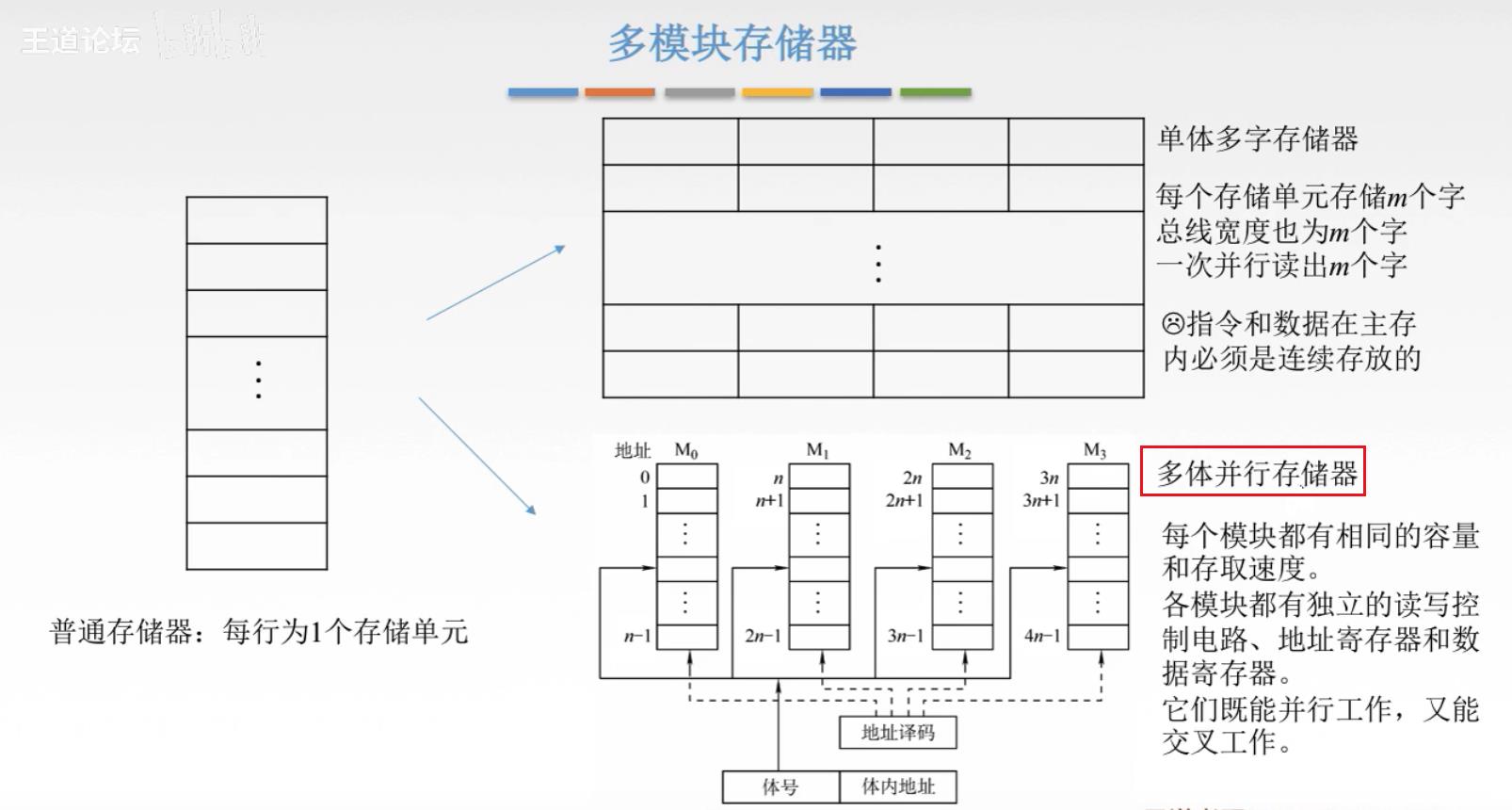

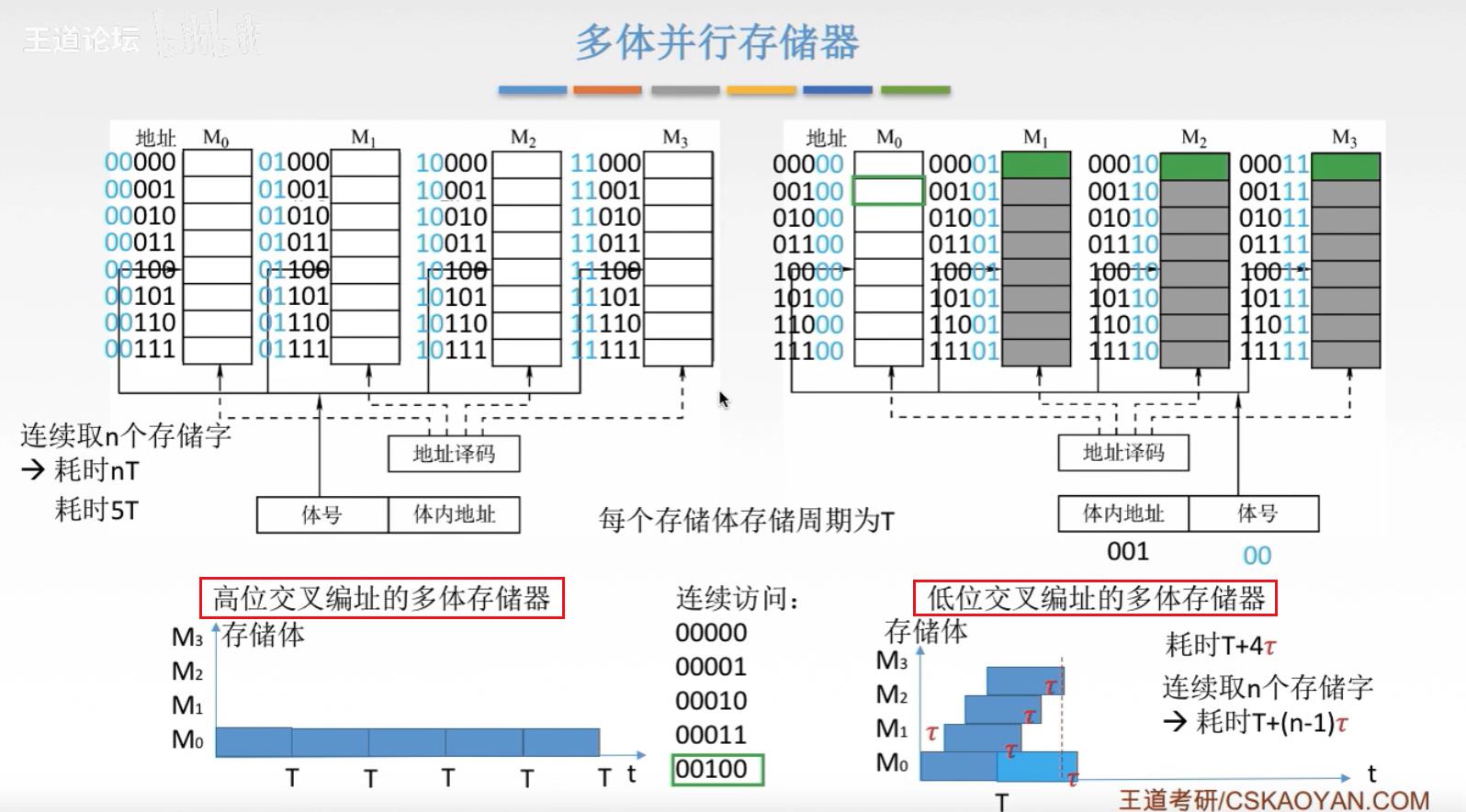

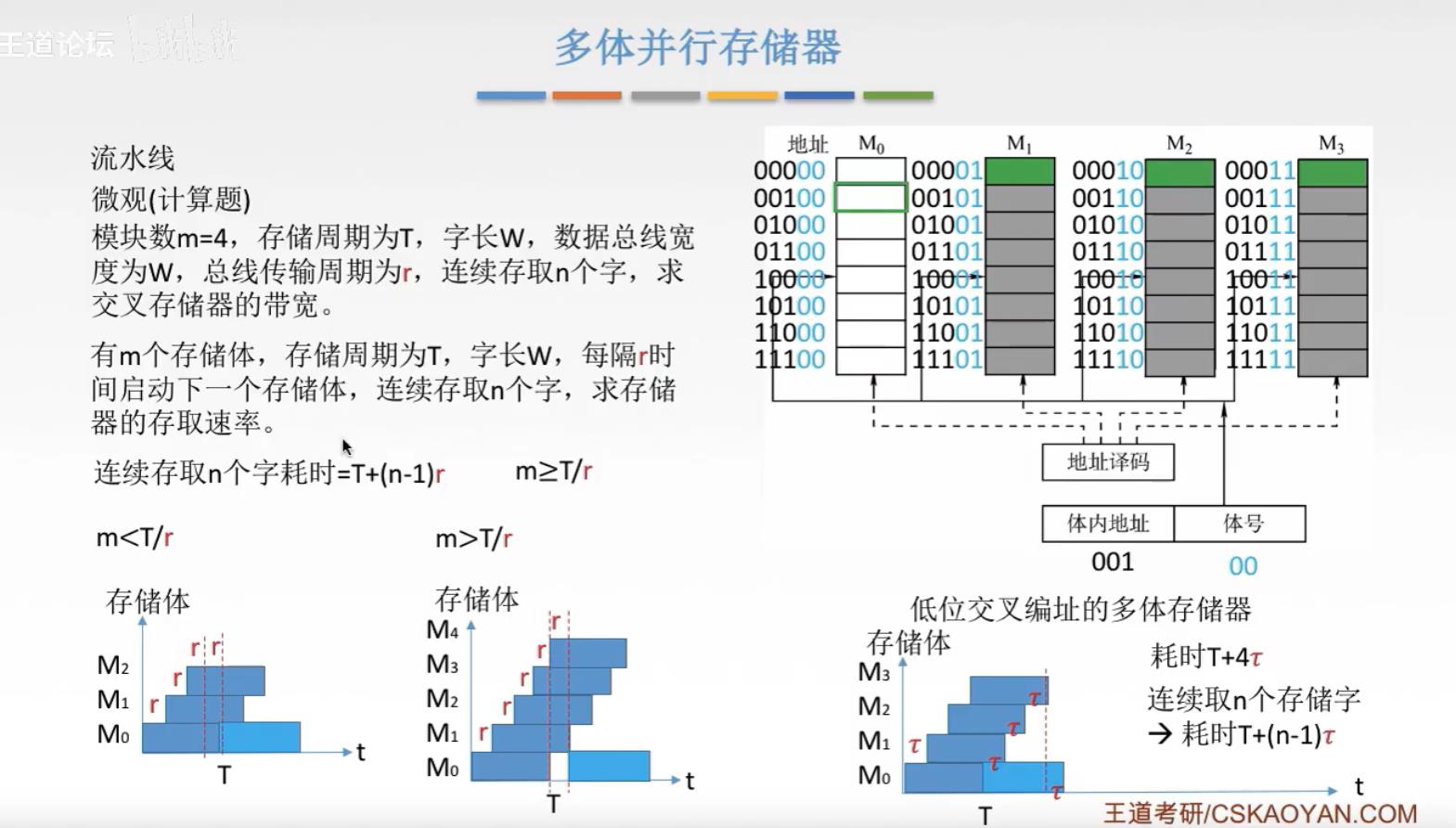

3.5.2 多模块存储器

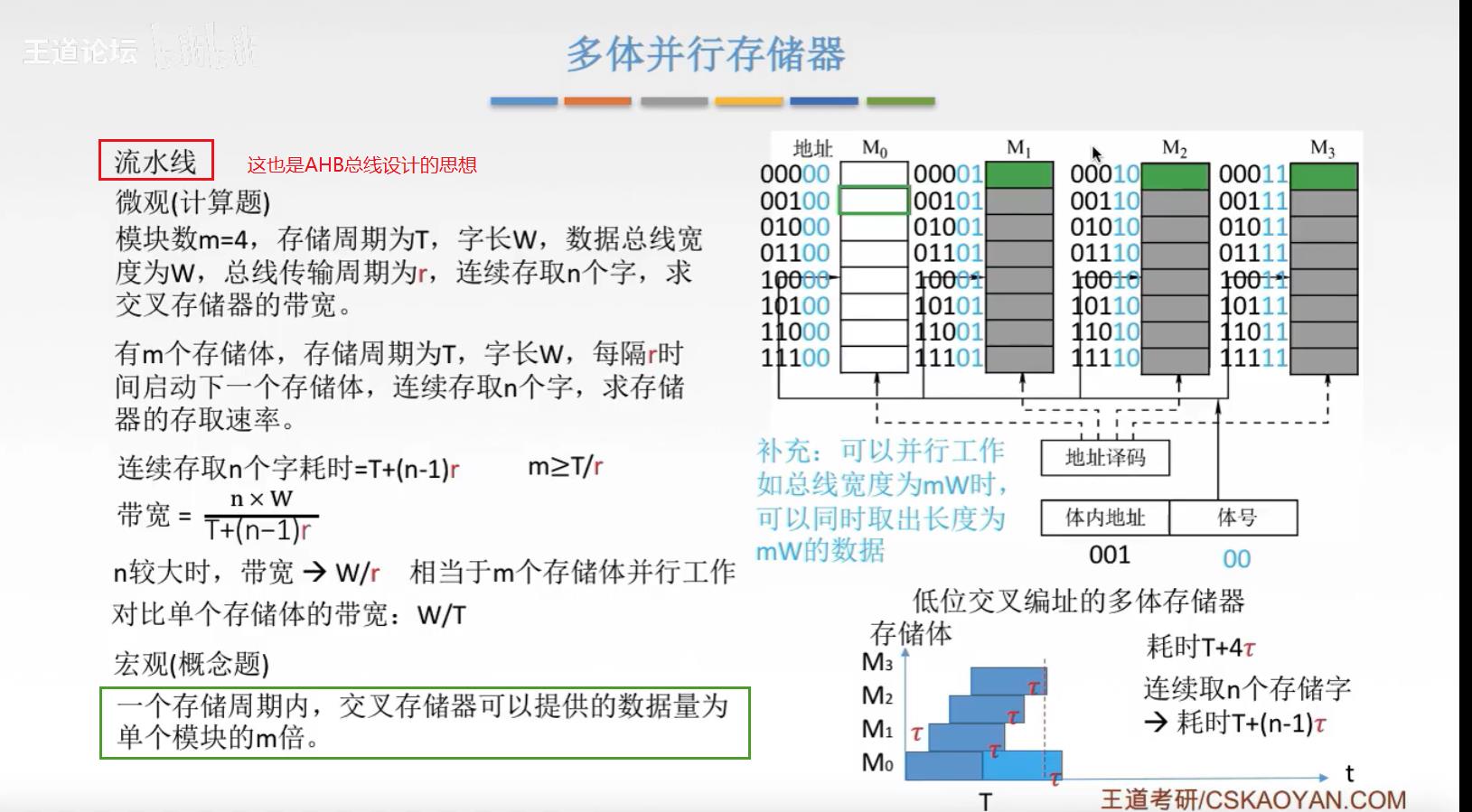

交叉存储器实际上是一种模块式的存储器,它能并行执行多个独立的读/写操作。

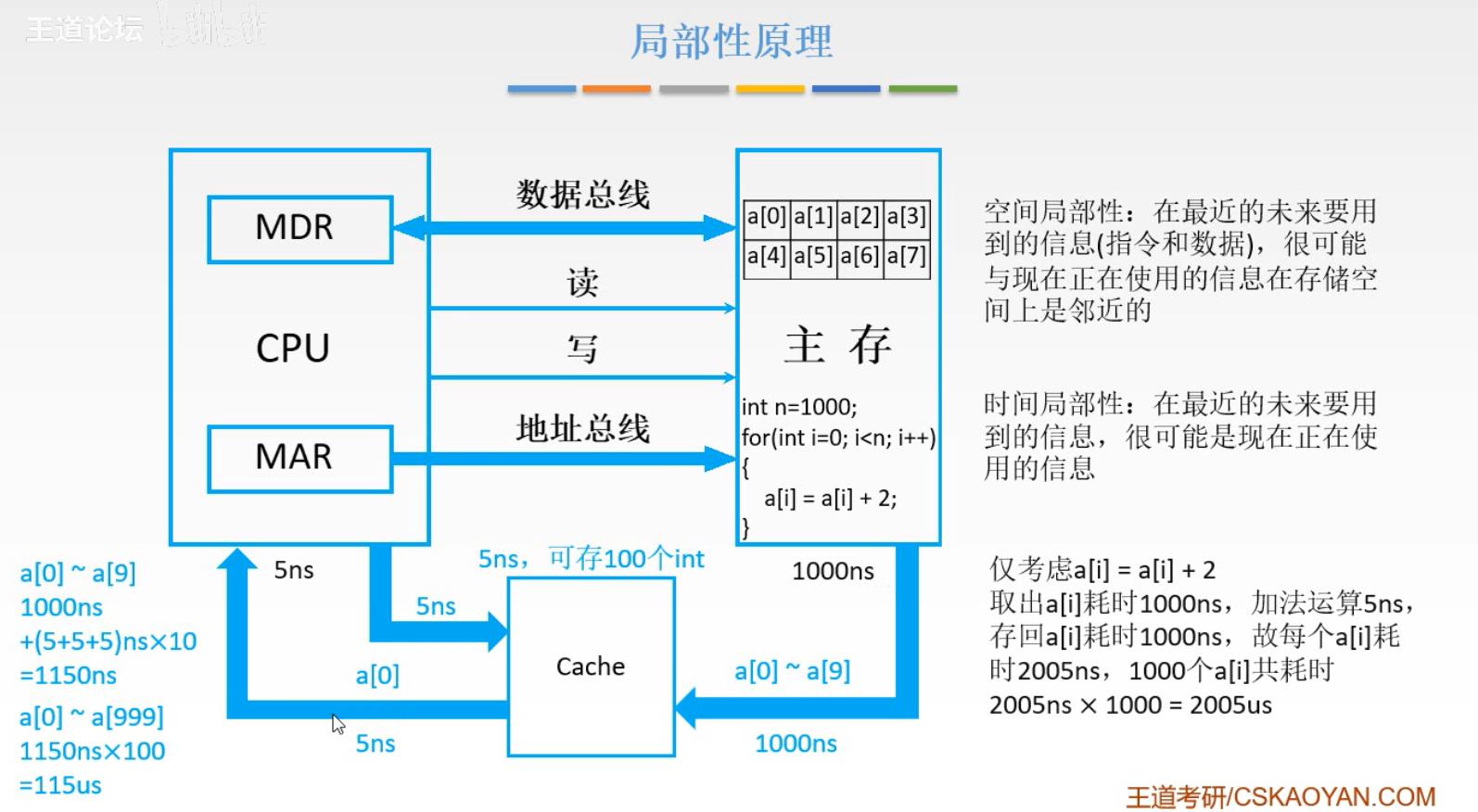

3.6 高速缓冲存储器

3.6.1 程序访问的局部性原理

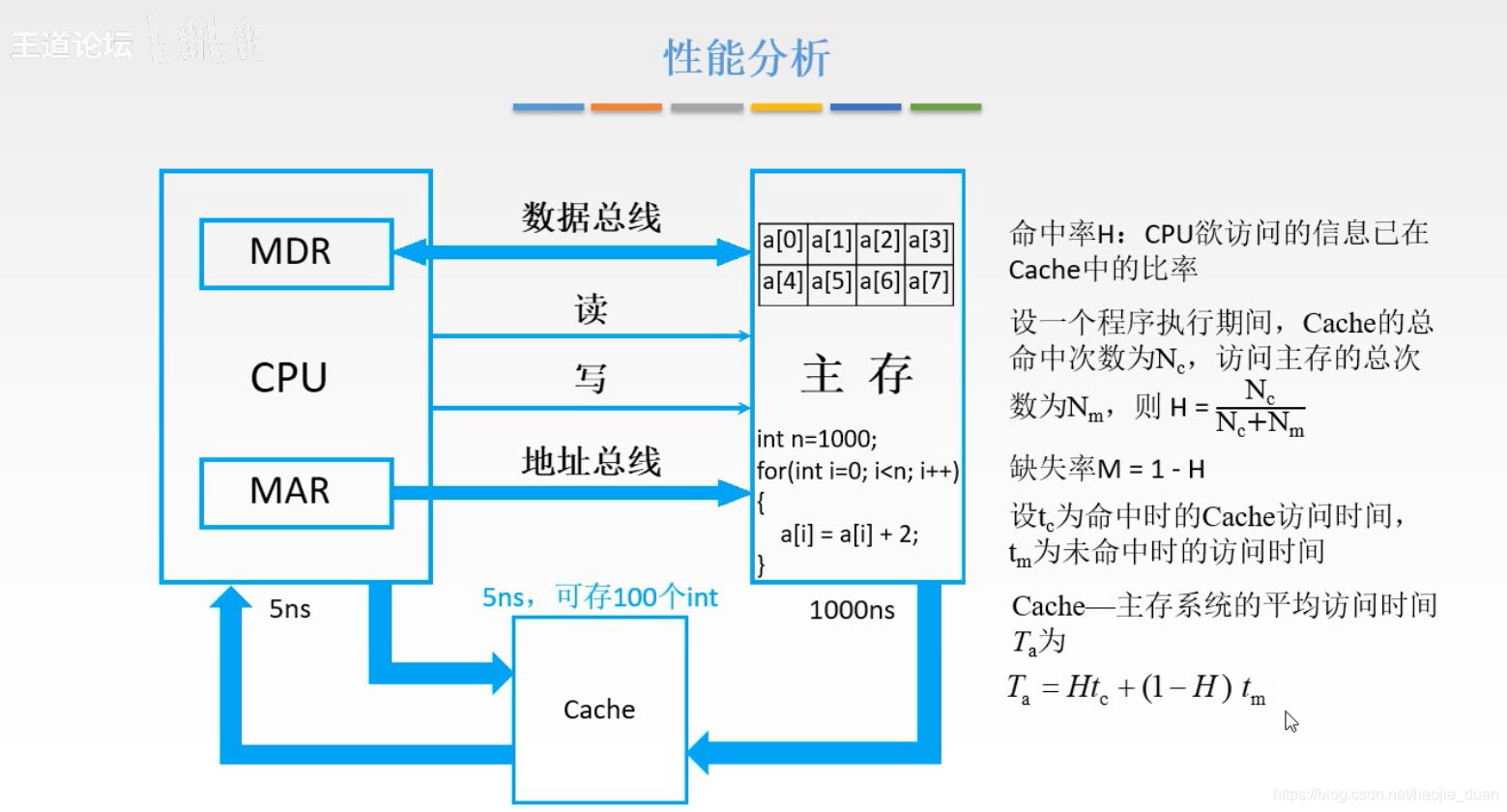

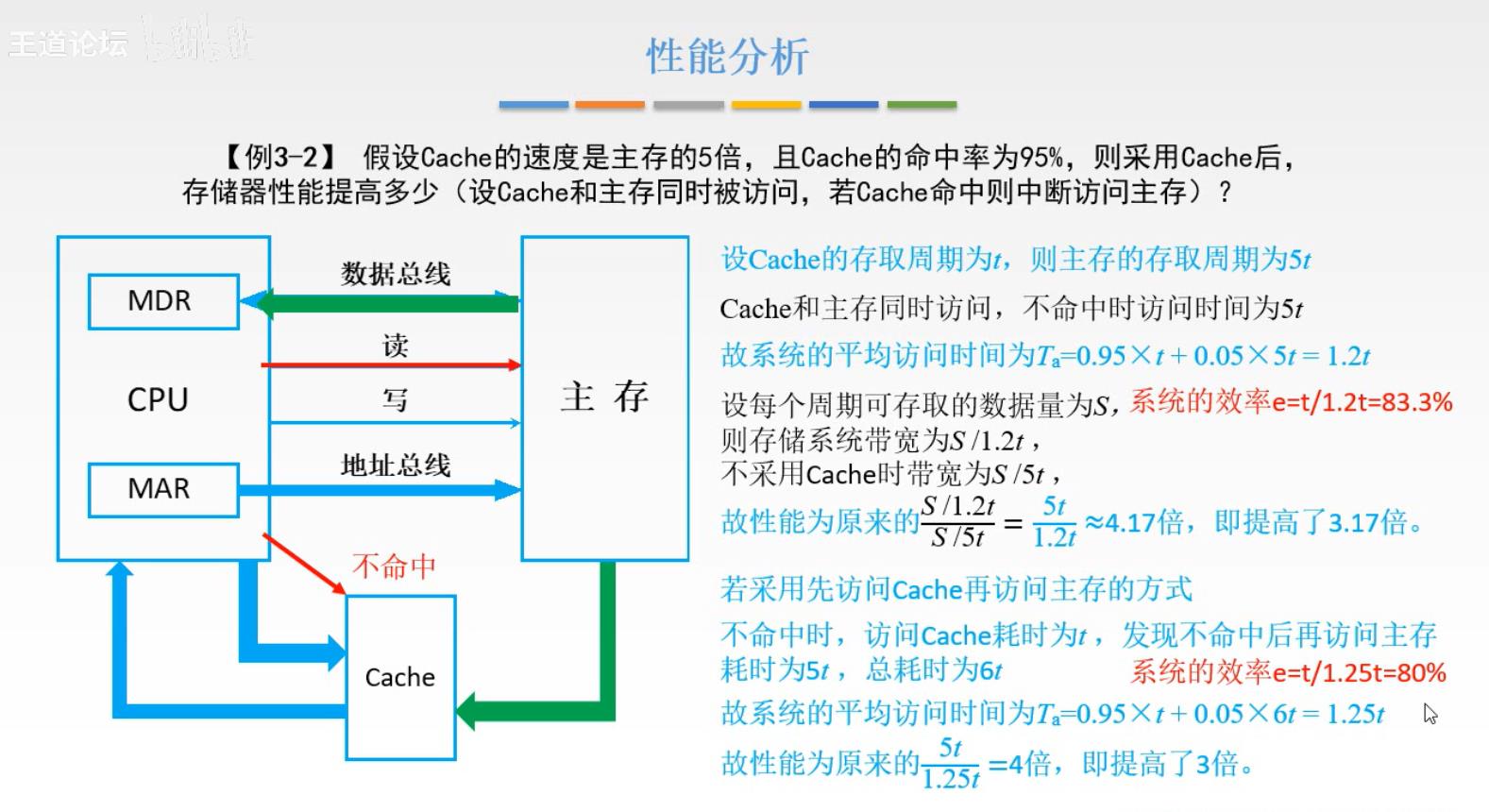

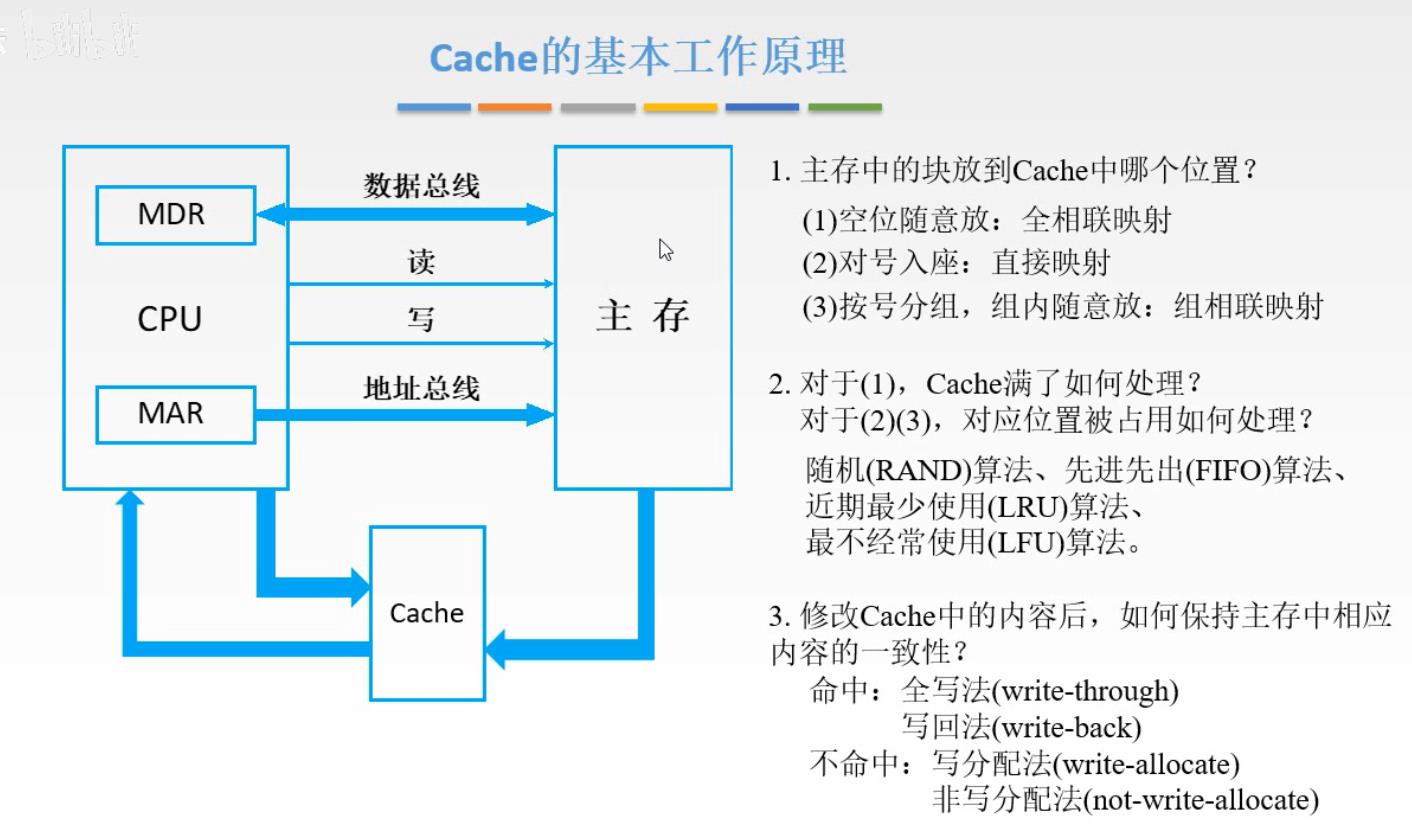

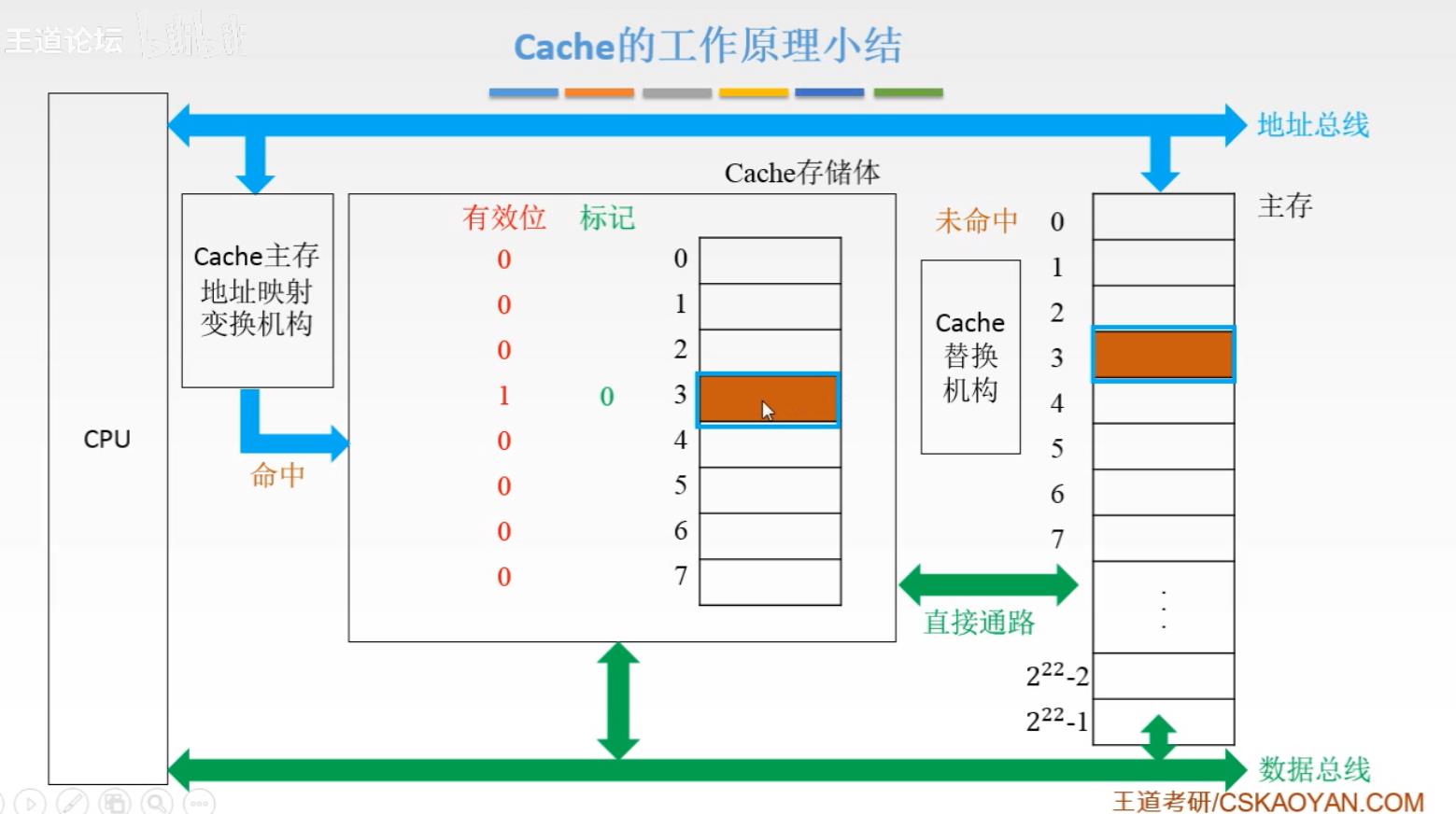

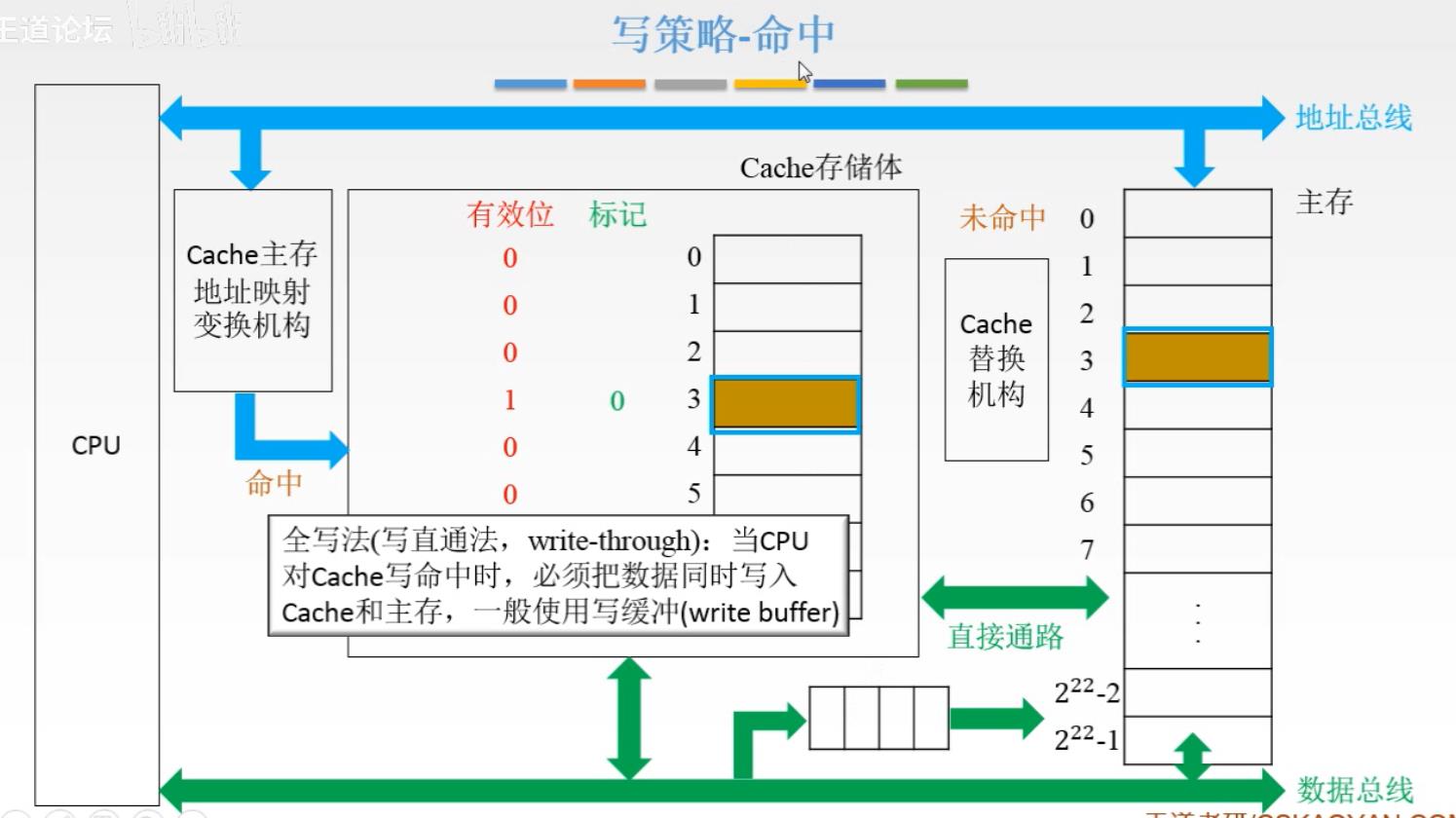

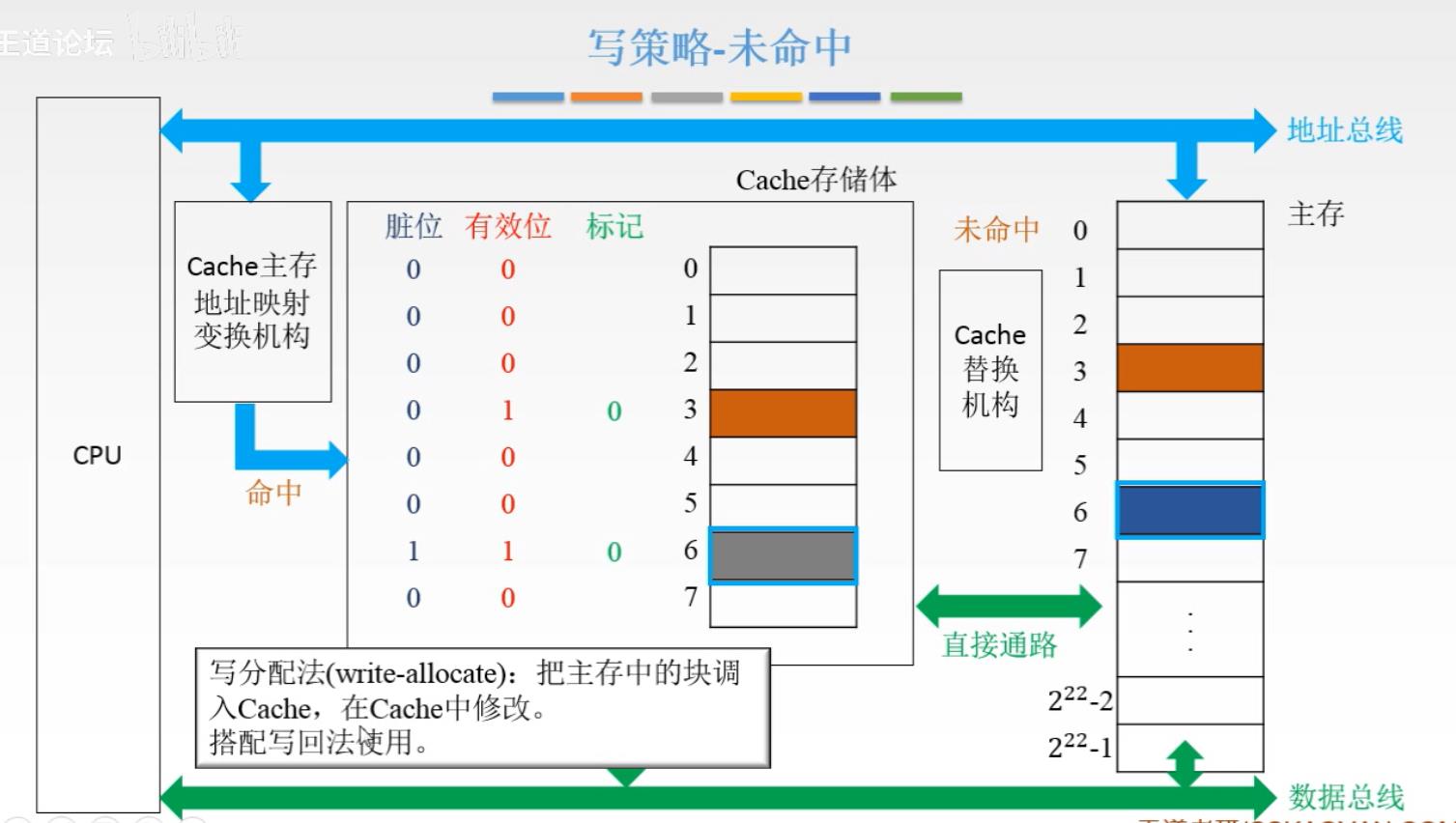

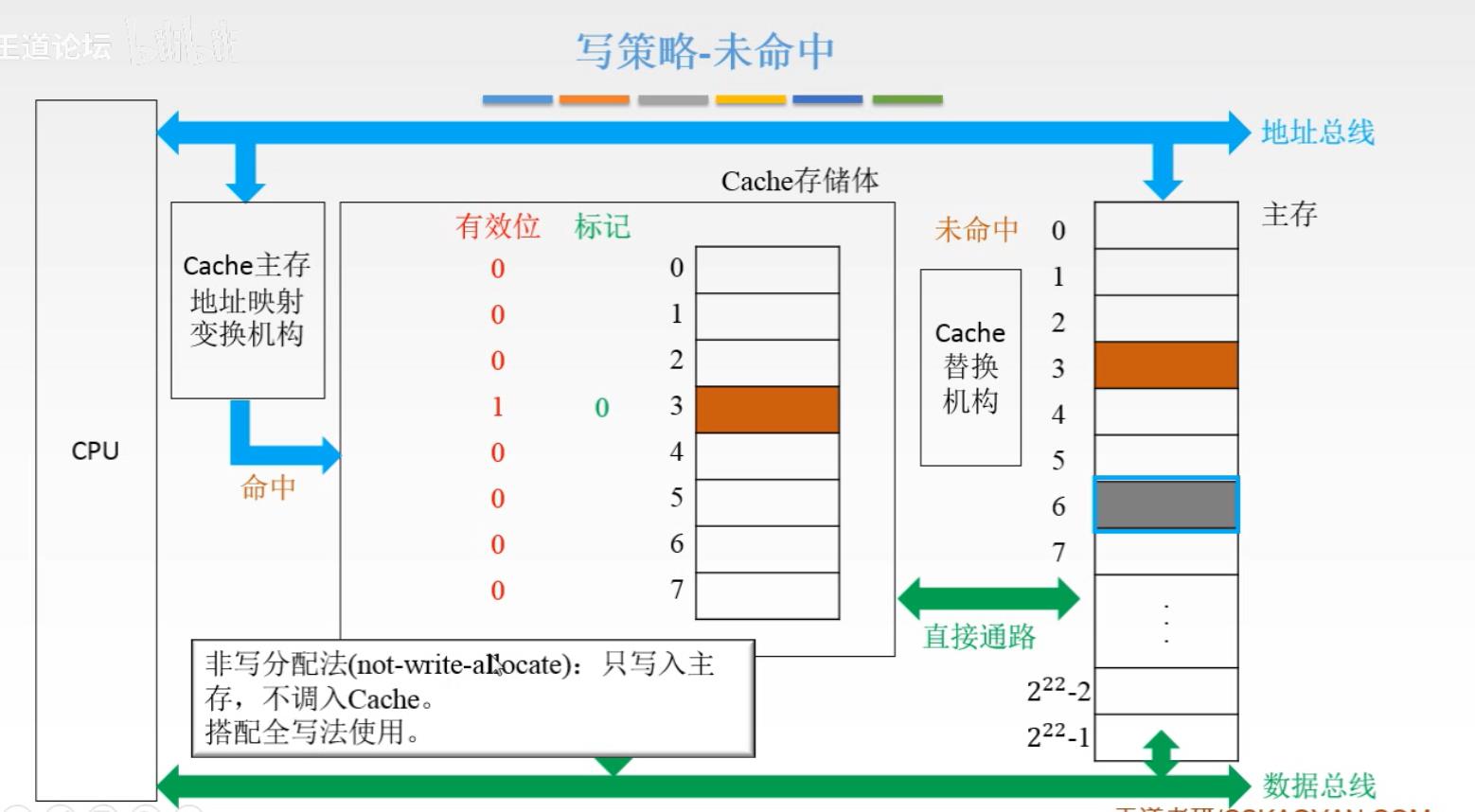

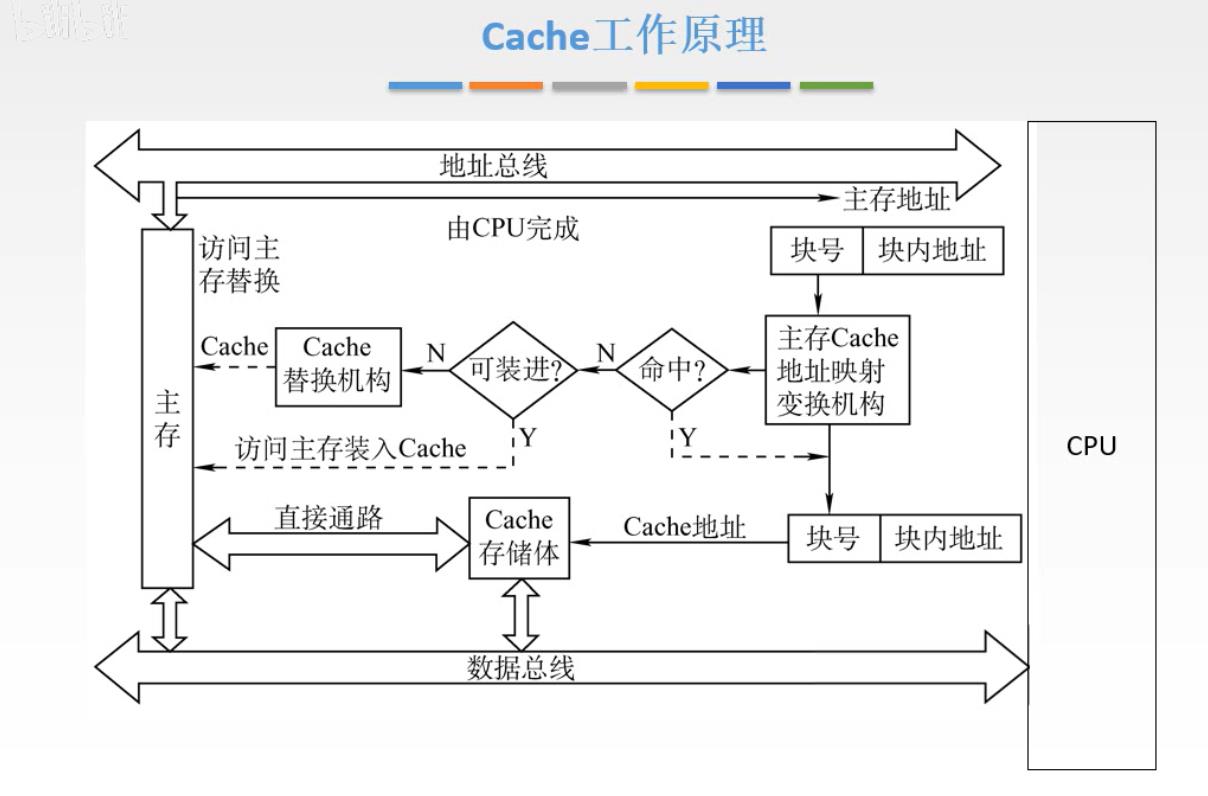

3.6.2 Cache的基本工作原理

直接好家伙!

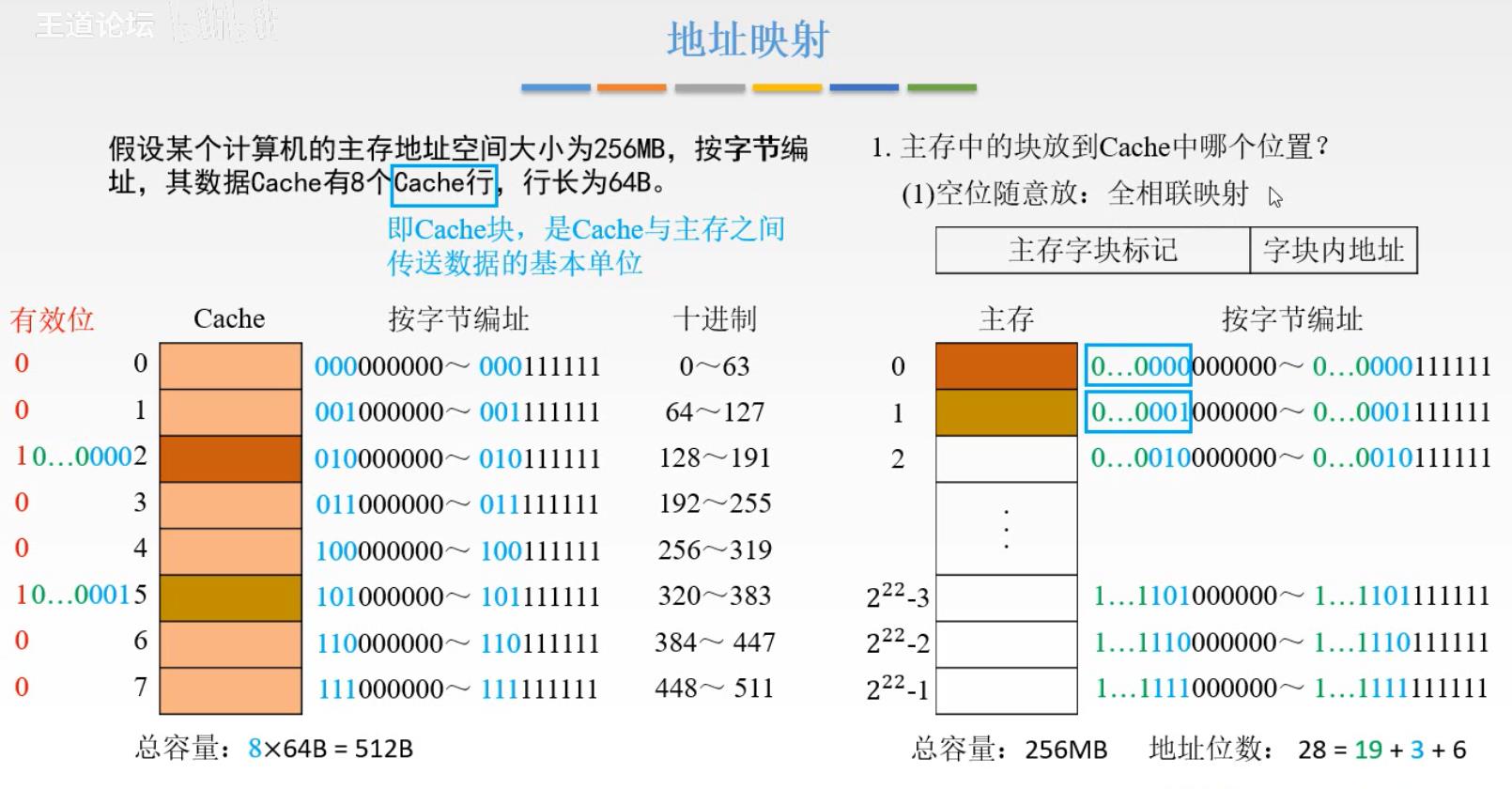

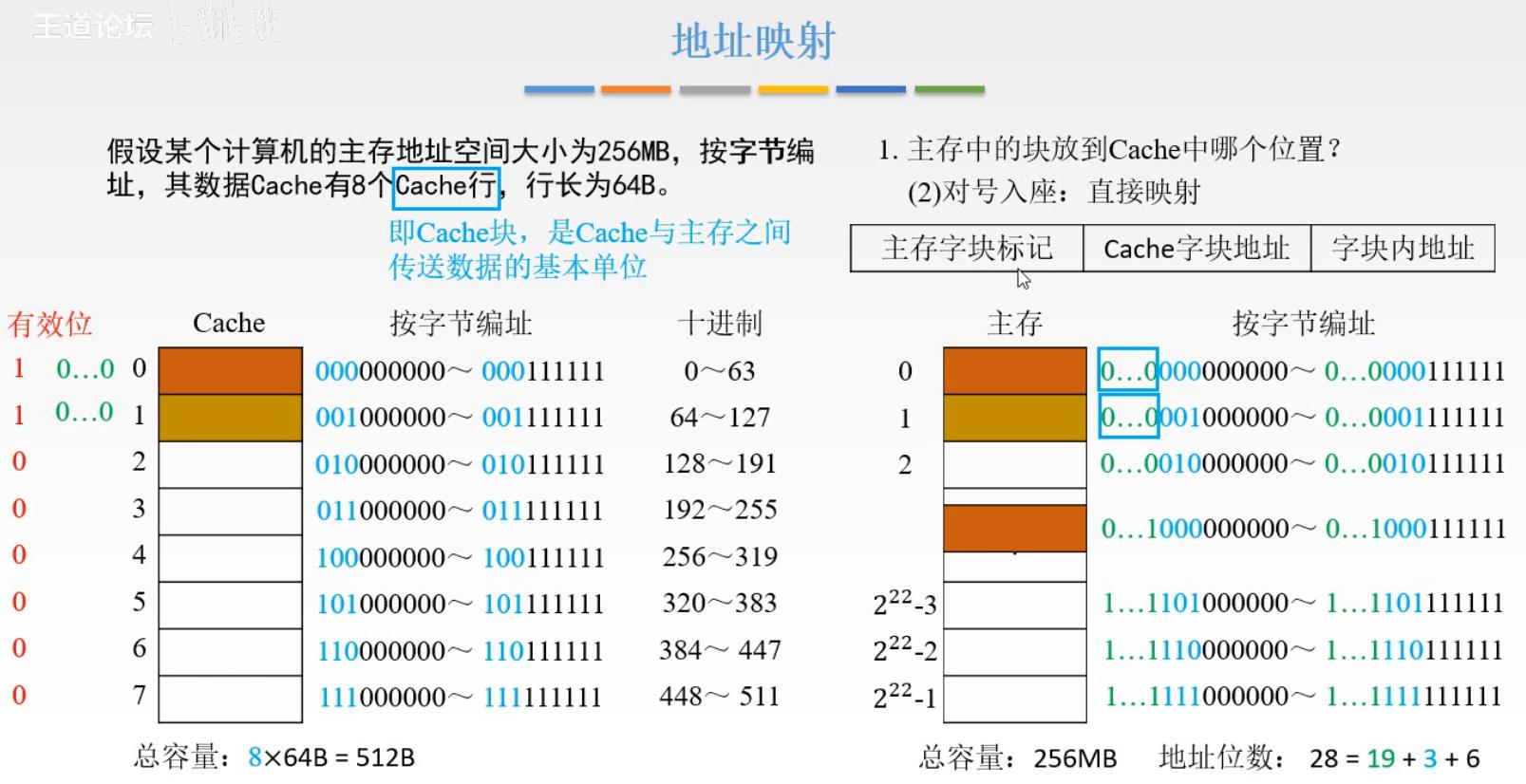

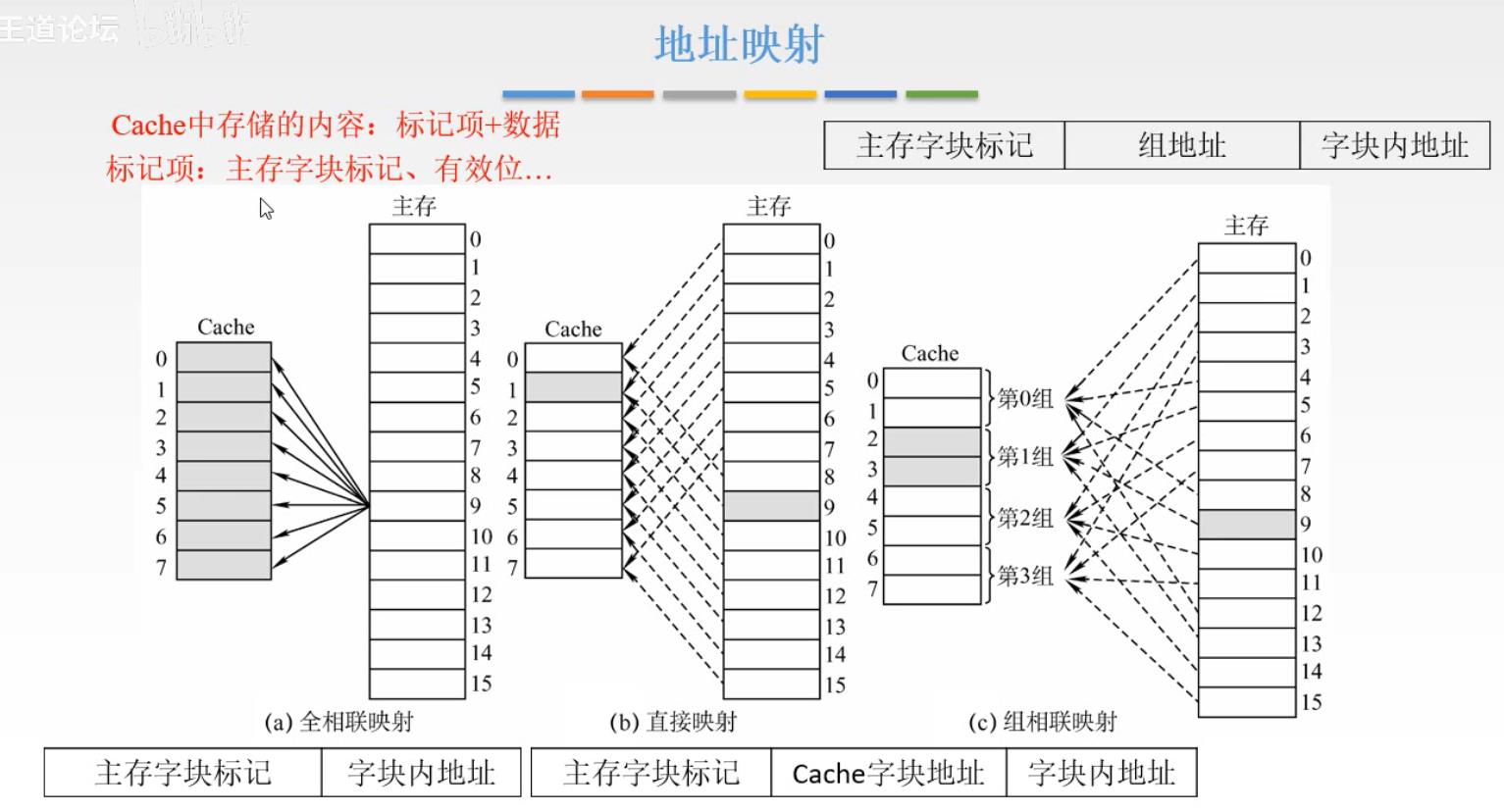

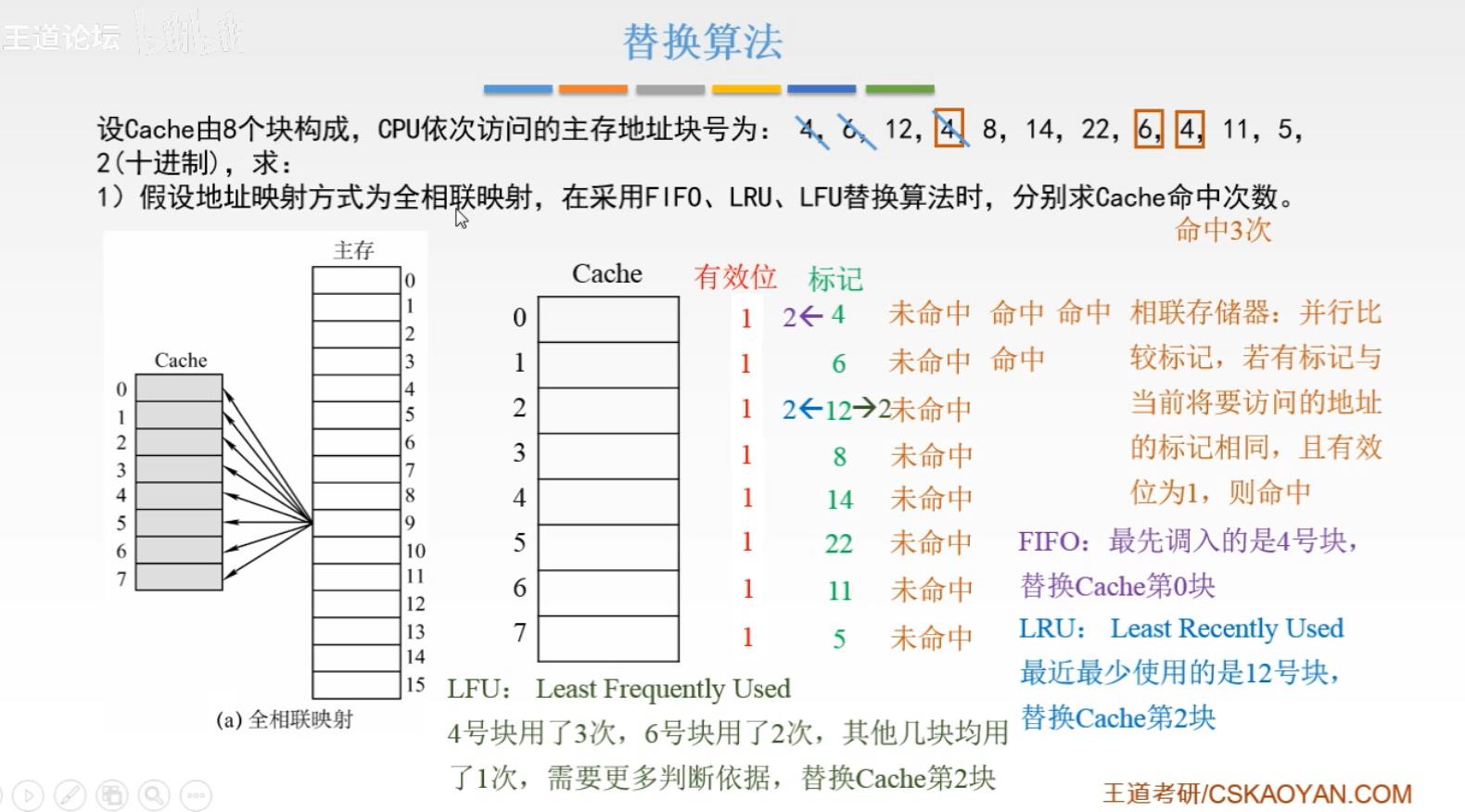

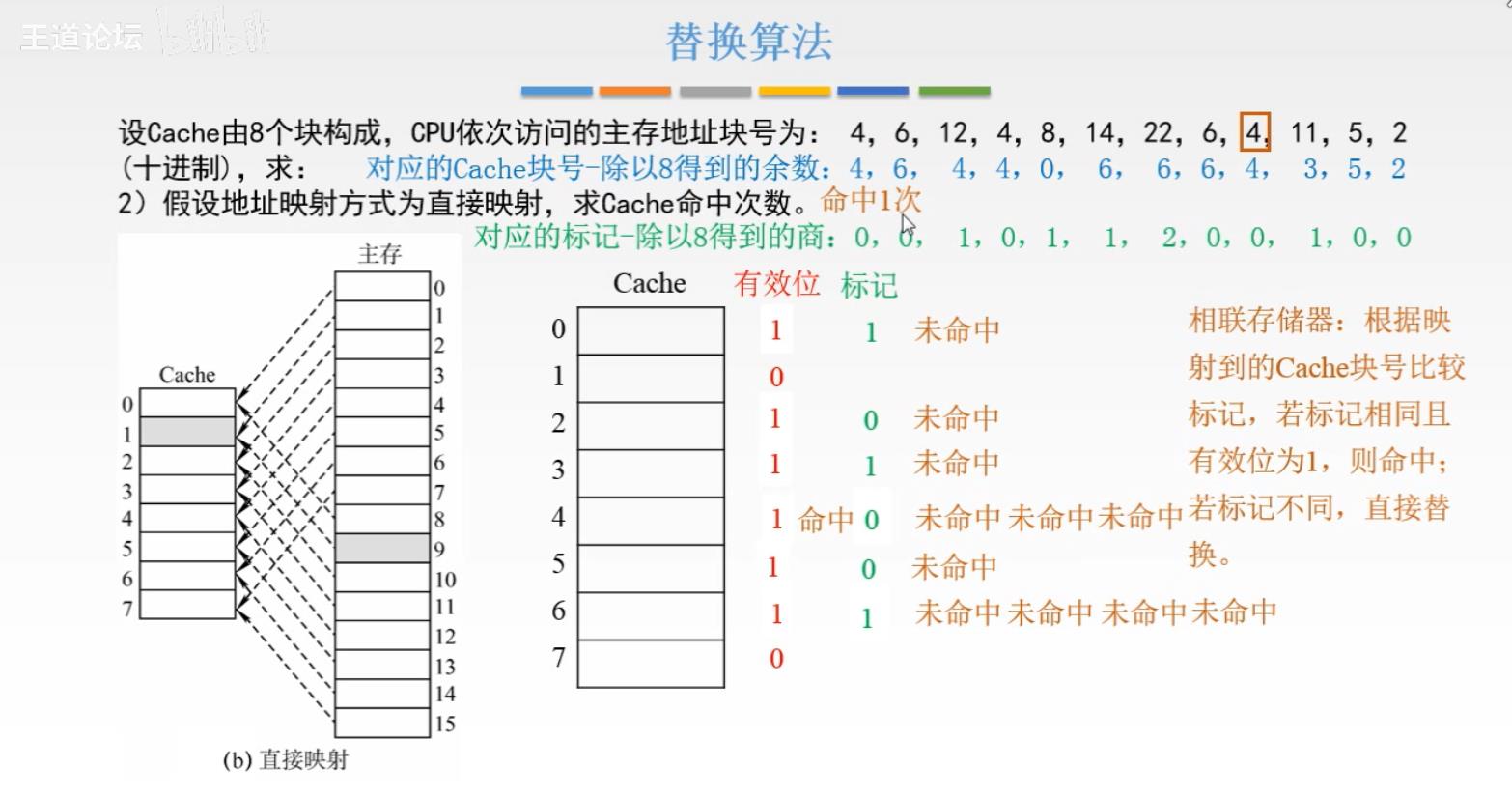

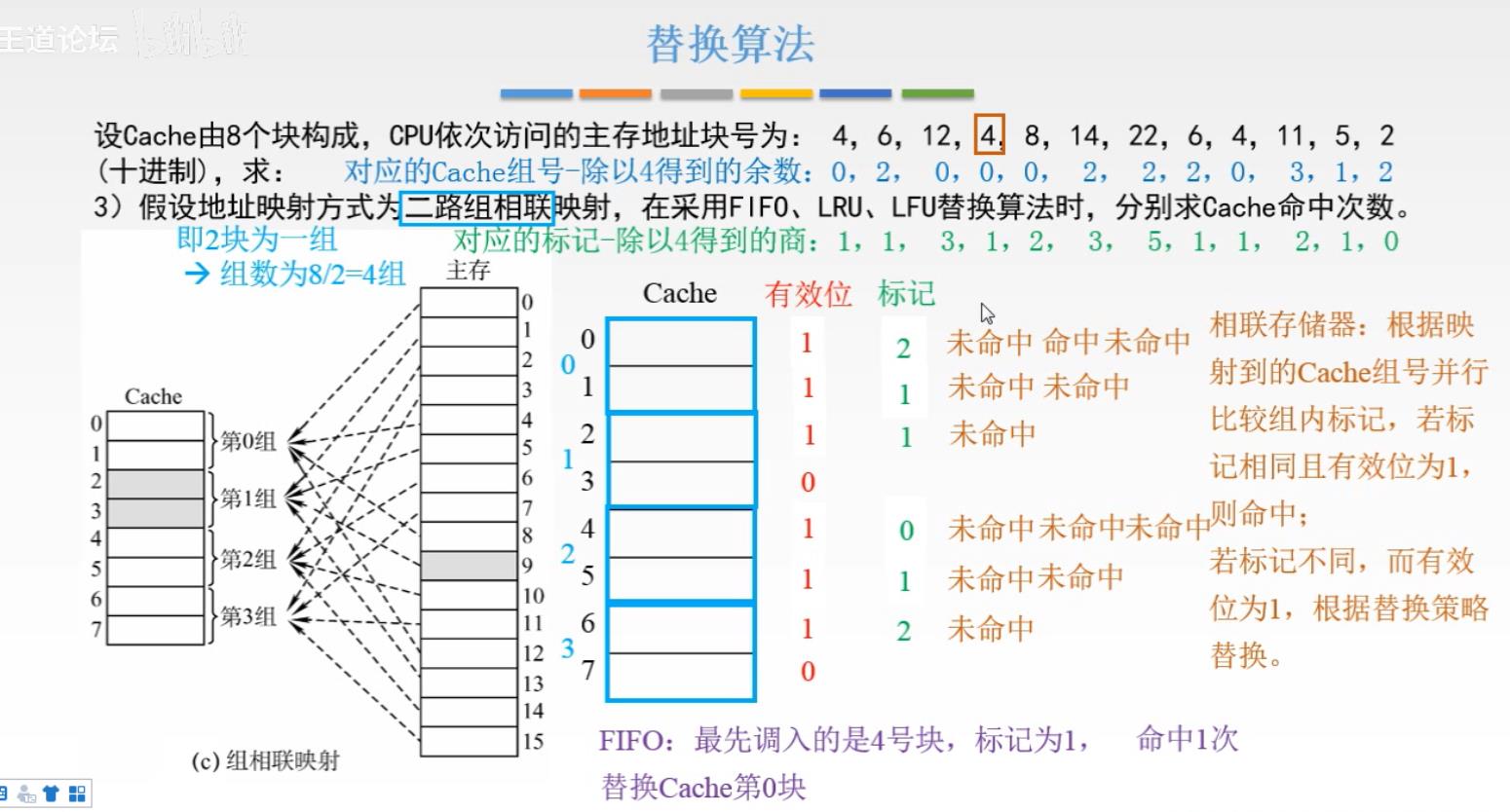

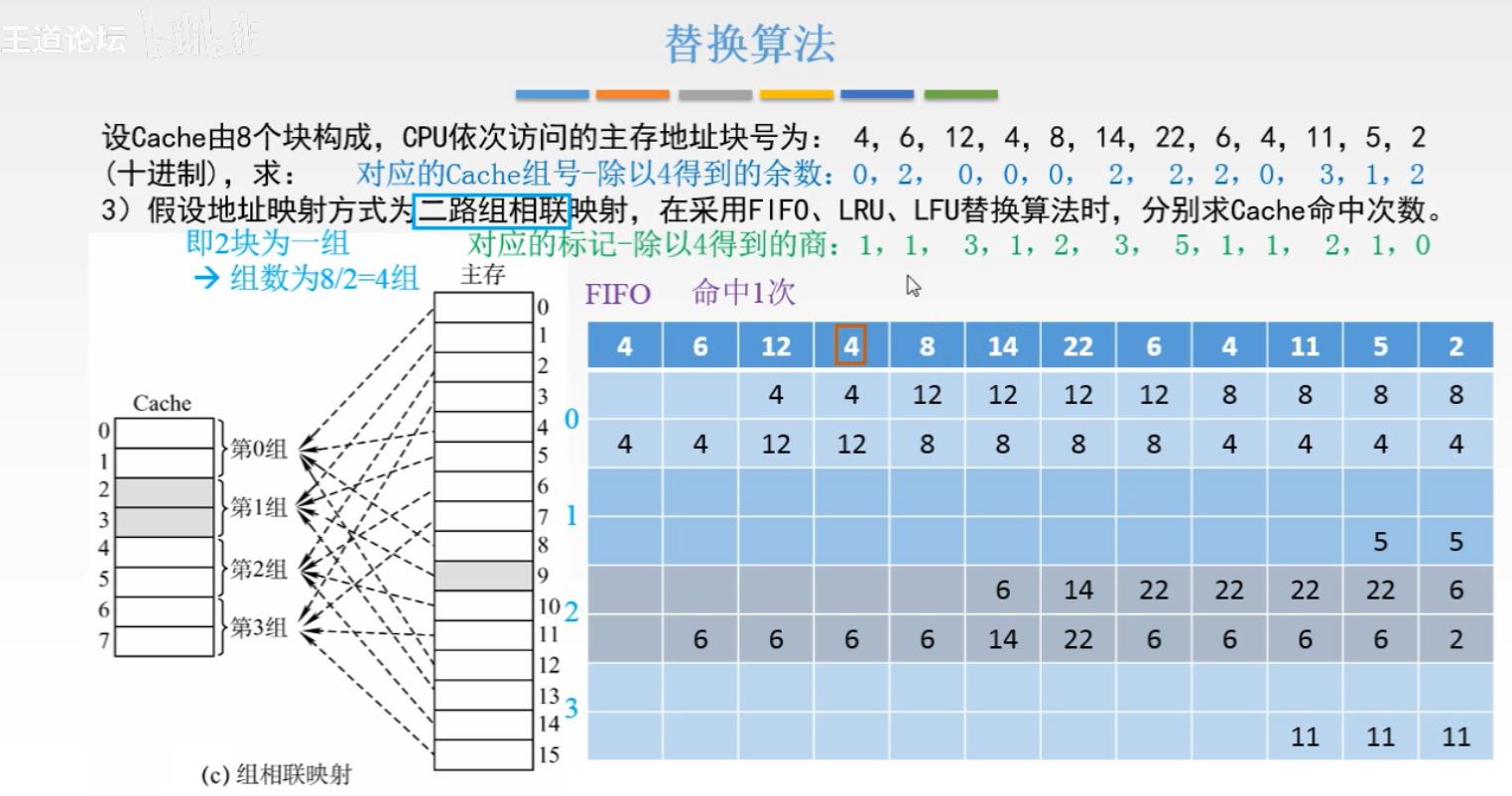

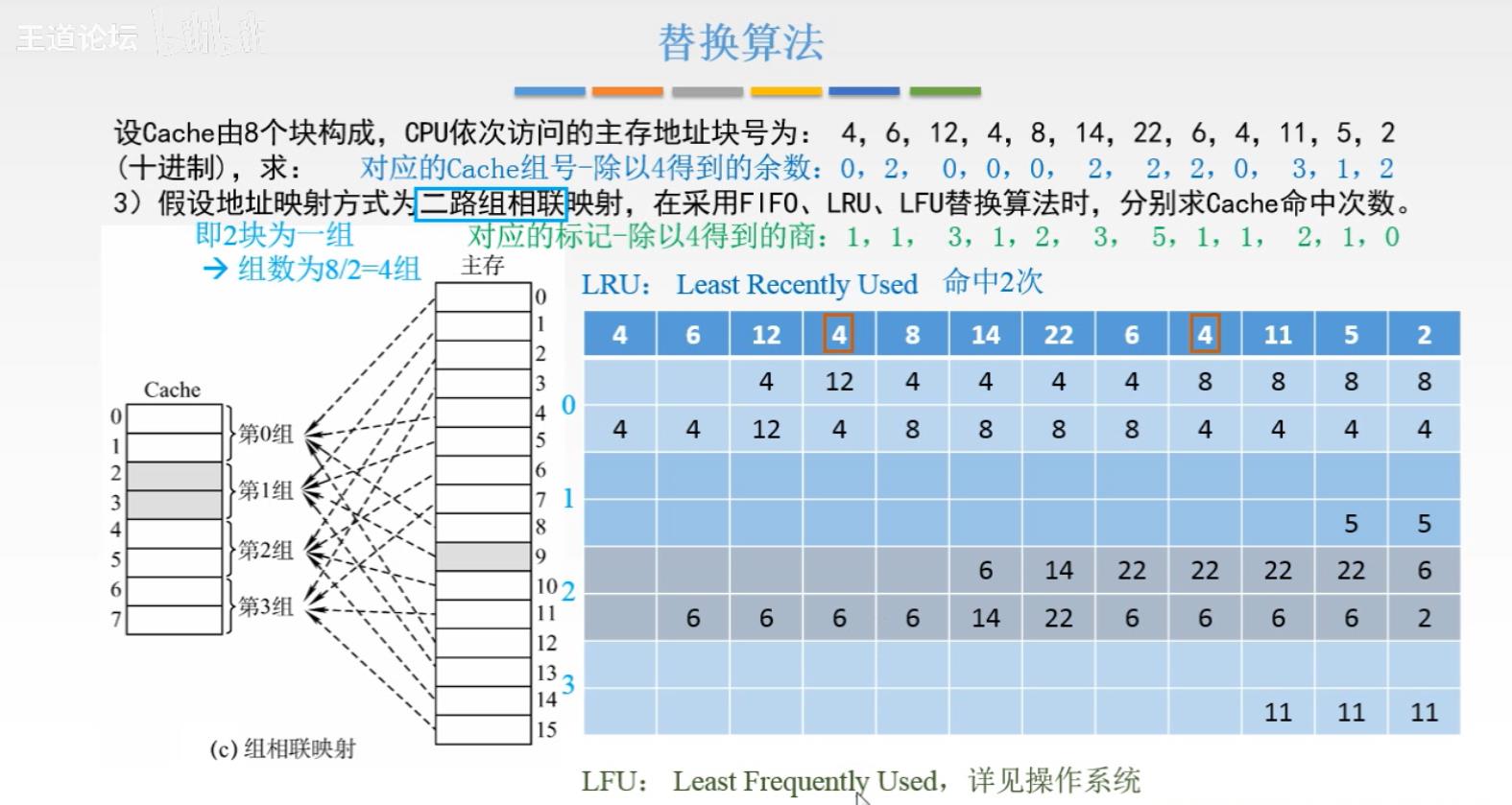

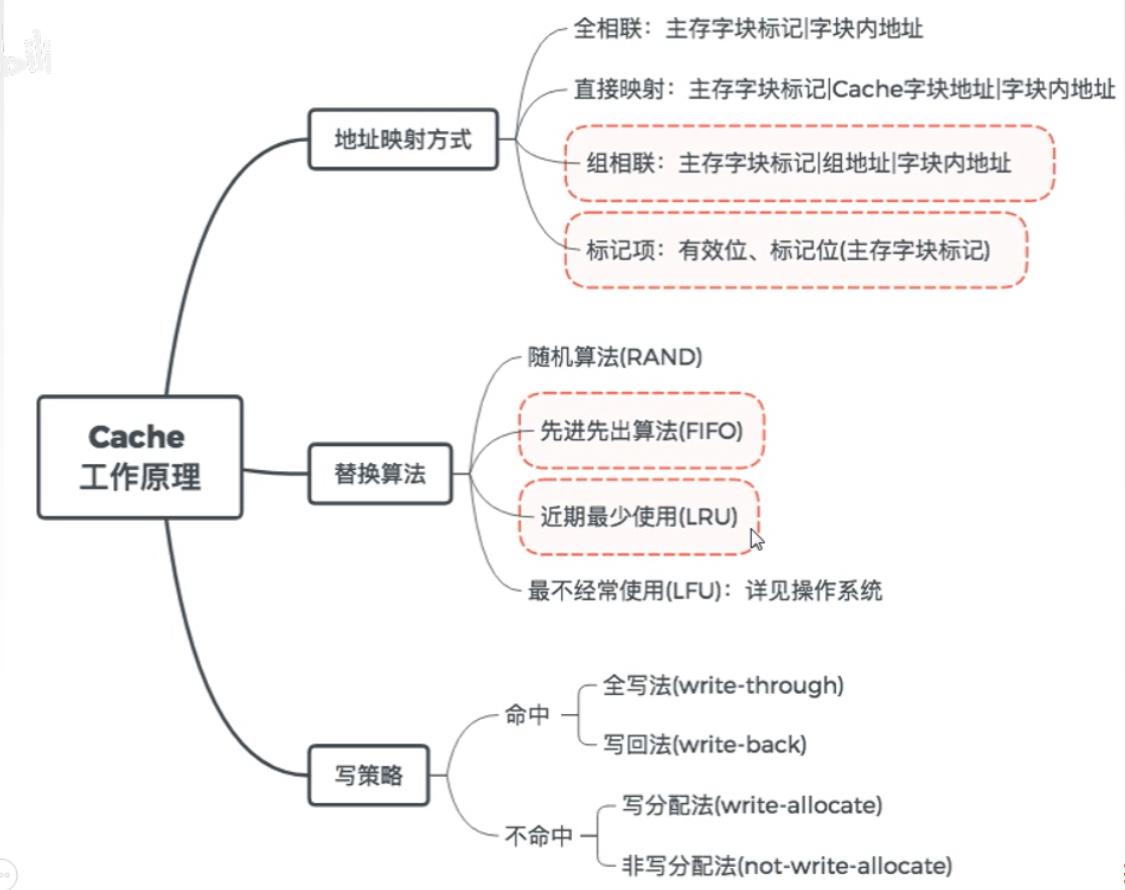

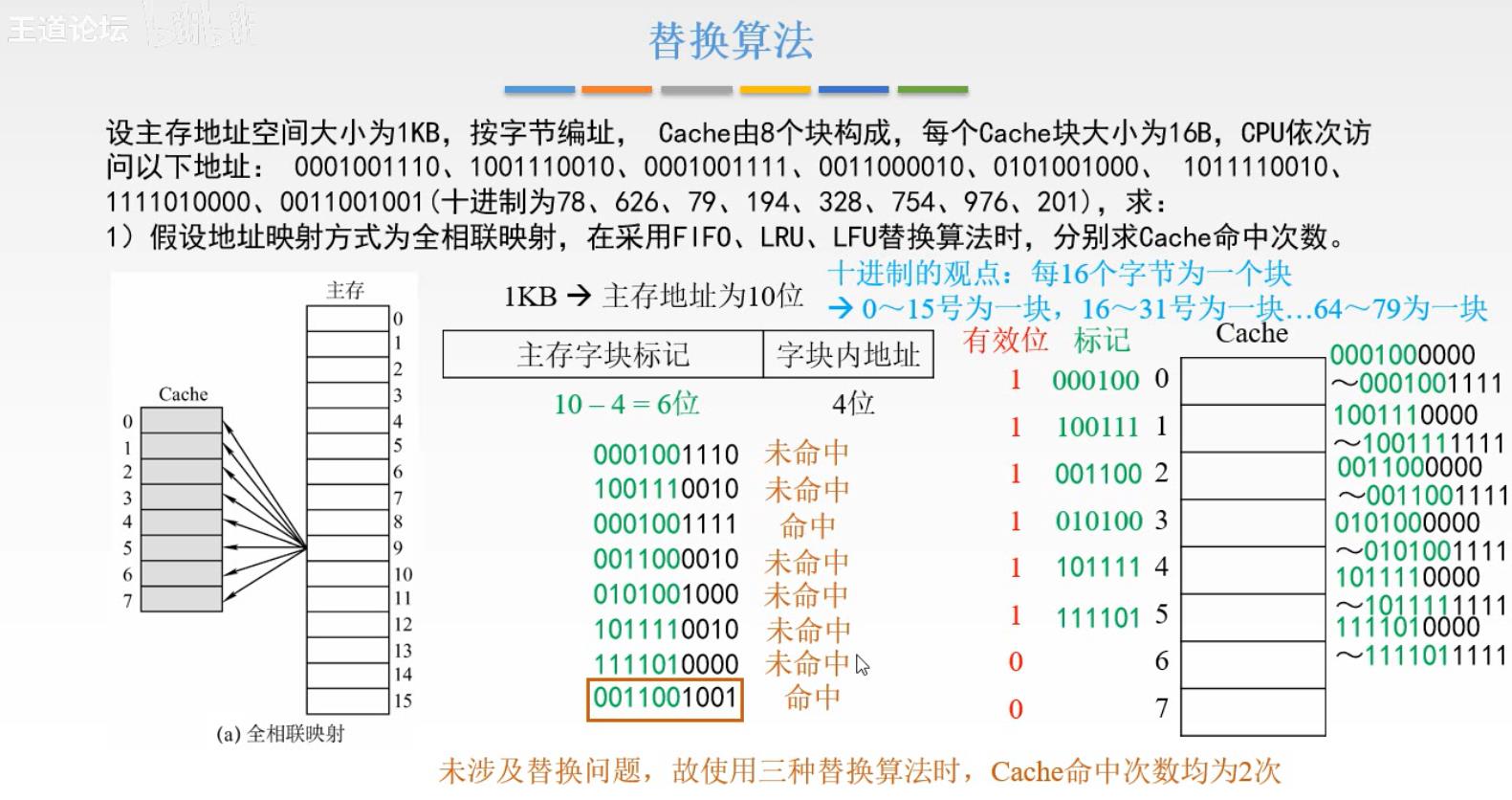

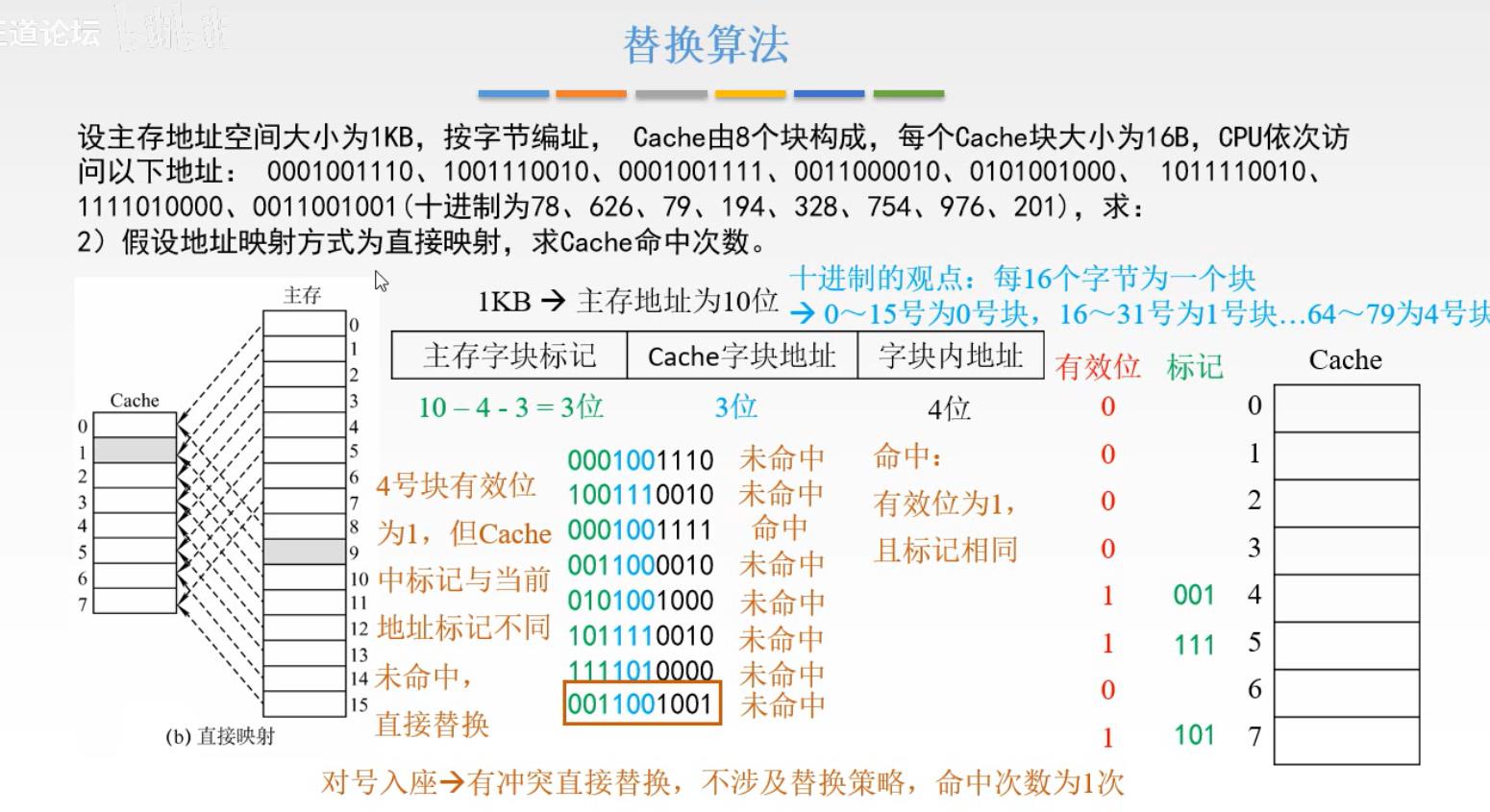

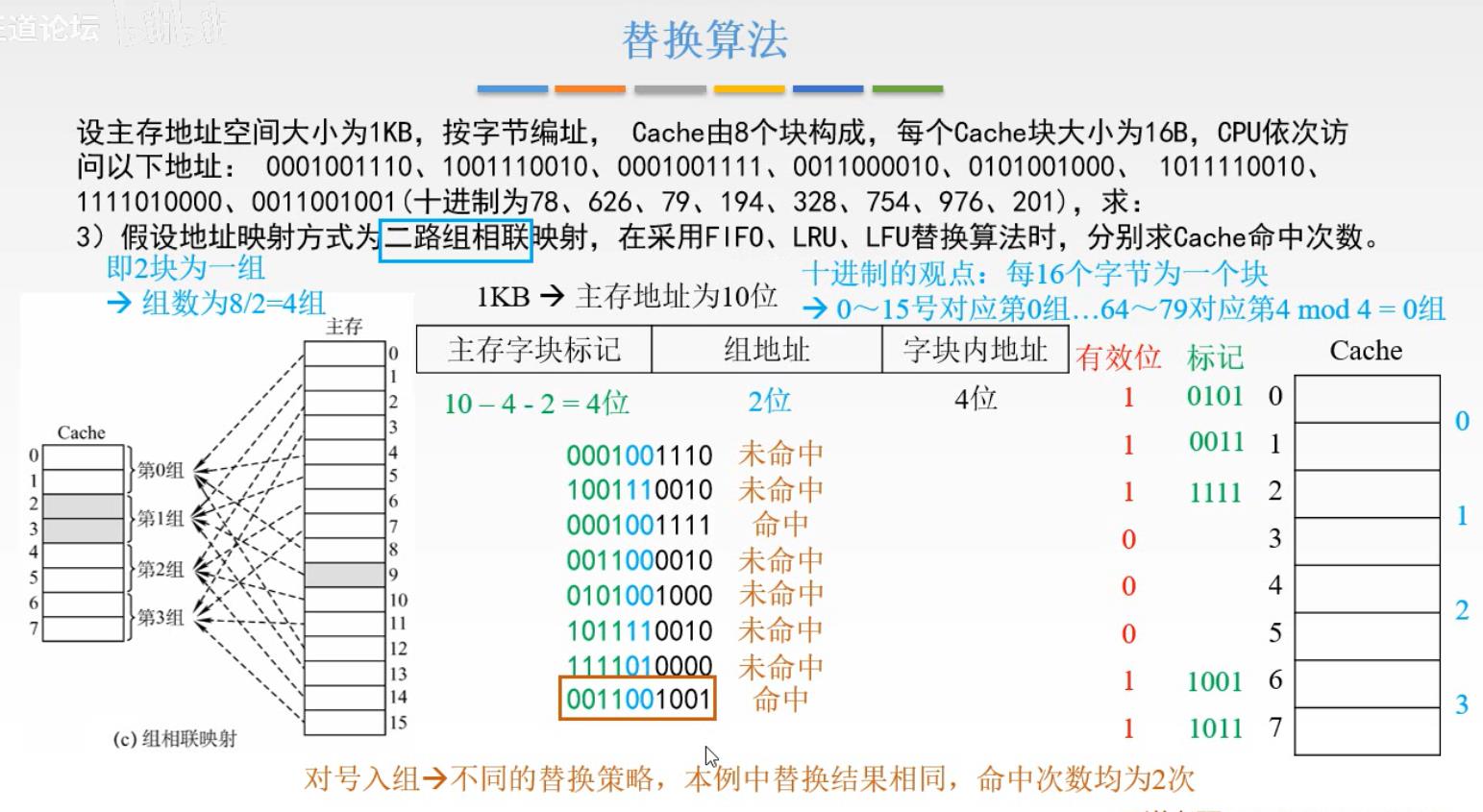

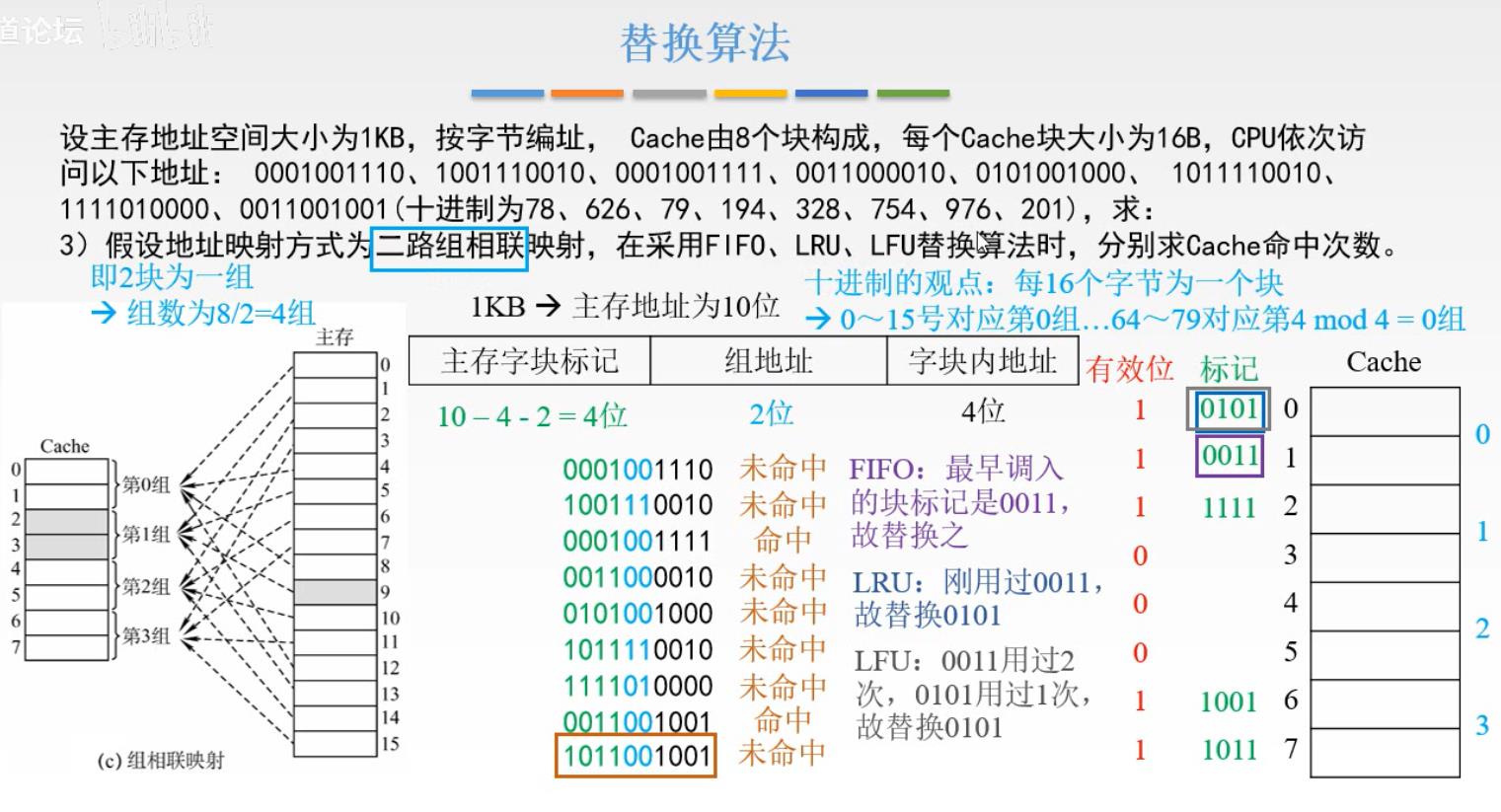

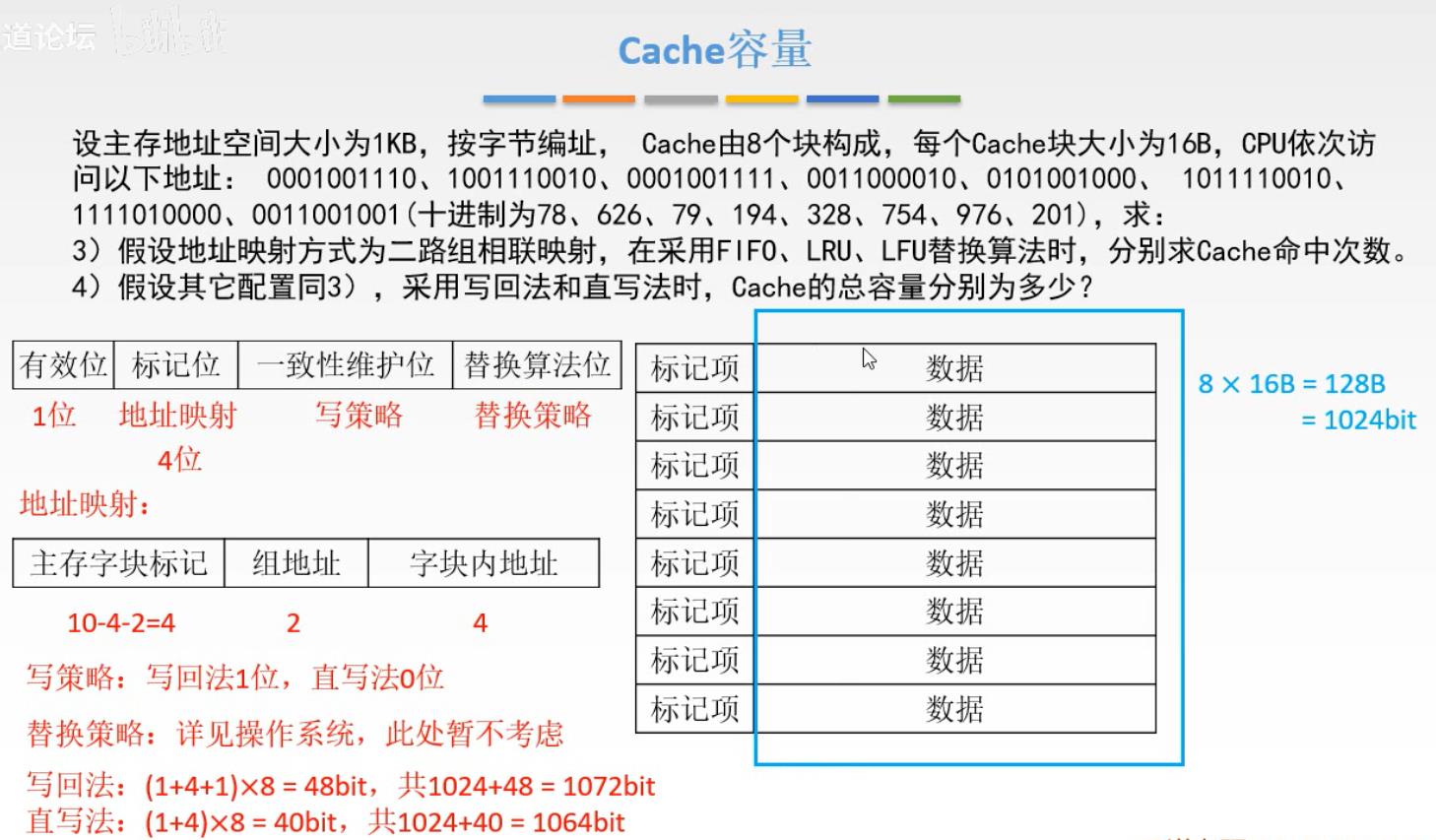

3.6.4 Cache中主存块的替换算法

- 随机算法(RAND):随机地确定替换的 Cache块。它的实现比较简单,但没有依据程序访问的局部性原理,故可能命中率较低

- 先进先出算法(FIFO):选择最早调入的行进行替换。它比较容易实现,但也没有依据程序访问的局部性原理,可能会把一些需要经常使用的程序块(如循环程序)也作为最早进入 Cache的块替换掉。

- 近期最少使用算法(LRU):依据程序访问的局部性原理选择近期内长久未访问过的存储行作为替换的行,平均命中率要比FFO要高,是堆栈类算法。

LRU算法对每行设置一个计数器, Cache每命中一次,命中行计数器清0,而其他各行计数器均加1,需要替换时比较各特定行的计数值,将计数值最大的行换出。 - 最不经常使用算法(LFU):将一段时间内被访问次数最少的存储行换出。每行也设置一个计数器,新行建立后从0开始计数,每访问一次,被访问的行计数器加1,需要替换时比较各特定行的计数值,将计数值最小的行换出。

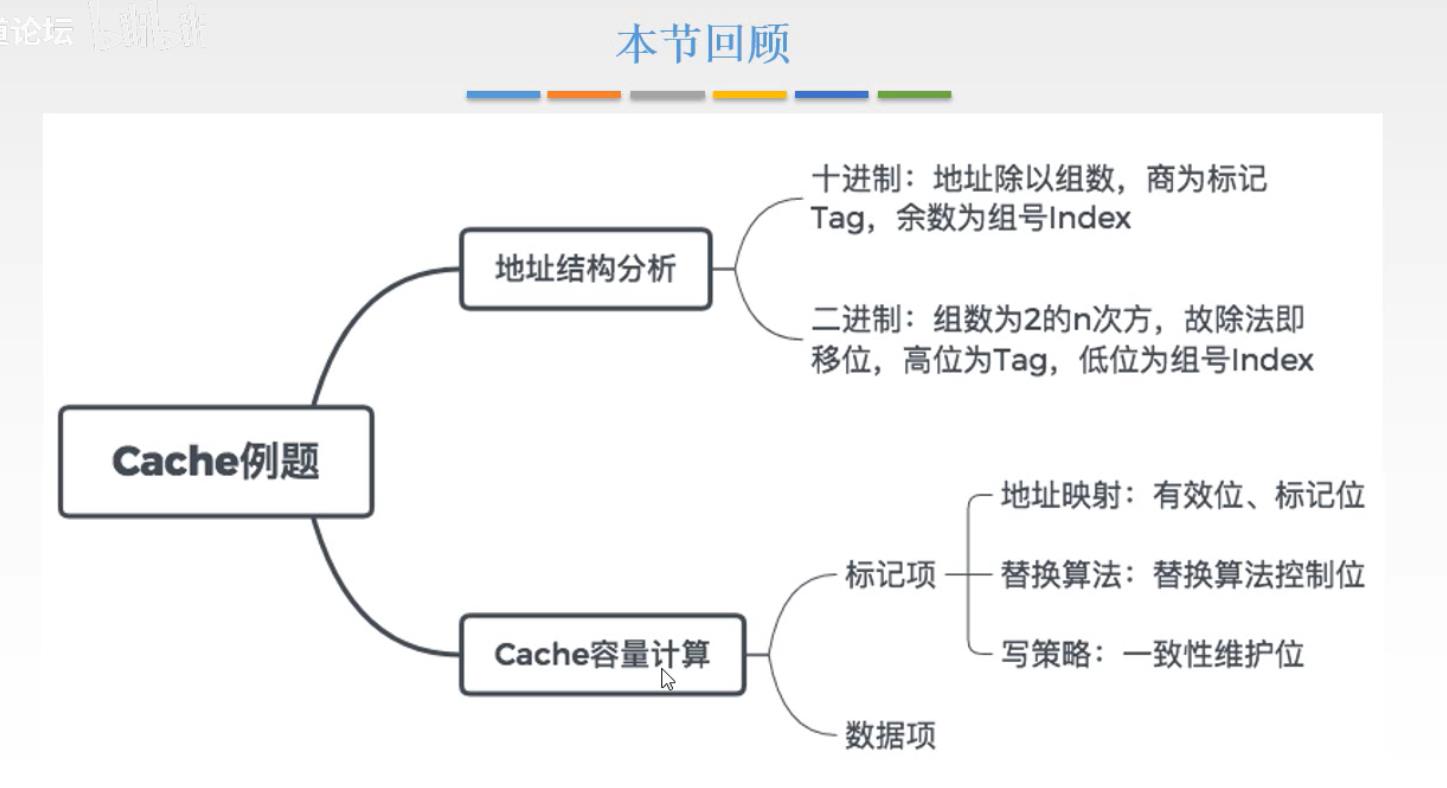

Cache例题

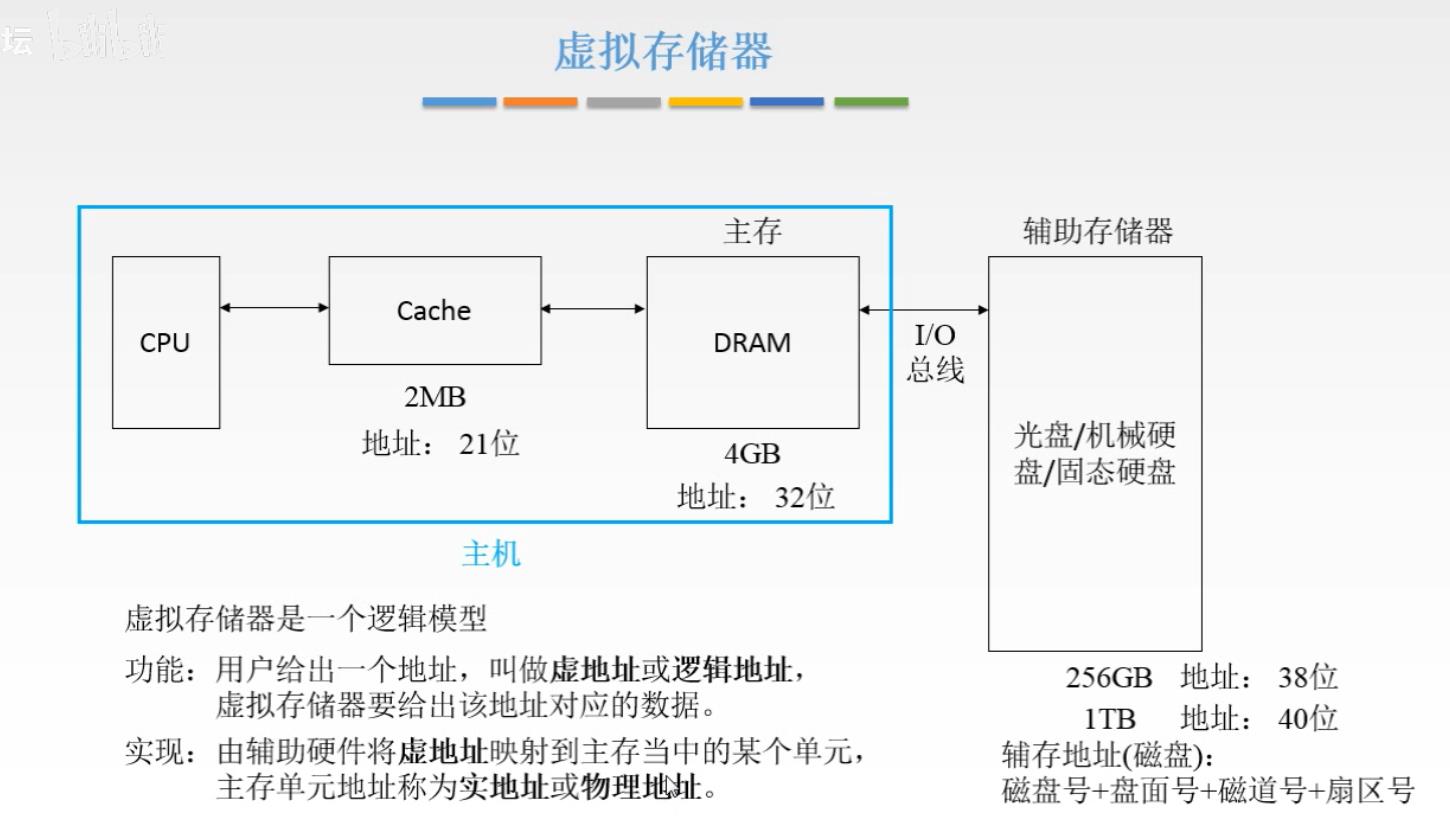

3.7 虚拟存储器

3.7.1 虚拟存储器的基本概念

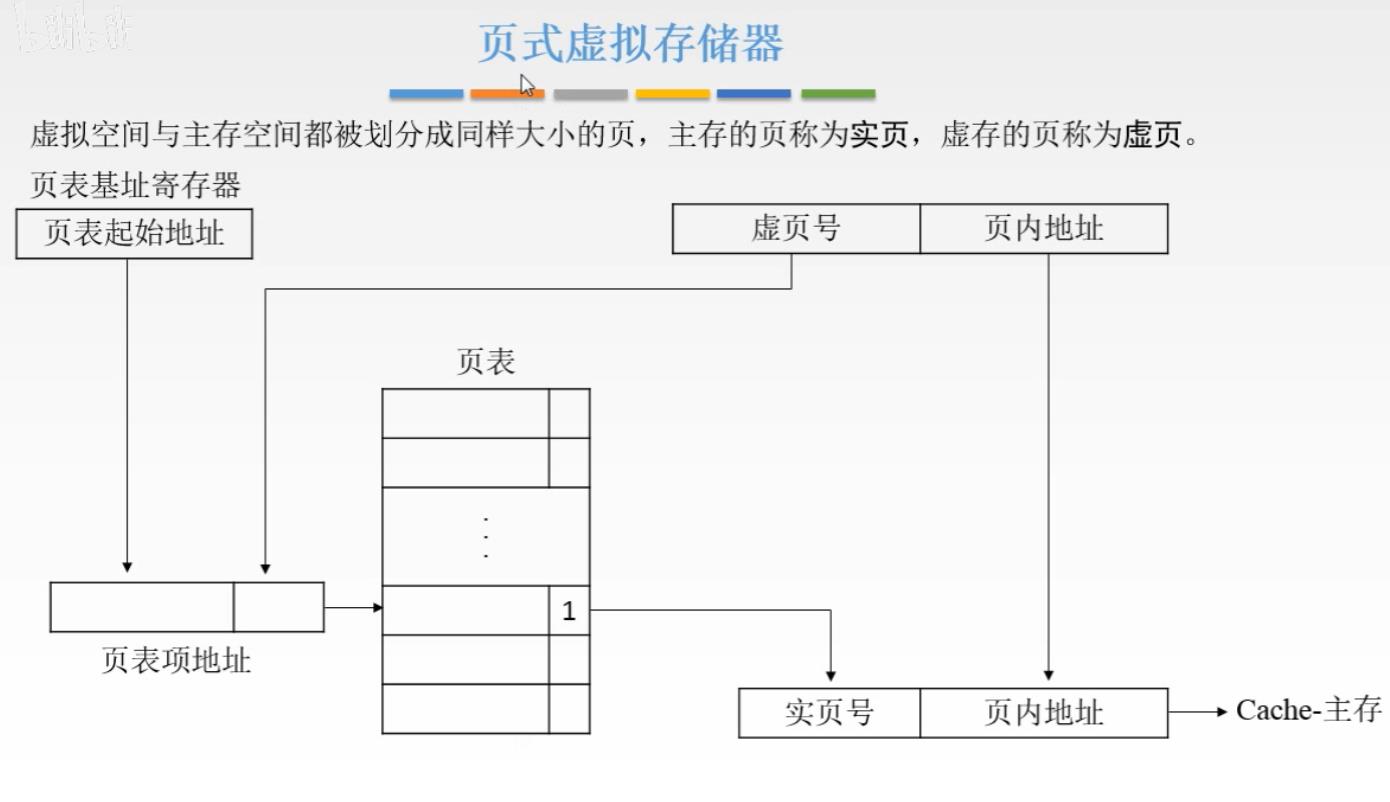

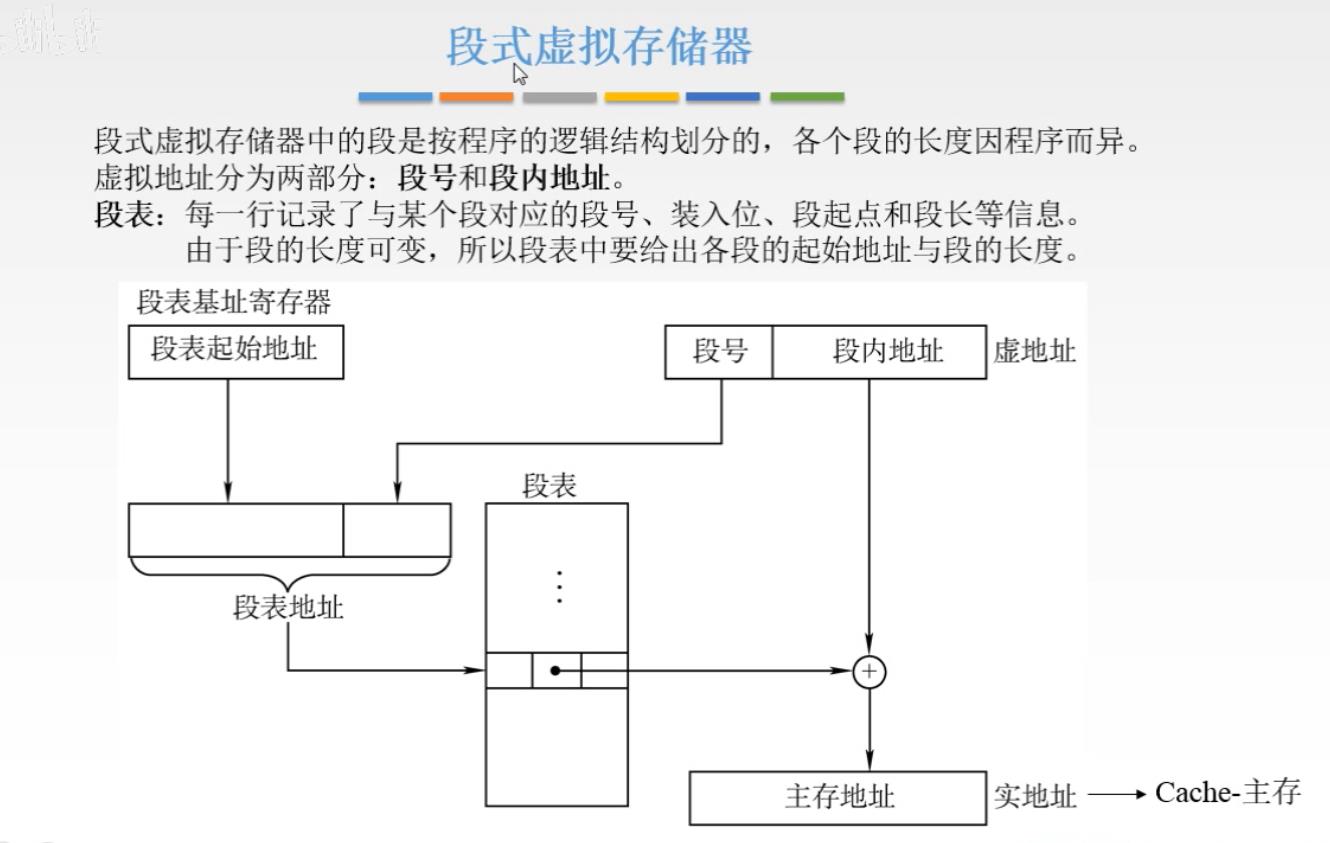

3.7.5 段页式虚拟存储器

把程序按逻辑结构分段,每段再划分为固定大小的页,

主存空间也划分为大小相等的页,

程序对主存的调入、调出仍以页为基本传送单位。

每个程序对应一个段表,每段对应一个页表

虚拟地址:段号+段内页号+页内地址

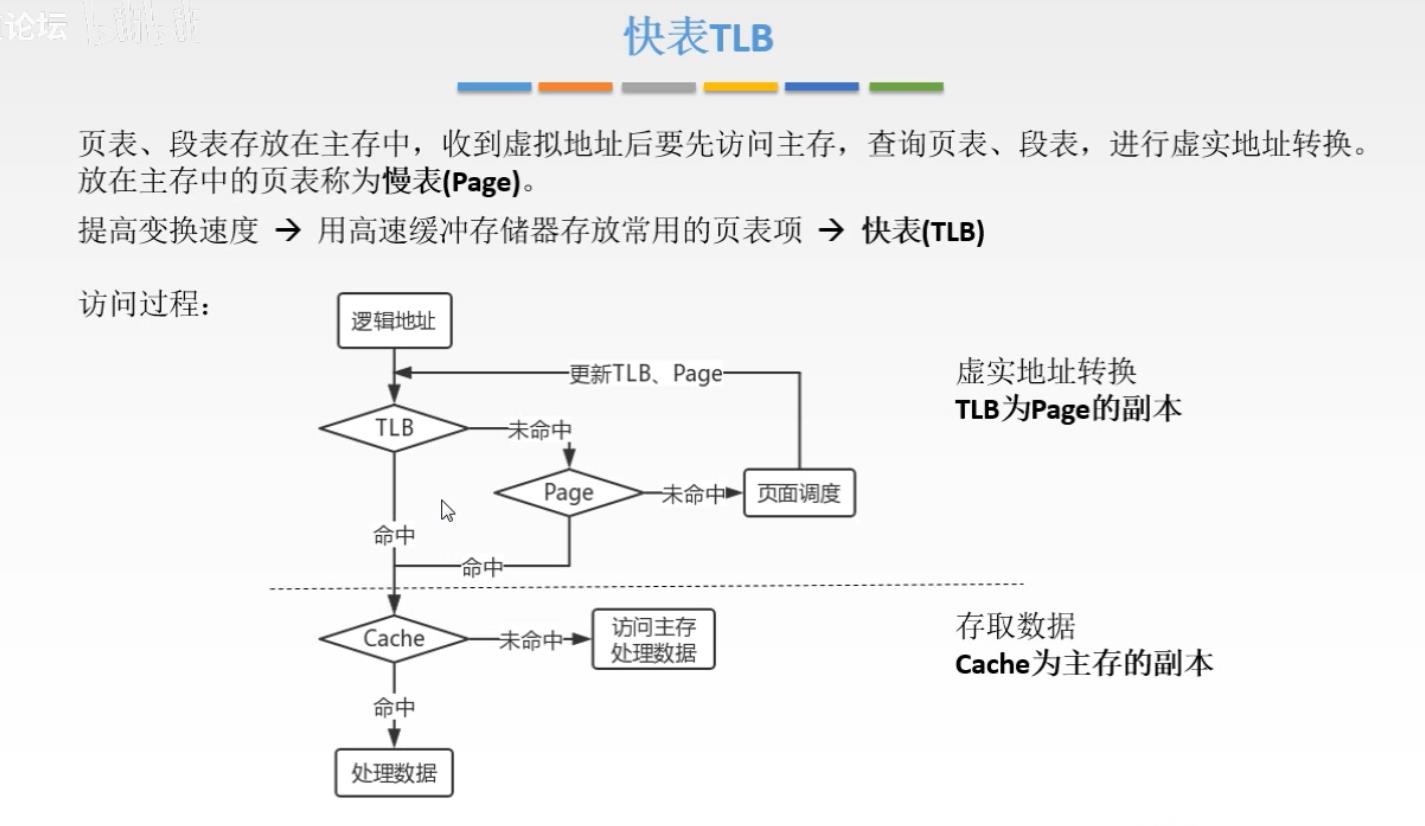

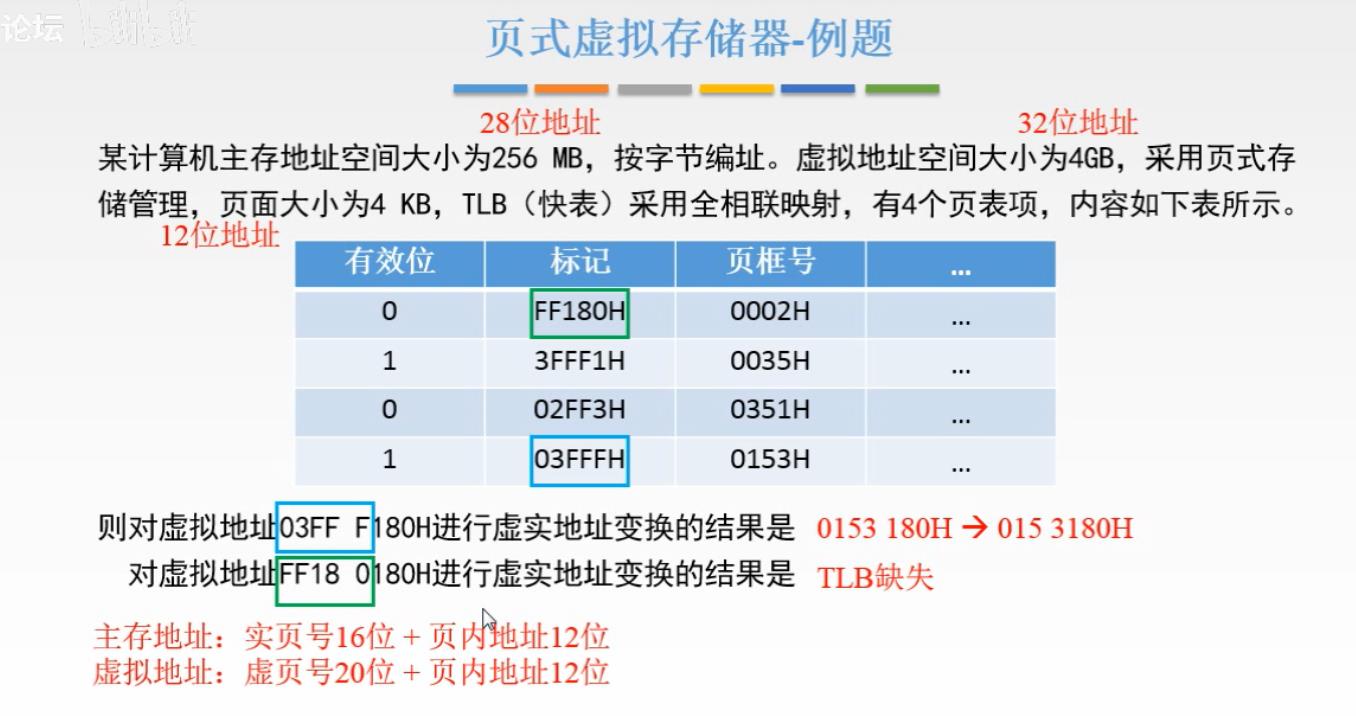

3.7.3 快表(TLB)

页表、段表存放在主存中,收到虚拟地址后要先访问主存,査询页表、段表,进行虚实地址转换。

放在主存中的页表称为慢表(Page)

提高变换速度→用高速绥沖存储器存放常用的页表项 → 快表(TLB)

3.8 本章开头提出的问题回答

1)存储器的层次结构主要体现在何处?为何要分这些层次?计算机如何管理这些层次?

-

1)存储器的层次结构主要体现在何处?为何要分这些层次?计算机如何管理这些层次?

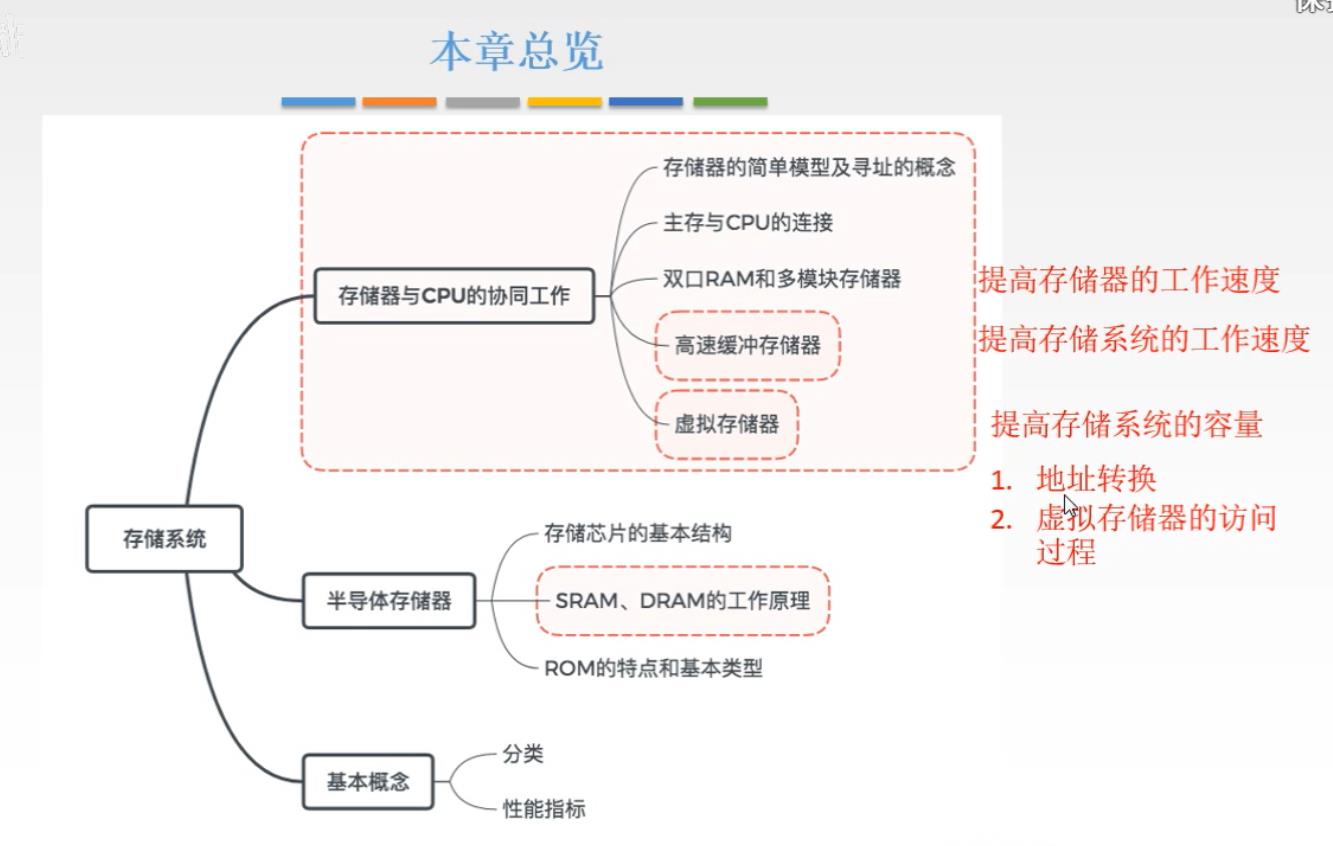

存储器的层次结构主要体现在 Cache-主存和 主存-辅存这两个存储层次上。

Cache-主存层次在存储系统中主要 对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于 Cache的速度,而寻址空间和位价却接近于主存。

主存-辅存层次在存储系统中主要 起扩容作用,即从程序员的角度看,他所使用的存储器的容量和位价接近于辅存,而速度接近于主存。

综合上述两个存储层次的作用,从整个存储系统来看,就达到了速度快、容量大、位价低的优化效果。

主存与 Cache之间的信息调度功能全部由硬件自动完成。而主存与辅存层次的调度目前广泛采用虚拟存储技术实现,即将主存与辅存的一部分通过软/硬结合的技术组成虚拟存储器,程序员可用这个比主存实际空间(物理地址空间)大得多的虚拟地址空间(逻辑地址空间)编程,当程序运行时,再由软/硬件自动配合完成虚拟地址空间与主存实际物理空间的转换。因此,这两个层次上的调度或转换操作对于程序员来说都是透明的。

2)存取周期和存取时间有何区别?

-

2)存取周期和存取时间有何区别?

存取周期和存取时间的主要区别是:存取时间仅为完成一次操作的时间;而存取周期不仅包含操作时间,而且包含操作后线路的恢复时间,即存取周期=存取时间+恢复时间。(这是不是也可以解释,为什么IC前端,时序分析中有建立时间和保持时间吧)

3)在虚拟存储器中,页面是设置得大一些好还是设置得小一些好?

-

3)在虚拟存储器中,页面是设置得大一些好还是设置得小一些好?

页面不能设置得过大,也不能设置得过小。因为页面太小时,平均页内剩余空间较少,可节省存储空间,但会使得页表增大,而且页面太小时不能充分利用访存的空间局部性来提高命中率;页面太大时,可减少页表空间,但平均页内剩余空间较大,会浪费较多存储空间,页面太大还会使页面调入/调出的时间较长

3.9 常见问题

1.存取时间Ta就是存储周期Tm吗?

-

1.存取时间Ta就是存储周期Tm吗?

不是。存取时间Ta是执行一次读操作或写操作的时间,分为读出时间和写入时间。读出时间是从主存接收到有效地址开始到数据稳定为止的时间;写入时间是从主存接收到有效地址开始到数据写入被写单元为止的时间。

存储周期Tm是指存储器进行连续两次独立地读或写操作所需的最小时间间隔。所以存取时间Ta不等于存储周期Tm。通常存储周期Tm大于存取时间Ta。

2. Cache行的大小和命中率之间有什么关系?

-

2.Cache行的大小和命中率之间有什么关系?

行的长度较大,可以充分利用程序访问的空间局部性,使一个较大的局部空间被一起调到Cache中,因而可以增加命中机会。但是,行长也不能太大,主要原因有两个:

1)行长大使失效损失变大。也就是说,若未命中,则需花更多时间从主存读块。

2)行长太大, Cache项数变少,因而命中的可能性变小

3.发生取指令 Cache缺失的处理过程是什么?

-

3.发生取指令 Cache缺失的处理过程是什么?

1)程序计数器恢复当前指令的值。

2)对主存进行读的操作。

3)将读入的指令写入 Cache中,更改有效位和标记位。

4)重新执行当前指令。

4.关于 Cache的一些小知识

-

4.关于 Cache的一些小知识。

1)多级 Cache。现代计算机系统中,一般采用多级的 Cache系统。CPU执行指令时,先到速度最快的一级 Cache( LI Cache)中寻找指令或数据,找不到时,再到速度次快的二级Cache(L2 Cache)中找…最后到主存中找。

2)指令 Cache和数据 Cache。指令和数据可以分别存储在不同的 Cache中( LI Cache一般会这么做),这种结构也称哈佛 Cache,其特点是允许CPU在同一个 Cache存储周期内同时提取指令和数据,由于指令执行过程取指和取数据都有可能访问 Cache,因此这一特性可以保证不同的指令同时访存。

西数退出存储系统市场

| 导读 | WDC西数公司今天突然宣布退出存储系统市场,将旗下的IntelliFlash业务出售给了DataDirect Networks(简称DDN)公司。此外另一部分存储系统业务ActiveScale也将寻求出售。 |

西数退出存储系统市场?是,不过这里说的存储系统并不是普通玩家理解的闪存、硬盘之类的,这部分依然是西数的核心业务,而西数不干了的存储系统业务实际上是存储系统阵列,换句话说西数还是决定自己当个基础的元件供应商,不再自己做存储系统阵列卖给其他公司了。

即便如此,这样的决定还是让很多人意外,因为西数公司的IntelliFlash业务是2017年9月收购Tegile Systems闪存公司时才获得的,刚刚2年时间就卖掉了,实在有点不寻常,这要么是因为当初收购Tegile Systems闪存公司不是看重这部分业务,要么就是西数觉得存储系统业务玩不转,索性卖掉。

存储系统市场现在倒也不是夕阳产业,在存储系统、高性能计算、数据中心等领域很火,而且接手IntelliFlash业务的DDN公司这两年风头正劲,一年多来先后收购了多家存储系统公司或者业务,包括Intel公司的Lustre业务,还有混合阵列厂商Tintri、软件定义存储厂商Nexenta,现在又拿下了西数的IntelliFlash业务。

西数及DDN都没有公布具体的交易金额,预计在2020财年Q3季度中会产生每股0.2美元的非GAAP收益,不过这也会带来重组及其他费用,暂时还无法估计。

本文转自:https://www.linuxprobe.com/intelliflash-activescale.html

以上是关于存储系统的主要内容,如果未能解决你的问题,请参考以下文章