存储系统

Posted 绀香零八

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了存储系统相关的知识,希望对你有一定的参考价值。

文章目录

存储系统的层次结构

· 存储系统:容量越大越好、速度较快越好、价格(成本)越低越好

· 当前制造工艺的存储器件:工作速度较快的存储器,单位价格却较高;容量较大的存储器,虽然单位价格较低,但存取速度又较慢

各种存储器件需要相互配合形成完整的存储系统

技术指标

存储器主要用容量、速度和成本来评价

- 存储容量

主存存储容量:以字节B(Byte)为基本单位

半导体存储器芯片:以位b (Bit)为基本单位

存储容量以2^10=1024规律表达KB,MB,GB和TB

厂商常以10^3=1000规律表达KB,MB,GB和TB - 存取速度

存取时间:发出读/写命令到数据传输操作完成所经历的时间

存取周期:两次存储器访问所允许的最小时间间隔

层次结构

· 寄存器:处理器内部的存储单元

· 高速缓存(Cache):完全用硬件实现主存储器的速度提高

· 主存储器:存放当前运行程序和数据,采用半导体存储器构成

· 辅助存储器:磁记录或光记录方式。磁盘或光盘形式存放可读可写或只读内容,以外设方式连接和访问

解决容量、速度和价格矛盾的方法

局部性原理

· 层次结构解决存储器件的容量、速度和价格矛盾

· 出色效率来源于存储器访问的局部性原理:处理器访问存储器时,所访问的存储单元在一段时间内都趋向于一个较小的连续区域中

· 空间局部:紧邻被访问单元的地方也将被访问

· 时间局部:刚被访问的单元很快将再次被访问

· 程序运行过程中,绝大多数情况都能够直接从快速的存储器中获取指令和读写数据;当需要从慢速的下层存储器获取指令或数据时,每次都将一个程序段或一个较大数据块读入上层存储器,后续操作就可以直接访问快速的上层存储器

主存储器

· 主存储器由半导体存储器构成

· 按制造工艺,半导体存储器可分为:

“双极型”器件:存取速度快、集成度低、功耗大、价格高等特点,主要用于高速存储场合;

“MOS型”器件:集成度高、功耗低、价格便宜,但速度较双极型器件慢,用于通用微机的主存(RAM和ROM)

· 按使用属性,半导体存储器可分为:读写存储器RAM、只读存储器ROM

读写存储器

· 读写存储器:可以读出也可以写入的存储器

· 半导体存储器采用随机存取:可以从任意位置开始读写,存取位置可以随机确定,只要给出存取位置就可以读写内容,存取时间与所处位置无关

· 磁带存储器采用顺序存取:必须按照存储单元的顺序读写,存取时间与所处位置密切相关

· 磁盘和光盘则采用直接存取:磁头以随机方式寻道,以数据块为单位顺序方式读写扇区

· 半导体读写存储器是挥发性(Volatile)RAM,即断电后原保存信息丢失

半导体读写存储器=随机存取存储器地址RAM

- 主要类型

· SRAM(静态RAM:Static RAM)

以触发器为基本存储单元,不需要额外的刷新电路,速度快,但集成度低,功耗和价格较高

· DRAM(动态RAM:Dynamic RAM)

以单个MOS管为基本存储单元,要不断进行刷新(Refresh)操作,集成度高、价格低、功耗小,但速度较SRAM慢 - 存储结构

· 存储器芯片具有大量存储单元

· 每个存储单元拥有一个地址

· 存储1/4/8/16/32位数据

· 存储器芯片结构:

M个地址信号可以去别2^M个存储单元, 2 ^M个存储单元需要M个地址信号。

存储单元数×每个存储单元的数据位数=2^M×N=芯片的存储容量

M=芯片地址线的个数; N=数据线的个数/数据引脚的个数

存储结构2K×8

16K位存储容量

具有2K个存储单元

11个地址引脚(2K=2^11)

8个数据引脚

- 读写控制

· 片选(CS或CE)

片选有效,才可以对芯片进行读/写操作。无效时,数据引脚呈现高阻状态,并可降低功耗

· 读控制(OE*)

芯片被选中有效,数据输出到数据引脚。对应存储器读MEMR*

· 写控制(WE*)

芯片被选中的前提下,若有效,将数据写入。对应存储器写MEMW* - 静态读写存储器SRAM

· 主要被用于小型微机系统

· 多为“存储单元数×8”的存储结构

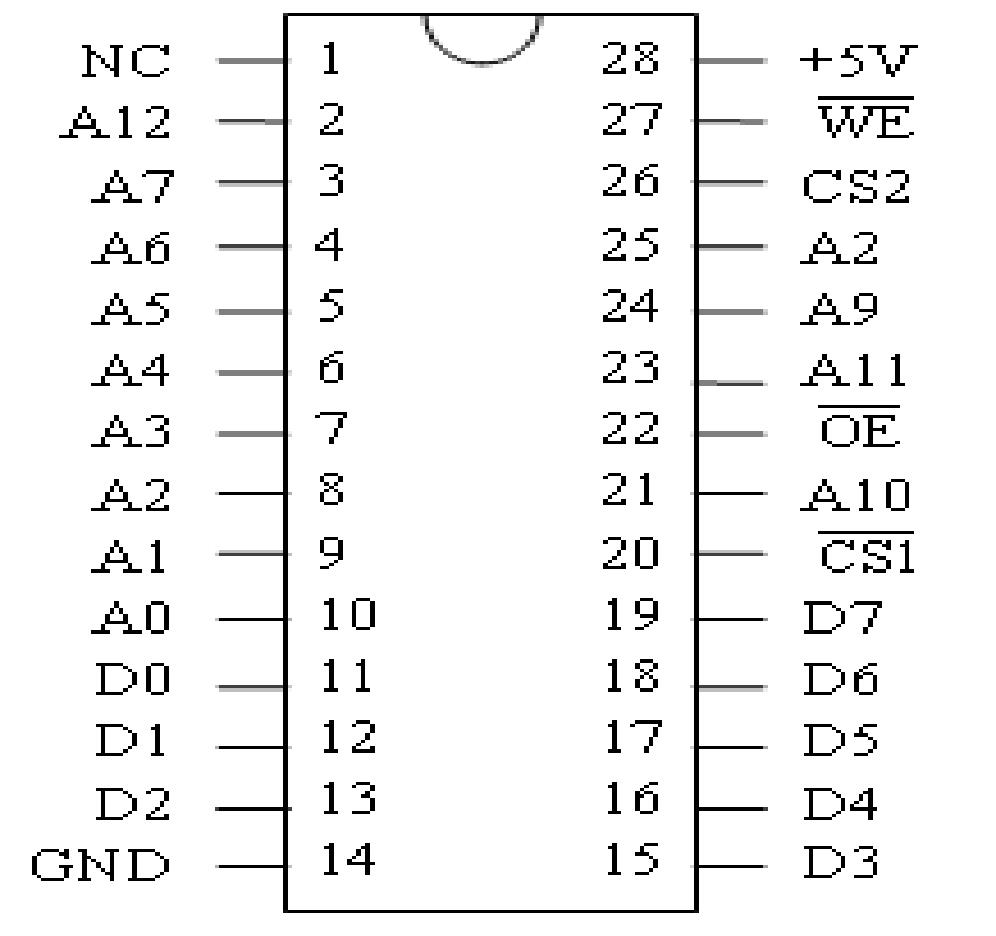

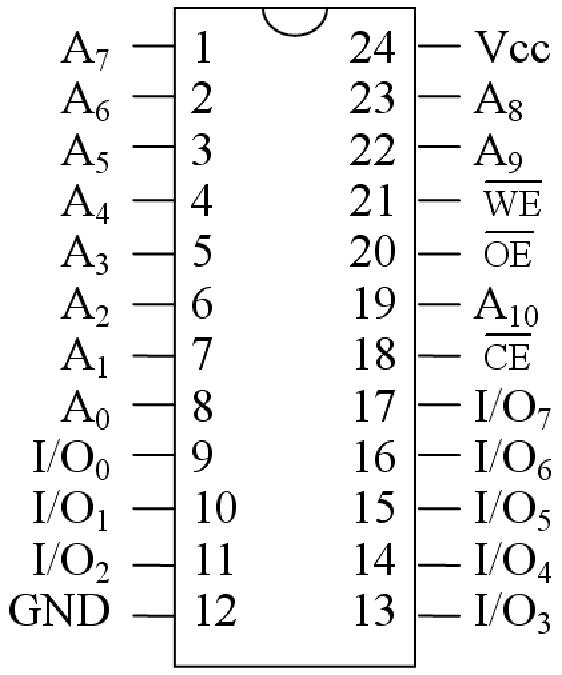

· 6264 SRAM芯片

芯片容量:64K位

存储结构:8K×8

28脚双列直插(DIP)

13个地址线:A12~A0

8个数据线:D7~D0

控制引脚:CS1*,CS2,OE*,WE*

无连接:NC(No Connect)

6264 SRAM的引脚

6264 SRAM的引脚功能表

设计了两个片选引脚:CS1*低电平有效,CS2高电平有效

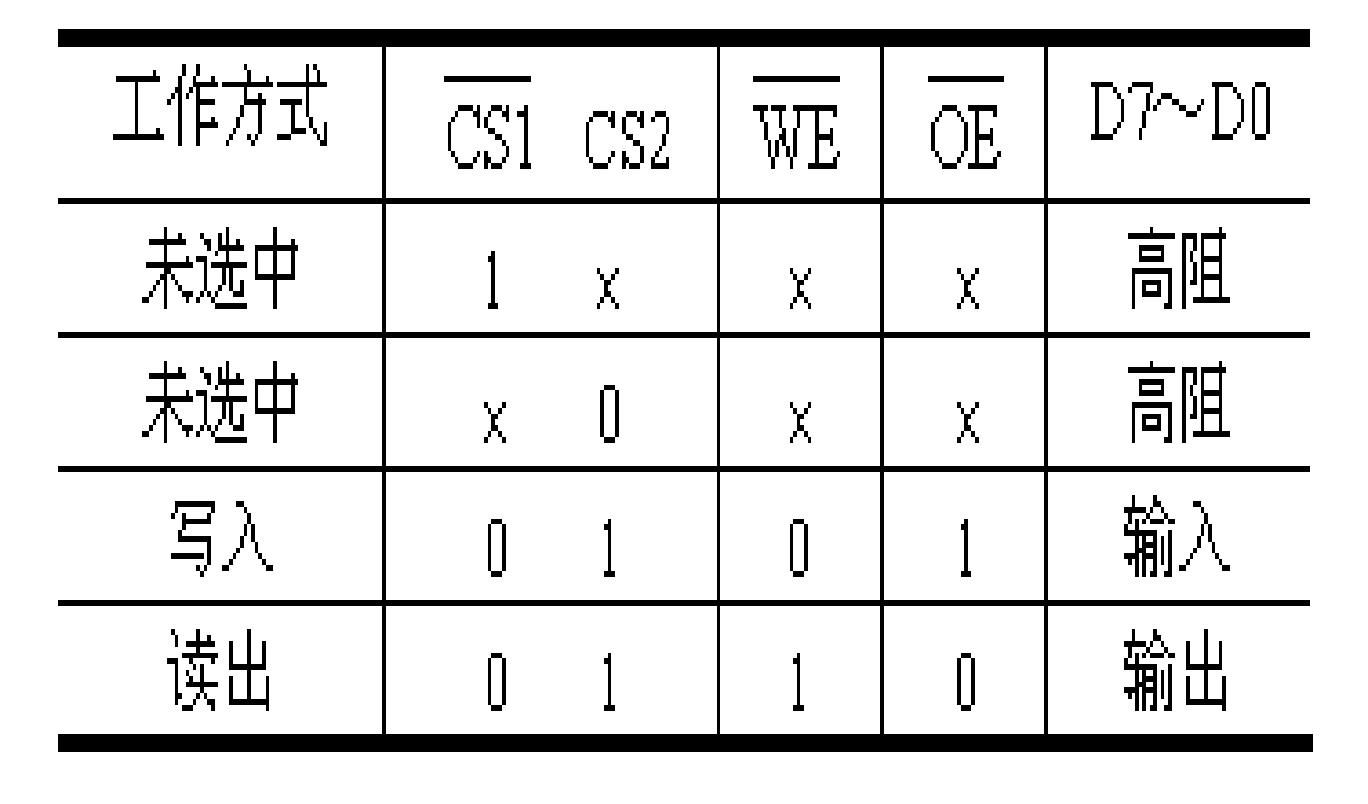

- 动态读写存储器DRAM

· DRAM芯片用一组地址引脚传送两批地址信号

· 第一批地址称行地址

用行地址选通信号RAS下降沿锁存

· 第二批地址称列地址

用列地址选通信号CAS下降沿锁存

· 一个信号WE*实现读写控制

· 数据输入引脚Din

· 数据输出引脚Dout

DRAM的引脚图

- DRAM的刷新

· DRAM内部

有“读出再生放大电路”的刷新电路

设计有仅行地址有效的刷新周期

每次刷新一行存储单元

· 存储系统的外部刷新控制电路

将刷新行地址同时送达所有DRAM芯片

所有DRAM芯片同时进行一行的刷新

在一定时间间隔内启动一次刷新

每次行地址增量

*只读存储器

· 正常的工作状态,ROM只能读出

· 特殊的编程状态,多数ROM芯片也能写入

· 有些ROM芯片需要特殊方法先将原数据擦除,然后才能编程

· ROM芯片的集成度较高,但速度较DRAM还要慢,一般用来保存固定的程序或数据

· ROM芯片数据可长期保存,掉电亦不丢失,属于非易失性存储器件

- 主要类型

· MROM(掩膜ROM)

掩膜工艺直接制作

· OTP-ROM(一次性编程ROM)

允许用户进行一次性编程

· EPROM(可擦除可编程ROM)

紫外光擦除、并可重复编程的ROM

· EEPROM(电擦除可编程ROM)

擦除和编程(擦写)通过加电进行

· Flash Memory(闪速存储器)

新型的电擦除可编程ROM

快速擦除整片或数据块 - EPROM

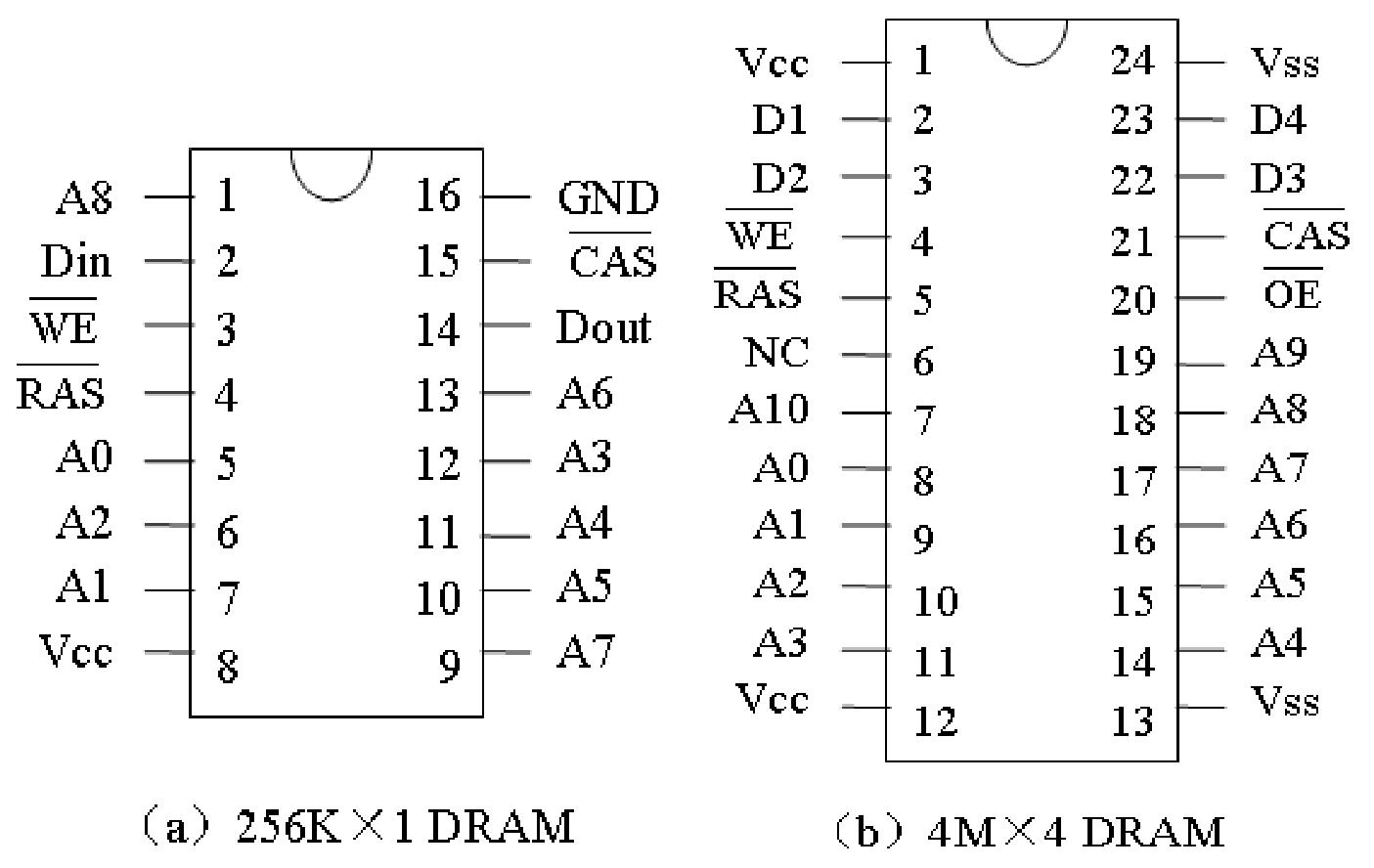

· 2764 EPROM

· 存储容量64K位

· 存储结构8K×8

· 13个地址线:A12~A0

· 8个数据线:O7~O0

· 控制信号

片选:CE*

输出:OE*

编程控制:PGM*

编程电源:Vpp

EPROM工作方式

- EEPROM

· EEPROM 2816

· 存储结构:2K×8

· 有11个地址引脚A10~A0

· 8个数据引脚I/O7~I/O0

· 3个控制引脚

片选CE*

输出允许OE*

写允许WE*

· 字节擦写

· 查询擦写是否完成

- Flash Memory

· AT29C040A

· 存储结构:512K×8

· 有19个地址引脚A18~A0

· 8个数据引脚I/O7~I/O0

· 3个控制引脚

片选CS*

输出允许OE*

写允许WE*

· 扇区(256字节)擦写

· 查询擦写是否完成

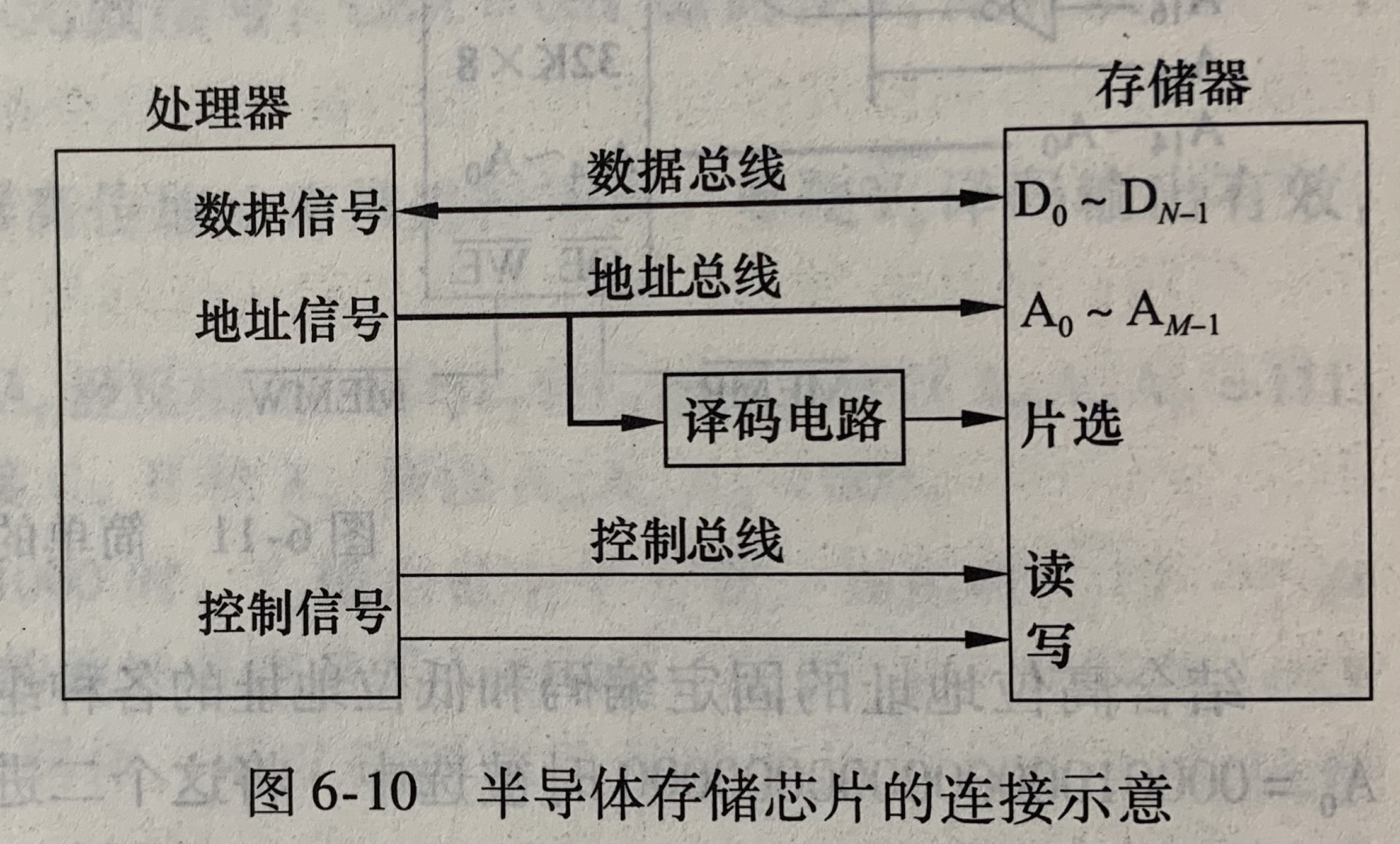

存储器地址译码

· 存储器芯片与处理器的连接

存储器芯片有数据、地址、读写控制引脚

处理器总线有数据、地址、读写控制信号

功能上多数可以直接相连

· 但是,地址信号需要译码

处理器地址总线个数多于存储器地址引脚个数

多个存储器芯片组成一定容量的存储系统

需要利用地址总线控制存储器片选信号

- 地址译码

· 译码(Decode)

将某个特定的编码输入翻译为有效输出的过程

· 存储器译码电路

可编程逻辑器件PLD

译码器

门电路组合

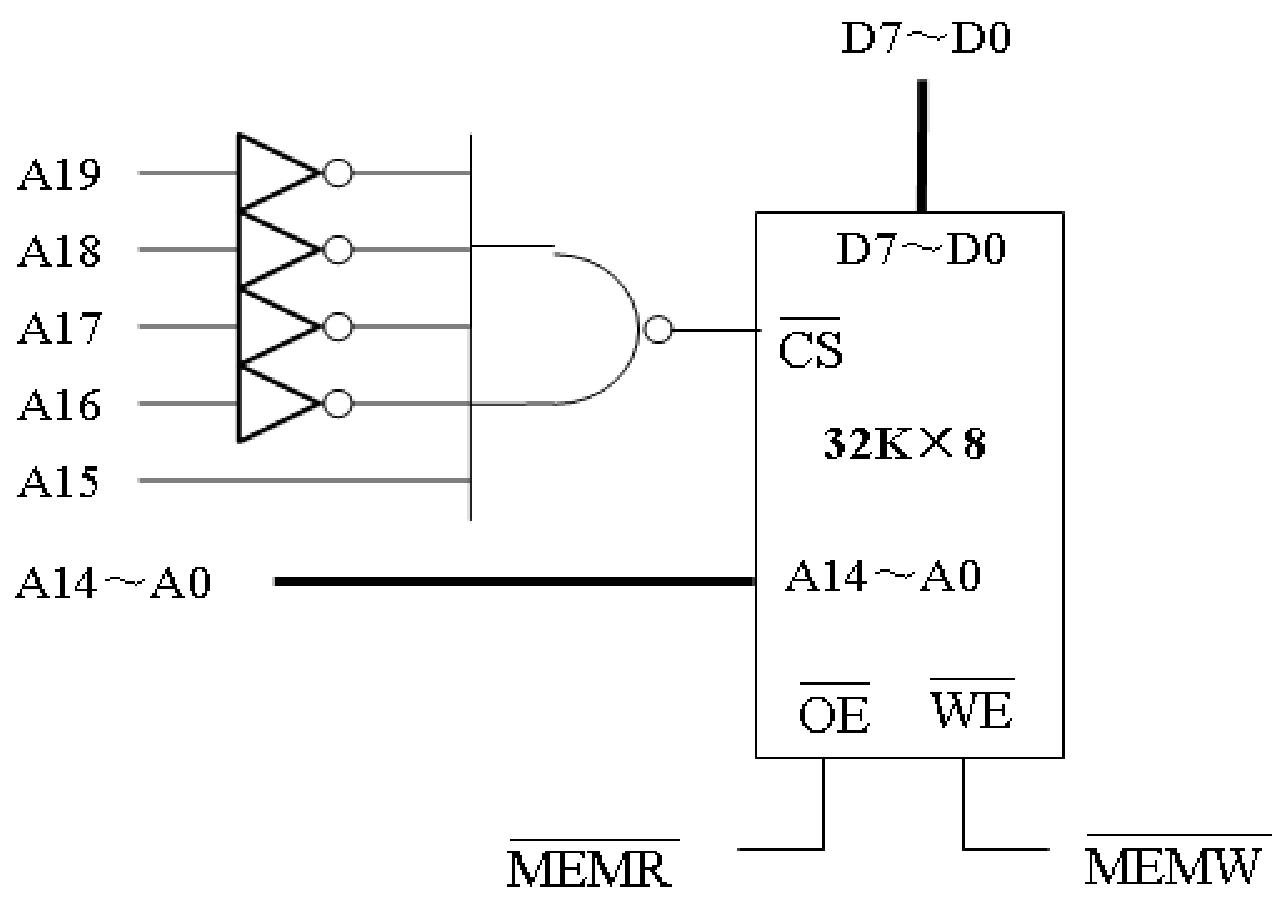

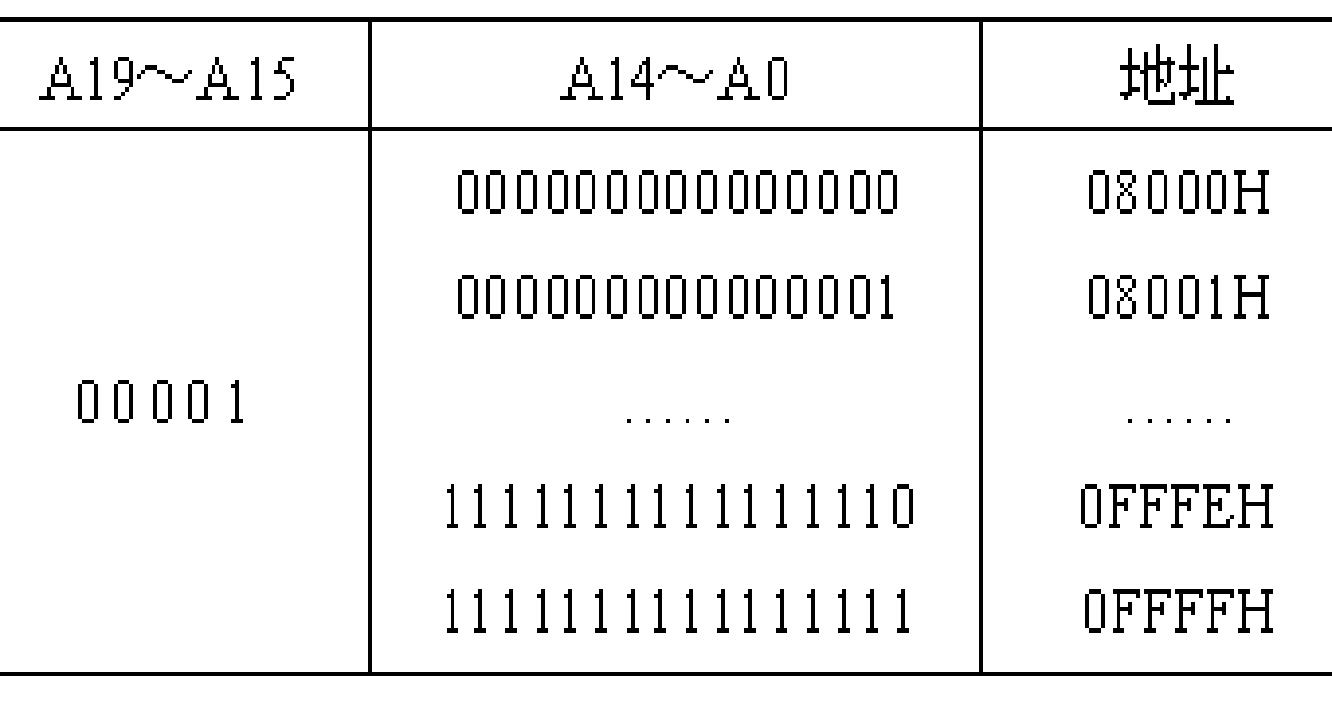

· 举例:多输入与非门实现译码

· 32K×8结构的SRAM:地址引脚15个A14~A0

· 8088处理器:

20个地址总线A19~A0 ;8位数据总线

简单的门电路译码

存储器地址分析

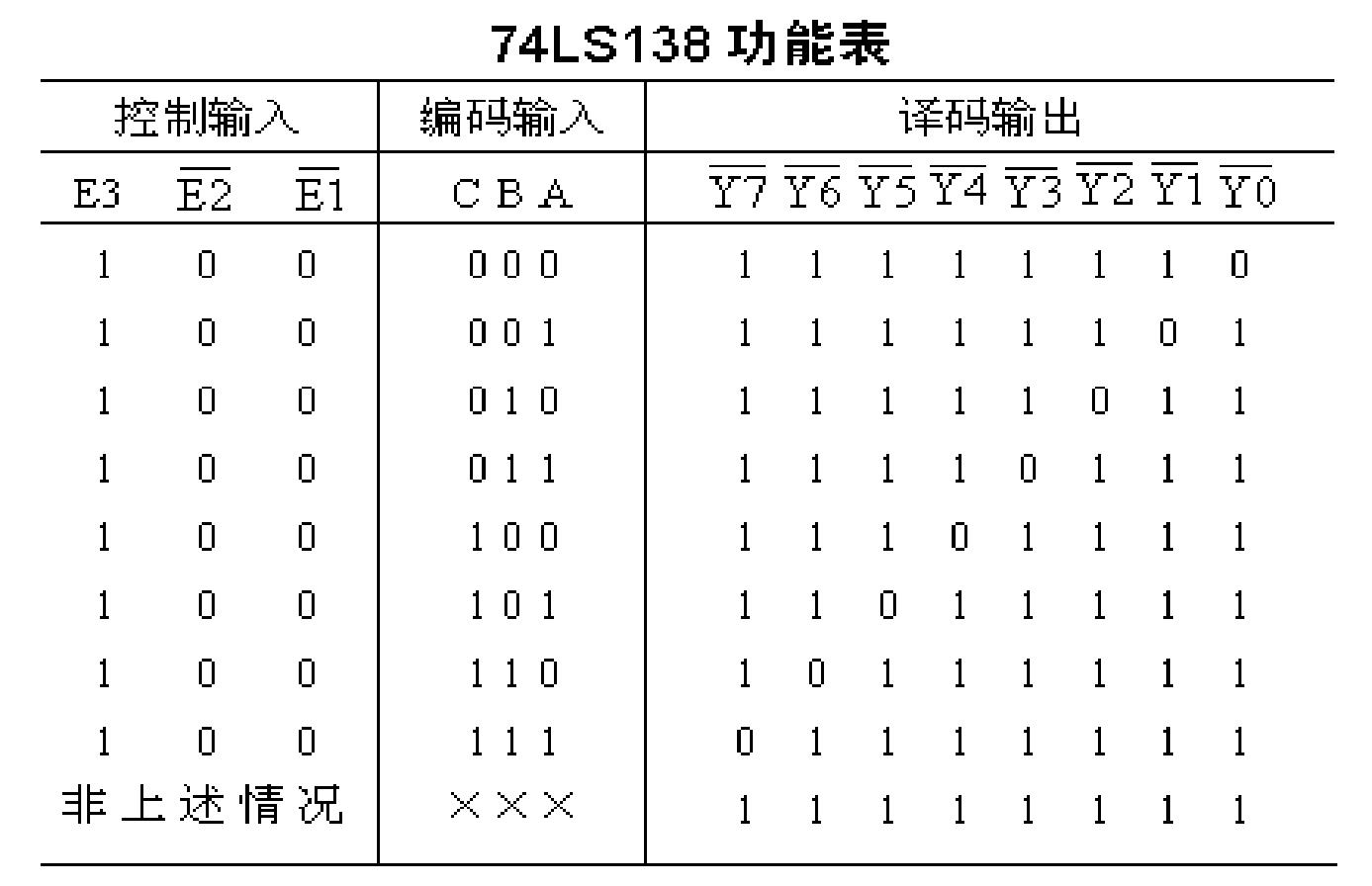

- 译码器

· 3∶8译码器:138译码器

· 3个控制输入引脚:E3,E2* 和E1* 都有效,才能实现译码功能

· 3个编码输入引脚:C,B和A

8种编码各对应一个译码输出引脚

CBA=000编码使Y0低有效,其他高电平无效

CBA=001编码使Y1低有效,其他高电平无效

……

CBA=111编码使Y7*低有效,其它高电平无效

译码器74LS138

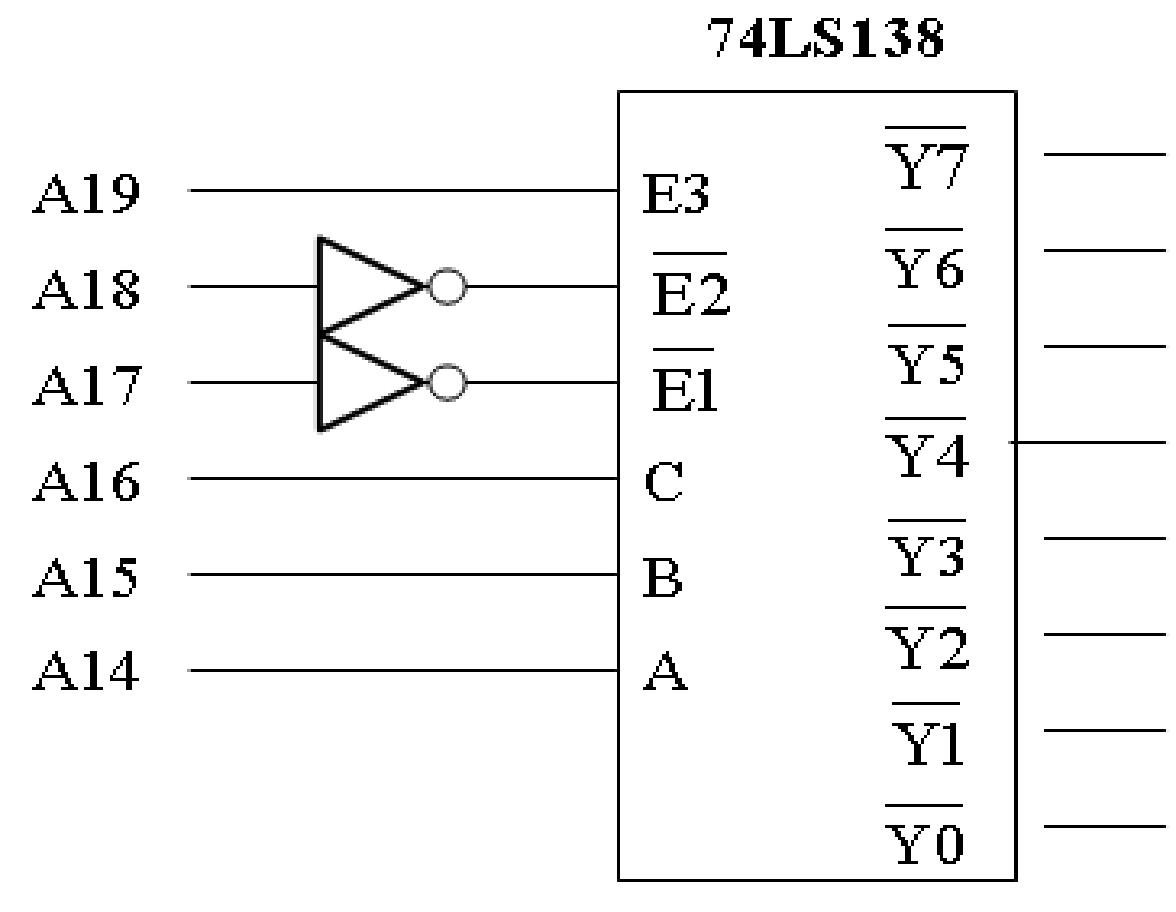

译码器译码

Y0* 译码输出有效,必须:

E3E2* E1*=100

A19A18A17=111

CBA=000

A16A15A14=000。

结论:A19~A14=111000

地址范围:E0000H~E3FFFH

存储容量:16KB

存储容量=结束地址-起始地址+1

译码器译码示意图

不使用A13的译码

存储容量:8KB

A13=0时,地址范围: E0000H~E1FFFH

A13=1时,地址范围: E2000H~E3FFFH

结论:该8KB存储器芯片占用了

E0000H~E1FFFH 地址范围(A13=0)

E2000H~E3FFFH 地址范围(A13=1)

实际应用中,常选择第一个地址

不使用A0的译码

存储容量:8KB

A0=0时,占用E0000H~E3FFFH范围的偶地址

A0=1时,占用E0000H~E3FFFH范围的奇地址

结论:该8KB存储器芯片占用了

E0000H~E3FFFH 偶地址(A0=0)

E0000H~E3FFFH 奇地址(A0=1)

实际应用中,常选择偶地址

译码方式

· 全译码方式 : 地址唯一 空间连续

使用全部微处理器地址总线

片内寻址:低位地址与存储器芯片地址引脚相连

片选寻址:高位地址经译码与存储器芯片片选引脚相连

· 部分译码方式:地址重复,译码简单

只使用部分微处理器地址总线进行译码

没有使用的地址信号对存储器芯片的工作不产生影响

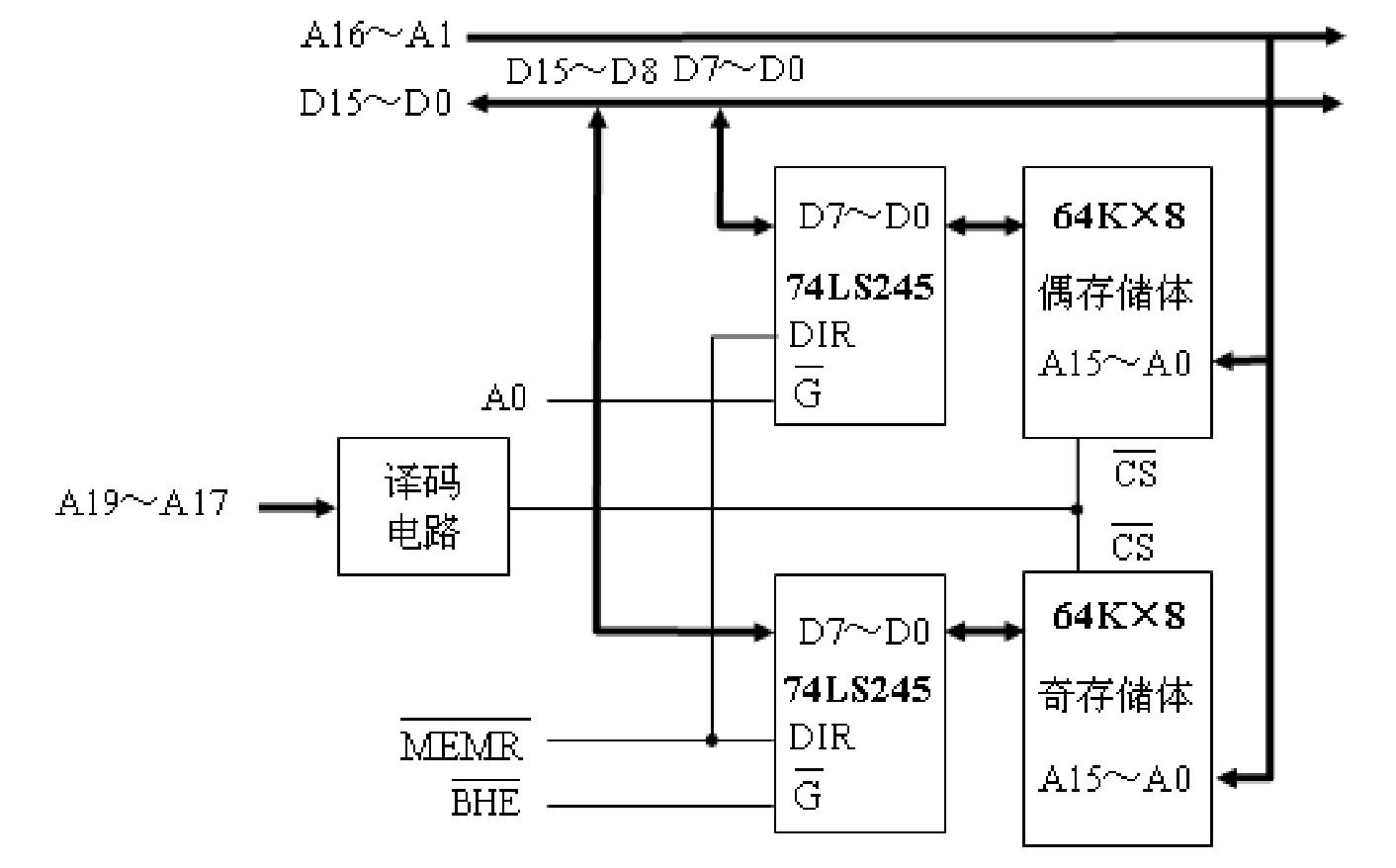

- 8086的16位存储结构

· 对称的两个存储体(Bank)所构成

· 偶存储体(A0=0)

对应所有的偶地址单元(0、2、4、……FFFEH)接处理器低8位数据总线D7~D0

· 奇存储体(BHE*=0)

对应所有的奇地址单元(1、3、5、……FFFFH)接处理器高8位数据总线D15~D8

· 两个存储器芯片的片选端连接在一起

8086的16位存储结构

地址对齐(Align)

· 高位地址A19~A17=111,片选信号有效

· 低位地址A16~A1=0…0,那么:

A0=0(地址E0000H),BHE=0,访问16位数据

A0=0(地址E0000H),BHE=1,访问低8位数据

A0=1(地址E0001H),BHE=0,访问高8位数据

A0=1,BHE=1,无效的数据访问组合

· 8086存储器按16位数据宽度组织

支持8位和16位数据访问

偶地址开始的16位访问可以一次完成

奇地址开始的16位访问需要两次操作

· 地址对齐:16位数据以偶地址开始

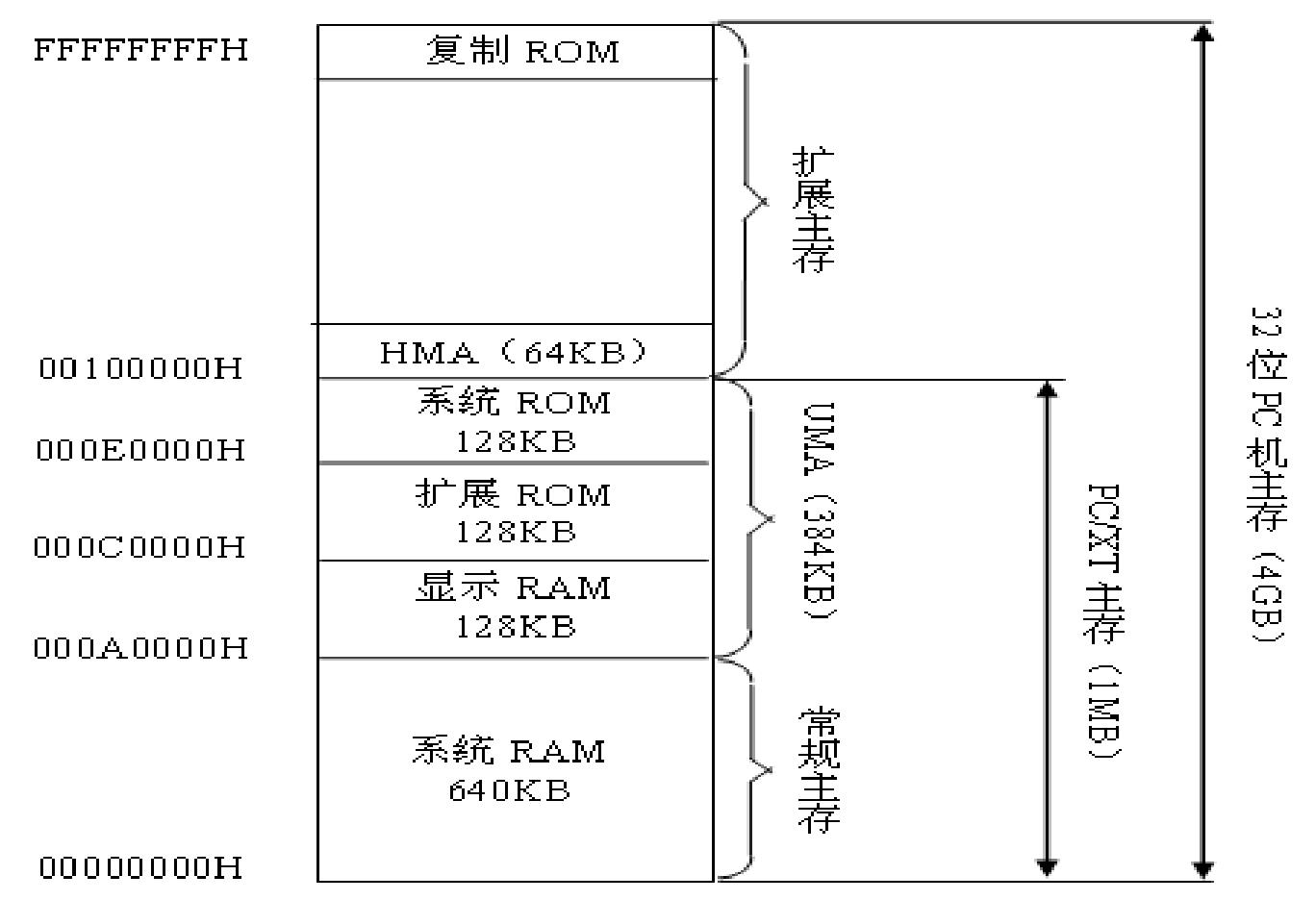

主存空间分配

高速缓冲存储器

主存是一个影响性能的关键因素

因为处理器的运行速度提高,但由DRAM组成的主存的存取时间较慢,跟不上处理器运行速度

SRAM速度较快,但其容量较小、价格较贵,无法大量用于微机系统

解决方案:高速缓存 高速缓冲存储器Cache(Memory),完全用硬件实现主存速度的提高

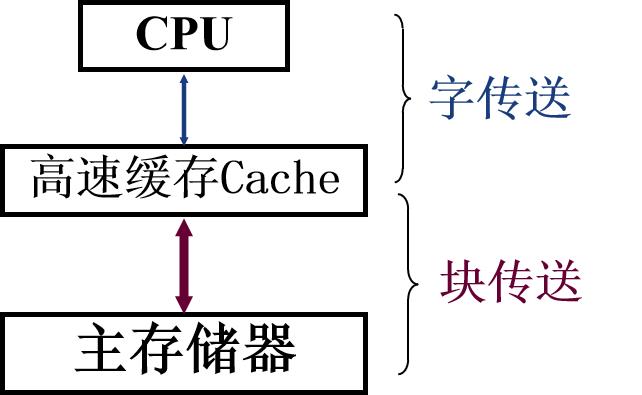

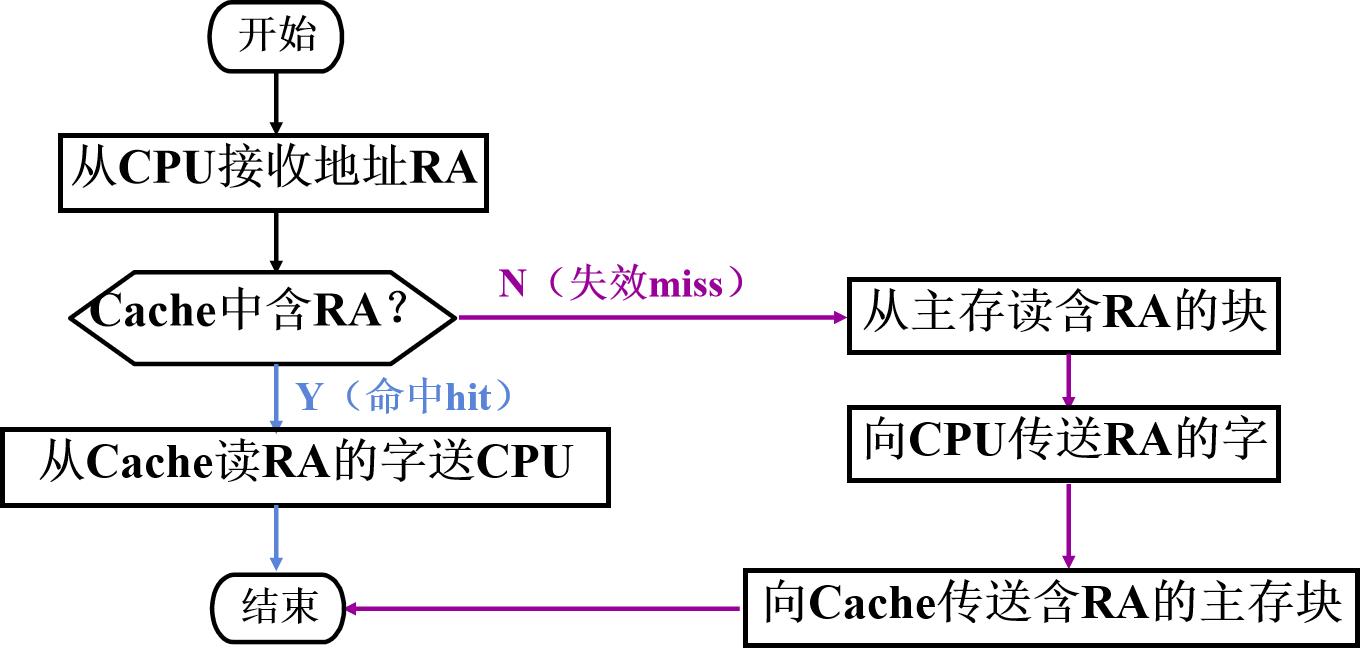

工作原理

· 高速缓存:在相对容量较大而速度较慢的主存DRAM与高速处理器之间设置的少量但快速SRAM组成的存储器

· 高速命中(Hit):

处理器读取主存的内容已包含在Cache中,可以直接读取Cache,不用访问主存

· 高速缺失(Miss):

处理器读取主存的内容不在Cache中,需要访问主存读取一个数据块

高速缓存的读操作

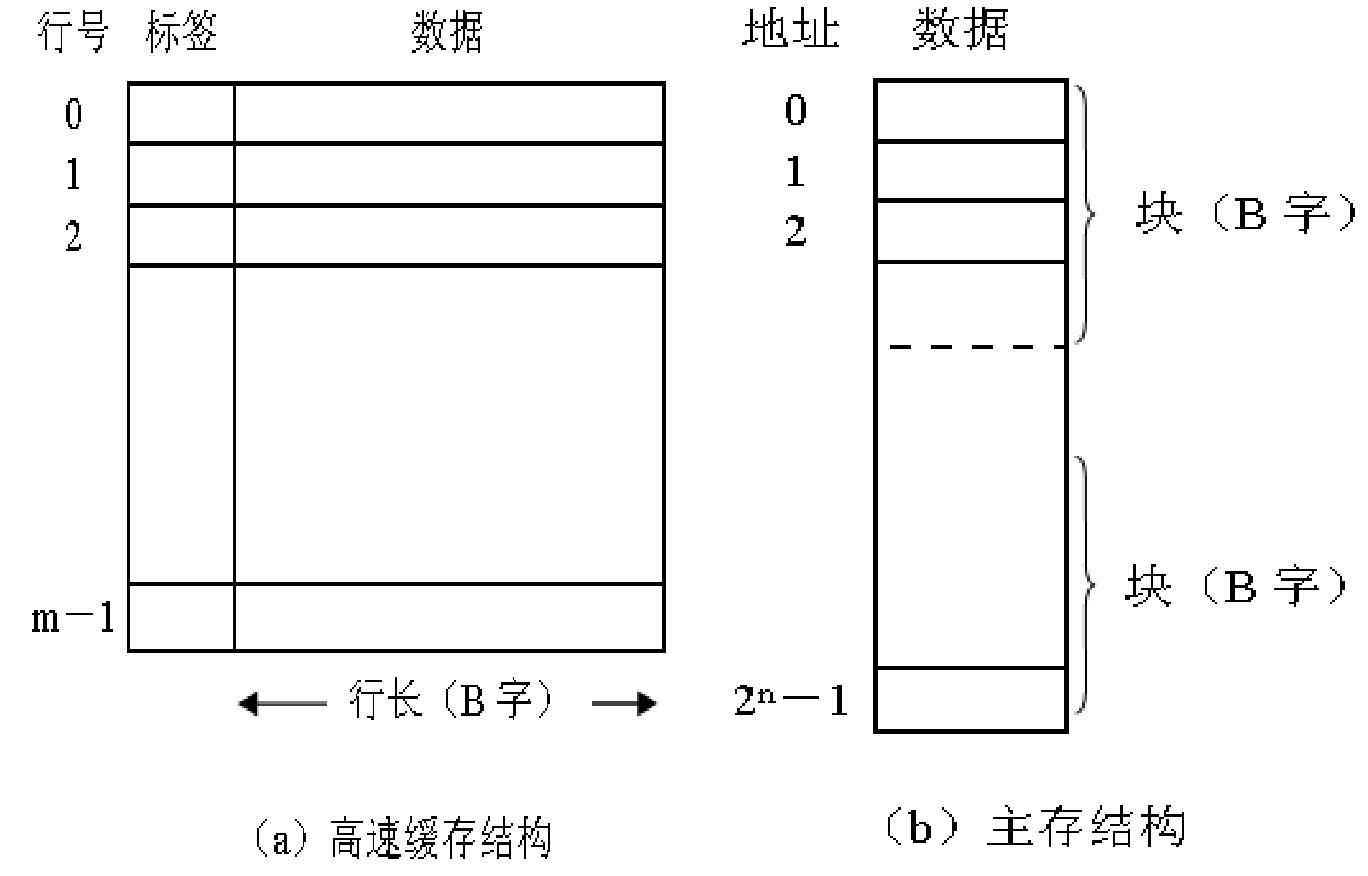

- 高速缓存的结构

· 主存以字(字节)为寻址单位

· Cache以行(线Line,槽Slot)为寻址单位

· Cache行包含B个主存字,对应一个主存块

· Cache与主存间的数据传送以数据块为单位

· 主存划分成M=2n÷B个“主存块”

· Cache具有m个“Cache行”

· Cache由数据存储器和标签存储器组成

数据存储器:高速缓存主存数据

标签存储器:保存数据所在主存的地址信息

- 高速缓存的容量和行大小

· 高速缓存性能的主要指标是命中率(Hit rate)

· 命中率(Hit Rate):高速命中的概率

· 对于高速缓存容量

希望它足够大,使存取时间接近高速缓存

希望它尽量小,使单位成本接近主存

受可用的芯片面积限制

同时还和运行的程序有关

· 对于Cache行大小

从很小增大,命中率开始会有提高

进一步增大,命中率可能反而减小 - 高速缓存的数量

· 单级与多级Cache

片上高速缓存(On-chip Cache)

第1级高速缓存(L1 Cache)

第2级高速缓存(L2 Cache)

第3级高速缓存(L3 Cache)

· 统一与分离Cache

统一(Unified)Cache

单个高速缓存既用于高速缓冲保存指令

也用于保存数据

分离(Split)Cache

一个专用于缓冲指令(I-Cache)

一个专用于缓冲数据(D-Cache)

以上是关于存储系统的主要内容,如果未能解决你的问题,请参考以下文章