CPU开发与存算一体技术

Posted 吴建明

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CPU开发与存算一体技术相关的知识,希望对你有一定的参考价值。

CPU开发与存算一体技术

CPU国产有多难

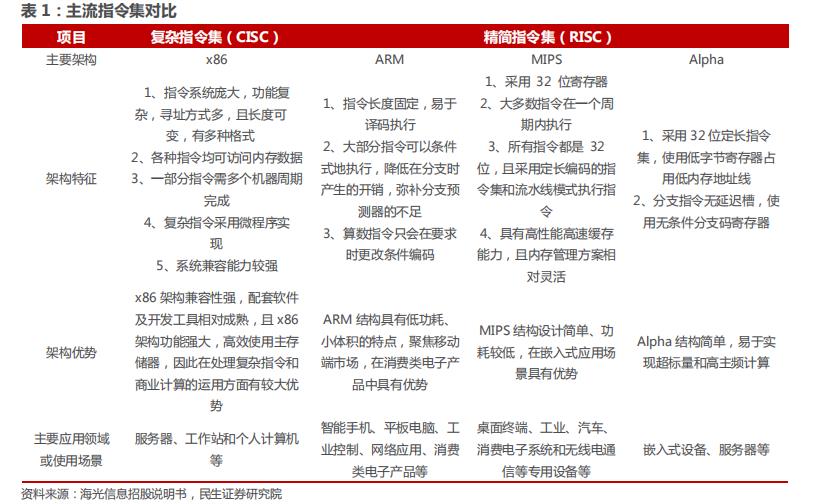

数字底座的“底座”——CPU,决定信创底层逻辑的关键。CPU 是信息产业中最基础的核心部件,指令集是计算机程序执行的基础单元功能集,是 CPU 产品生态体系的基石,可以分为复杂指令集(CISC)和精简指令集(RISC)两大类。

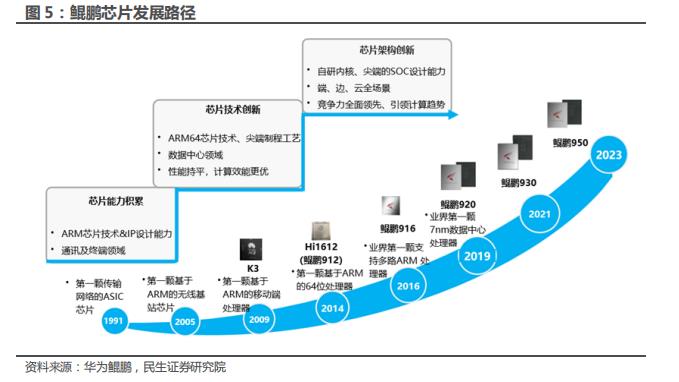

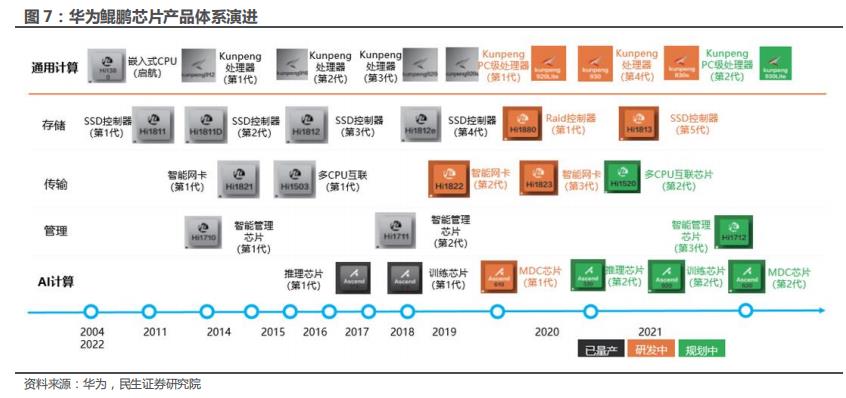

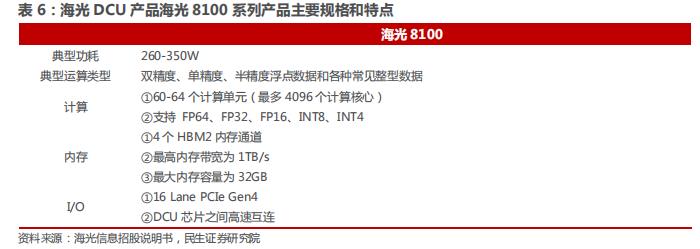

其中,复杂指集指令丰富、寻址方式灵活,以微程序控制器为核心,指令长度可变,功能强大,复杂程序执行效率高;精简指令集指令结构简单、易于设计,具有较高的执行能效比。在现行主流指令集架构中,x86 架构是复杂指令集的代表,而 ARM 架构、MIPS 架构和 Alpha 架构等是精简指令集的代表。CPU 是支撑数字底座生态架构发展的基础,也是决定信创底层发展逻辑的关键所在。国产 CPU 群雄逐鹿,各显“神通”。华为鲲鹏在国产 CPU 中目前具备最完善的生态体系与商业化环境,自上而下全栈式打造鲲鹏计算产业。海光 CPU 基于成熟的 x86 指令框架,“类 CUDA”计算环境和国际先进处理器设计技术,海光同时拥有海光 CPU 和海光 DCU 两类高端处理器产品,可以满足服务器、工作站等计算、存储设备中对高端处理器的功能需求,是目前适配难度最低、通用型较强的国产化 CPU 厂商;飞腾 CPU 与 麒麟操作系统构筑国产底座“PK”体系,是基础生态体系最全面的“国家队”。中科龙芯引进消化吸收 MIPS,推出了自主指令系统 LoongArch,是底层自主化程度最高的国产化 CPU 厂商。芯片为信创产业根本硬件基础,重要性凸显。不同于其他产业,IT 基础设施国产化存在显著的“木桶效应”,在“硬件—软件—服务”链条中任何环节的国产化能力缺失将造成整个自主体系发展的停滞。芯片作为整个 IT 生态最底层的基础硬件,为整个计算机体系提供算力支撑,通过与上层的操作系统紧密配合,实现系统软硬件的基础调度、控制与资源支持,是整个国产化信创体系的中枢大脑,是我国软硬件国产化的根本。1、华为自主研发的全国产化高性能 CPU基于 ARM 架构开发,是华为继移动麒麟芯片、AI 昇腾芯片后,第三款自研芯片。鲲鹏芯片定位于服务器应用,其产品自研完成了华为具备优势的服务器业务自上而下的基础算力打通。在通用计算处理器领域,2014 年发布鲲鹏 912 处理器, 2016 年发布鲲鹏 916处理器。2019 年 1 月,华为正式发布鲲鹏 920 芯片。根据华为官方介绍,鲲鹏 920 处理器是业界第一颗采用 7nm 工艺的数据中心级的 ARM 架构处理器,集成最多 64*自研核,支持 64 核、48 核、32 核等多种型号。华为将鲲鹏芯片用于自身服务器,并用来搭建自身的数据中心业务。鲲鹏芯片多向出击,鲲鹏 930 芯片值得期待。华为鲲鹏处理器是华为自主研发的基于 ARM架构的企业级系列处理器产品,包含“算、存、传、管、智”五个产品系统体系。为了保证鲲鹏计算产业的可持续演进,鲲鹏处理器从指令集和微架构两方面进行兼容性设计,确保既可以适应未来的应用和技术发展演进的需求,又能后向兼容。参考华为鲲鹏芯片的发展路径规划,鲲鹏次时代芯片 930 芯片将有望进一步迭代,并在服务器和 PC 两个方向进一步出击。TaiShan 200 服务器是华为新一代数据中心服务器,基于华为鲲鹏 920 处理器,适合为大数据、分布式存储、原生应用、高性能计算和数据库等应用高效加速,旨在满足数据中心多样性计算、绿色计算的需求。TaiShan 200 服务器仅为华为基于鲲鹏芯片所打造的自有服务器产品,鲲鹏通用计算平台事实上提供基于鲲鹏处理器的TaiShan 服务器、鲲鹏主板及开发套件。2、基于海外龙头加快自主研发,发出国产 x86 体系最强音拥有海光CPU和海光DCU两类高端处理器产品,可以满足服务器、工作站等计算、存储设备中对高端处理器的功能需求:海光 CPU:兼容 x86 指令集,处理器性能参数与国际同类型主流处理器产品相当,支持国内外主流操作系统、数据库、虚拟化平台或云计算平台,能够有效兼容目前存在的数百万款基于 x86 指令集的系统软件和应用软件,具有优异的生态系统优势。

此外,海光 CPU 支持国密算法,扩充了安全算法指令,集成了安全算法专用加速电路,支持可信计算,提升了高端处理器的安全性。从海光 CPU 应用场景角度看,公司将海光 CPU 产品规划为海光 7000 系列、海光 5000 系列和海光 3000 系列。三个系列产品技术设计同源,处理器核心等具有相似的技术特征。根据不同的产品规格定义,需要在一块基板上封装 1 至 4颗裸片。目前,公司在售的海光 CPU 产品主要为海光 7200、海光 5200 和海光 3200 系列产品。海光 DCU:以 GPGPU 架构为基础,兼容“类 CUDA”环境,软硬件生态丰富,典型应用场景下性能指标达到国际上同类型高端产品的水平。海光 DCU 主要面向大数据处理、商业计算等计算密集型应用领域,以及人工智能、泛人工智能类运算加速领域。海光 DCU 产品采用与海光 CPU 类似的产品研发策略,2018 年1 月启动深算一号 DC 产品设计,目前品已实现商业化应用。另一方面,公司启动了第二代 DCU 深算二号的产品研发工作已于 2020 年 1 月启动。海光 CPU 系列产品中海光一号、海光二号已经实现商业化应用,海光三号完成实验室验证,海光四号处于研发阶段;海光 DCU 系列产品深算一号已经实现商业化应用,深算二号处于研发阶段。3、长期自主化耕耘,拥抱 ARM 架构目前主要包括高性能服务器 CPU(飞腾腾云 S 系列)、高效能桌面 CPU(飞腾腾锐 D 系列)、高端嵌入式 CPU(飞腾腾珑 E 系列)和飞腾套片四大系列,为从端到云的各型设备提供核心算力支撑。基于飞腾 CPU 的产品覆盖多种类型的终端(台式机、一体机、便携机、瘦客户机等)、服务器和工业控制嵌入式产品等,在国内政务办公、云计算、大数据以及金融、能源和轨道交通等行业信息系统领域已实现批量应用。前两代飞腾芯片均停留在学术层面,均采用仿制英特尔架构及指令集的方法对芯片基础技术进行学习消化。自第三代产品 FT-1000 以来,飞腾芯片转而采用 SPARC 指令架构下的OpenSPARC 指令集。FT-1000 在制程上采用台积电的 65nm 技术,并可兼容SPARCv9 指令集。

随着 Sun 公司被 Oracle 收购,SPARC 架构的支持逐步减弱。飞腾芯片逐步投入 ARM 指令集的怀抱,并推出在原有 FT-1500 芯片上改进得来的探索性产品 FT-1500A。2015 年 8 月的 HotChips 2015 大会上,飞腾技术团队张承义进行题为《Mars: A 64-core ARMv8 Processor》的报告,标志着飞腾已设计出世界上第一款基于 ARM 架构的 64 核 CPU。芯片产品主要分为高性能服务器芯片、高效能桌面芯片和高端嵌入式芯片。高端嵌入式芯片:飞腾嵌入式芯片采用自主研发、面向嵌入式行业定制化的处理器核心,具有高安全、高可靠、强实时和低功耗的特点,满足行业终端产品、工业控制领域应用产品需求。高效能桌面芯片:飞腾桌面芯片采用自主研发的高能效处理器核心,全芯片性能卓越、功耗适度,最新产品内置硬件级安全机制,能够同时满足信息化领域对性能、能耗比和高安全的应用需求。高端嵌入式芯片:飞腾嵌入式芯片采用自主研发、面向嵌入式行业定制化的处理器核心,具有高安全、高可靠、强实时和低功耗的特点,满足行业终端产品、工业控制领域应用产品需求。从产品迭代上,天津飞腾主要包括 FT-1500 系列产品、FT-2000 系列产品以及基于 FTC663 内核的 D/S 系列产品。4、中科院嫡系部队,专注于自主架构 CPU引进消化吸收 MIPS,推出自主研发指令集架构。龙芯中科在指令系统上实现了自主创新。龙芯中科自研发初期即选择基于开放度较高的指令系统并结合自研的模式,在授权体系相对开放的 MIPS 指令系统基础上扩展了数百条自定义指令,形成了 MIPS 兼容指令系统 LoongISA,并在多款 CPU 芯片中得到应用。2020年,龙芯中科推出了自主指令系统 LoongArch。2021 年 7 月开始,公司信息化业务已经转向基于龙芯自主指令系统 LoongArch 的 3A5000 系列处理器,工控业务开始转向基于龙芯自主指令系统 LoongArch 的系列处理器。具体而言,龙芯中科研制的芯片包括龙芯 1 号、龙芯 2 号、龙芯 3 号三大系列处理器芯片及桥片等配套芯片:龙芯 1 号系列:低功耗、低成本专用嵌入式 SoC 或 MCU 处理器,通常集成1 个 32 位低功耗处理器核,应用场景面向嵌入式专用应用领域,如物联终端、仪器设备、数据采集等;龙芯 2 号系列:低功耗通用处理器,采用单芯片 SoC 设计,通常集成 1-4 个64 位低功耗处理器核,应用场景面向工业控制与终端等领域,如网络设备、行业终端、智能制造等。龙芯 3 号系列:高性能通用处理器,通常集成 4 个及以上 64 位高性能处理器核,与桥片配套使用,应用场景面向桌面和服务器等信息化领域;配套芯片:包括桥片及正在研发尚未实现销售的电源芯片、时钟芯片等,其中桥片主要与龙芯 3 号系列处理器配套使用和销售,电源芯片和时钟芯片主要与龙芯 2 号、龙芯 3 号系列处理器配套使用。龙芯 1 号、2 号、3 号处理器芯片及配套芯片的主要客户是板卡、整机厂商。

5、横向对比:国产化 CPU分析总结

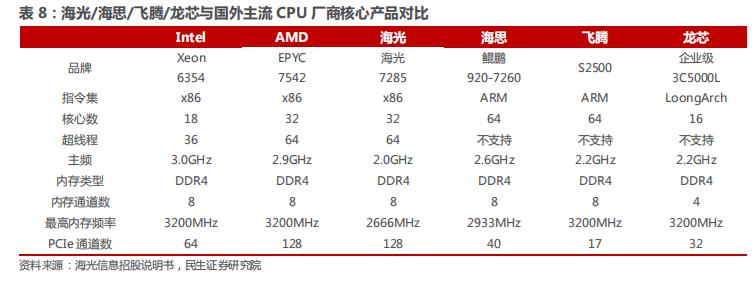

多指令集体系协同发展,基本产品参数已与国际主流产品具备一定可比性。指令集是影响处理器应用领域的重要因素,不同指令集架构下部分产品参数如核心数、超线程对产品性能影响程度不同,仅具有参考意义。

目前,海光信息采用 x86指令集架构,龙芯中科采用 LoongArch 指令集架构,天津飞腾及华为鲲鹏采用ARM 指令集架构。结合对几款国产化芯片厂商及其产品的分析和对比,我们认为可以得出以下结论:(1)国产化浪潮趋势明显,国产化芯片厂商有望顺势崛起。在海外贸易不确定性持续的背景下,芯片作为硬件基础底座的重要性与必要性凸显。海光与龙芯自2019 年以来收入的快速攀升,表明其在信创市场强劲的内生需求。在海外主流芯片厂商出口存在不确定的大背景下,国产化芯片厂商有望借助政策东风快速成长,顺势崛起。(2)海光信息服务器市场优势明显,中科龙芯 PC 市场存在潜力。根据产品单价及出货量来看,海光与龙芯分别在不同市场具备优势。海光承袭 x86 体系,在服务器市场具备优势;龙芯实现自主架构研发并重视生态建设,在 PC 及类 PC市场具备竞争优势。(3)ARM 架构生态强大,华为鲲鹏具备“王者归来”潜质。天津飞腾及华为鲲鹏基于 ARM 架构设计,本身能够较好地吸收 ARM 体系已有的生态应用。鲲鹏 920 芯片各项参数领先,并具备华为云自身作为稳定需求方,在自身软硬件技术优势下叠加持续壮大的合作伙伴生态体系,我们认为其是国产化芯片厂商中最具竞争优势的厂商之一。近期,鲲鹏在中国电信及农行等的中标,表明其发展潜力。如果供应链能够逐步复苏,有望实现“王者归来”。

存算一体:芯片设计瓶颈与挑战

面向云计算与边缘计算的大算力存算一体芯片、可重构存算一体技术和存算一体编译器的开发。

报告提纲分为大算力与大模型计算的瓶颈与挑战、存算一体的技术优势与设计难点、面向云计算与边缘计算的大算力存算一体芯片、可重构存算一体技术和存算一体编译器的开发。

1、大算力与大模型计算的瓶颈与挑战

AI发展趋势:大模型、通用AI、大算力需求爆发

AI模型历经数十年的发展,模型大小呈现出增速增加的趋势。由线性增长转变为指数增长。典型代表包括GPT-3、AlphaFold2等,个头都很大。

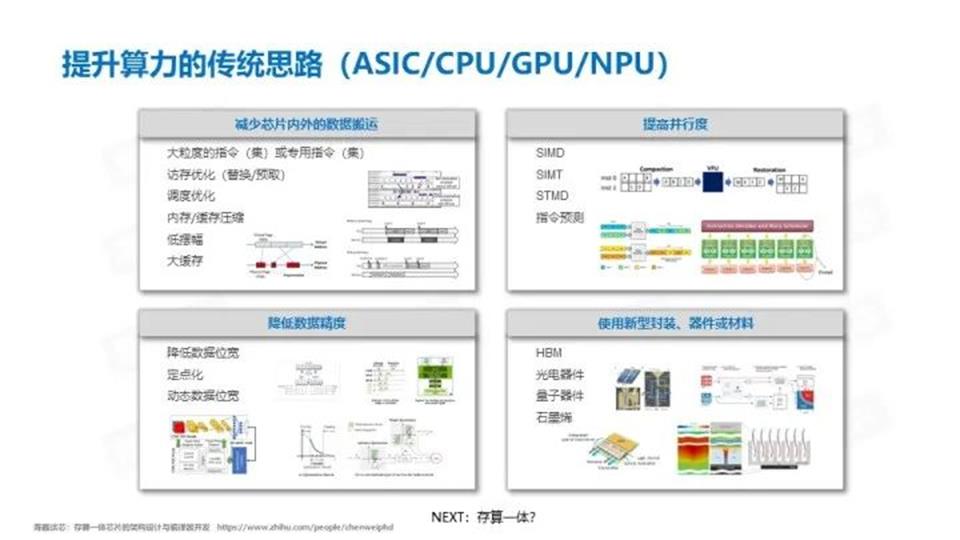

下面列了提升算力的一些传统思路。基本上各类方法在5年前都有使用过,但未能从根本上解决数据密集型算力的问题。例如包括为了减少数据搬运的大粒度的指令(集)或专用指令(集)、访存优化(替换/预取)、调度优化、内存/缓存压缩、低摆幅电路、大缓存技术等。也包括提高并行度的SIMD、SIMT、STMD、指令预测等技术。

大算力的瓶颈

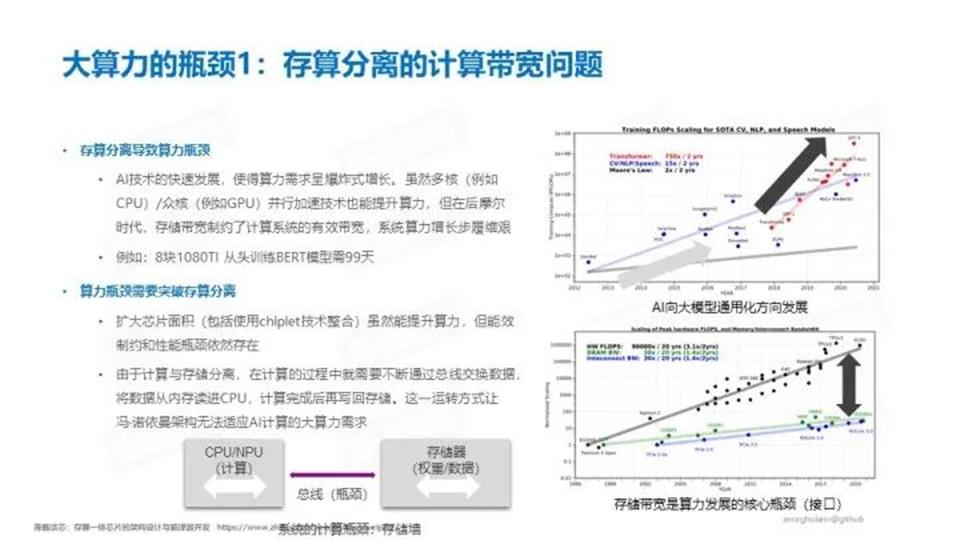

大算力的瓶颈,首先是存算分离的计算带宽问题。

存算分离会导致算力瓶颈。AI技术的快速发展,使得算力需求呈爆炸式增长。虽然多核(例如CPU)/众核(例如GPU)并行加速技术也能提升算力,但在后摩尔时代,存储带宽制约了计算系统的有效带宽,系统算力增长步履维艰。例如,8块1080TI 从头训练BERT模型需99天。想解决算力瓶颈,就需要突破存算分离得限制。传统的一些方法,包括扩大芯片面积(包括使用chiplet技术整合)虽然能提升算力,但能效制约和性能瓶颈依然存在。由于计算与存储分离,在计算的过程中就需要不断通过总线交换数据,将数据从内存读进CPU,计算完成后再写回存储。这一运转方式让冯·诺依曼架构无法适应AI计算的大算力需求。

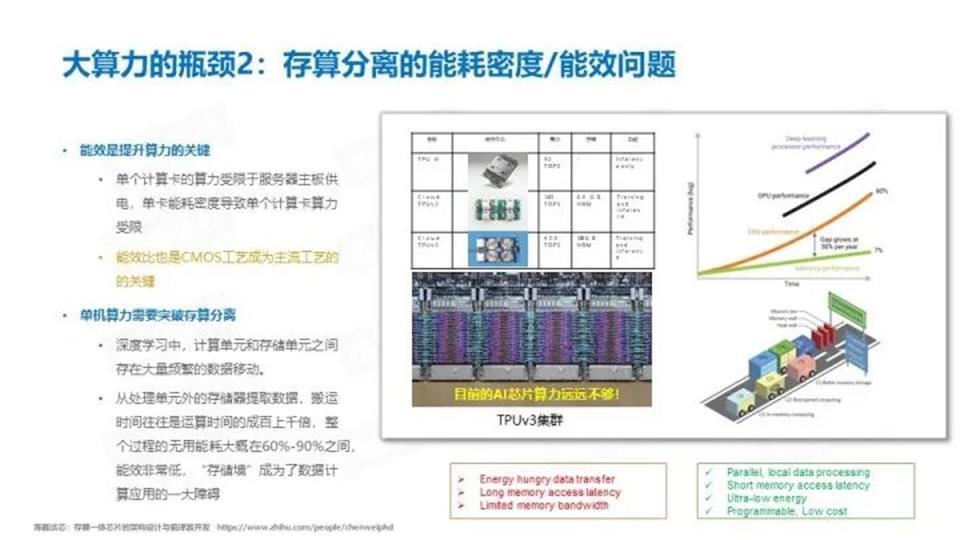

第二个瓶颈,是存算分离的能耗密度/能效问题。能效其实是提升算力的关键。服务器环境下,单个计算卡的算力受限于服务器主板供电,单卡能耗密度导致单个计算卡算力受限。了解半导体发展历史的应该清楚,能效比也是CMOS工艺成为主流工艺的的关键。另外一点,单机算力需要突破存算分离。深度学习中,计算单元和存储单元之间存在大量频繁的数据移动。从处理单元外的存储器提取数据,搬运时间往往是运算时间的成百上千倍,整个过程的无用能耗大概在60%-90%之间,能效非常低,这时“存储墙”成为了数据计算应用的一大障碍。

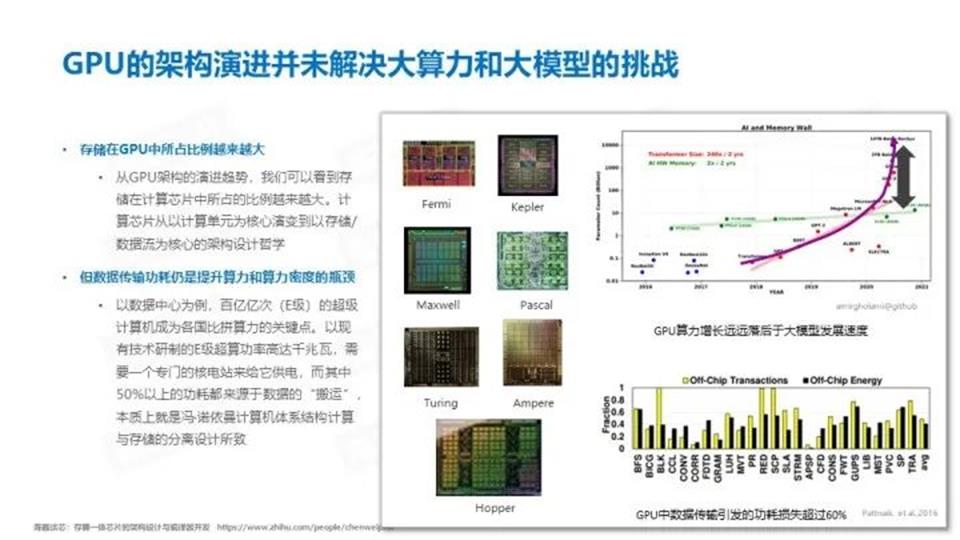

GPU的架构演进并未解决大算力和大模型的挑战

虽然说现在很多AI计算使用GPU,但GPU的发展速度已经不能适应AI模型的发展速度了。

一方面,存储在GPU中所占比例越来越大。从GPU架构的演进趋势,我们可以看到存储在计算芯片中所占的比例越来越大。计算芯片从以计算单元为核心演变到以存储/数据流为核心的架构设计哲学。另一方面,数据传输功耗仍是提升算力和算力密度的瓶颈。以数据中心为例,百亿亿次(E级)的超级计算机成为各国比拼算力的关键点。以现有技术研制的E级超算功率高达千兆瓦,需要一个专门的核电站来给它供电,而其中50%以上的功耗都来源于数据的“搬运”,本质上就是冯·诺依曼计算机体系结构计算与存储的分离设计所致。

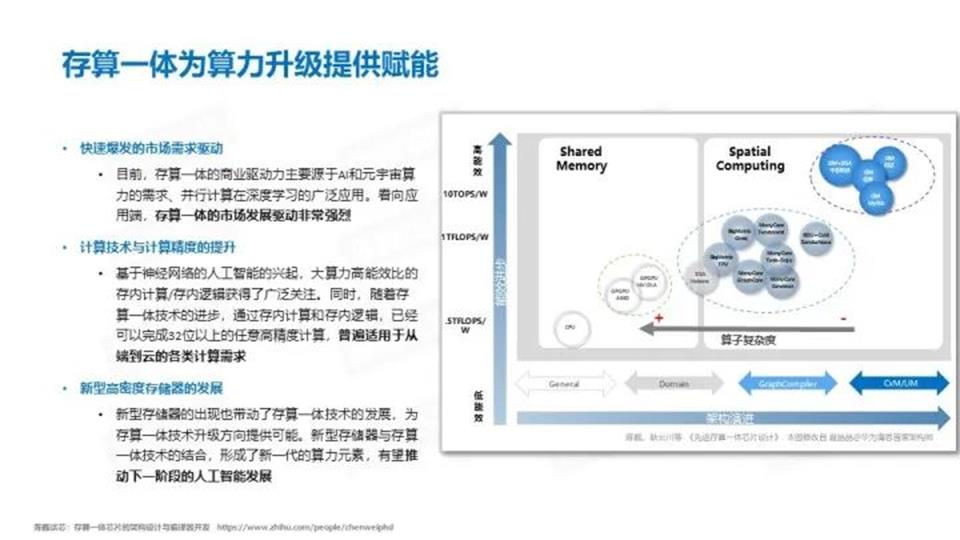

存算一体为算力升级提供赋能

我们看到,存算一体将为算力升级提供赋能。

一方面,是快速爆发的市场需求驱动。目前,存算一体的商业驱动力主要源于AI和元宇宙算力的需求、并行计算在深度学习的广泛应用。看向应用端,存算一体的市场发展驱动非常强烈另一方面,是存算一体计算技术与计算精度的提升。基于神经网络的人工智能的兴起,大算力高能效比的存内计算/存内逻辑获得了广泛关注。同时,随着存算一体技术的进步,通过存内计算和存内逻辑,已经可以完成32位以上的任意高精度计算,普遍适用于从端到云的各类计算需求。最后,新型高密度存储器的发展,也给存算一体的发展提供 了更多的可能。新型存储器的出现也带动了存算一体技术的发展,为存算一体技术升级方向提供可能。新型存储器与存算一体技术的结合,形成了新一代的算力元素,有望推动下一阶段的人工智能发展。

2、存算一体的技术优势与设计难点

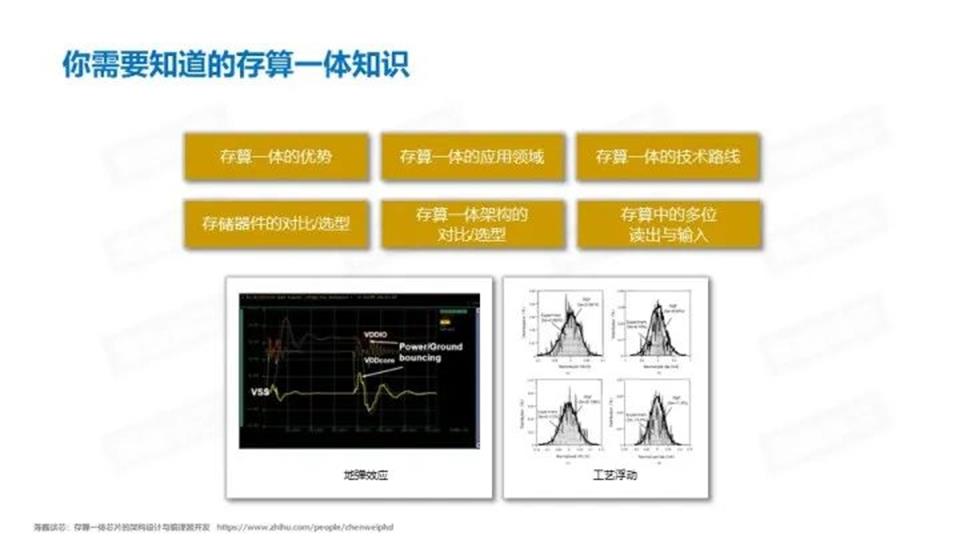

如果想把存算一体领域搞清楚,需要了解以下存算一体知识。比如存算一体的优势、应用领域、技术路线、存储器件的对比选型等等。这些知识也对很多存算一体领域的投资机构有价值。

如果是学习技术,则还要深入研究存算一体的架构和对比选型,以及电路级的多位读出与输入技术。

存算一体的原理、优势

存算一体就是存储器中叠加计算能力,以新的高效运算架构进行二维和三维矩阵计算。

存算一体的优势包括:1)具有更大算力(1000TOPS以上)2)具有更高能效(超过10-100TOPS/W),超越传统ASIC算力芯片3)降本增效(可超过一个数量级)存算一体技术的技术底层特征包括:减少数据搬运(降低能耗至1/10~1/100)存储单元具备计算能力(等效于在面积不变的情况下规模化增加计算核心数,或者等效于提升工艺代)单个存算单元替代“计算逻辑+寄存器” 更小更快

存算一体的应用领域与技术路线

存算一体可以用于互联网的个性化推荐、语音识别、自然语言处理,也可用于自动驾驶、工业视觉等很多领域。在技术层级上,存算一体可以给不同的计算芯片赋能,使各个领域的计算芯片提升能效和算力。

存算一体方面,其实有几个不同的技术路线。其中查存计算已经在GPU中广泛使用,近存计算正被AMD作为与Chiplet结合的关键技术落地。国内做存内计算的公司已经起步,并且在小算力芯片上逐渐突围。同时计算灵活性更好的存内逻辑技术也在兴起。

查存计算(Processing With Memory):GPU中对于复杂函数就采用了这种计算方法,是早已落地多年的技术。存储芯片内部的存储单元完成查表计算操作,存储单元和计算单元完全融合,没有一个独立的计算单元。近存计算(Computing Near Memory):典型代表是AMD的Zen系列CPU。计算操作由位于存储区域外部的独立计算芯片/模块完成。这种架构设计的代际设计成本较低,适合传统架构芯片转入。这次达摩院发布的存算芯片也属于这一类型。存内计算(Computing In Memory):典型代表是Mythic、千芯、闪亿、知存、九天睿芯。计算操作由位于存储芯片/区域内部的独立计算单元完成,存储和计算可以是模拟的也可以是数字的。这种路线适合算法固定的场景算法计算,目前主要用于语音等轻算力场景。存内逻辑(Logic In Memory):典型代表包括TSMC(在2021 ISSCC发表)和千芯科技。通过在内部存储中添加计算逻辑,直接在内部存储执行数据计算,这种架构数据传输路径最短,同时能满足大模型的计算精度要求。

参考文献链接

https://mp.weixin.qq.com/s/EHHj-iScK30LTLfJ0LpKng

https://mp.weixin.qq.com/s/tdMHAgBUYbD9SFC4eWsP7w

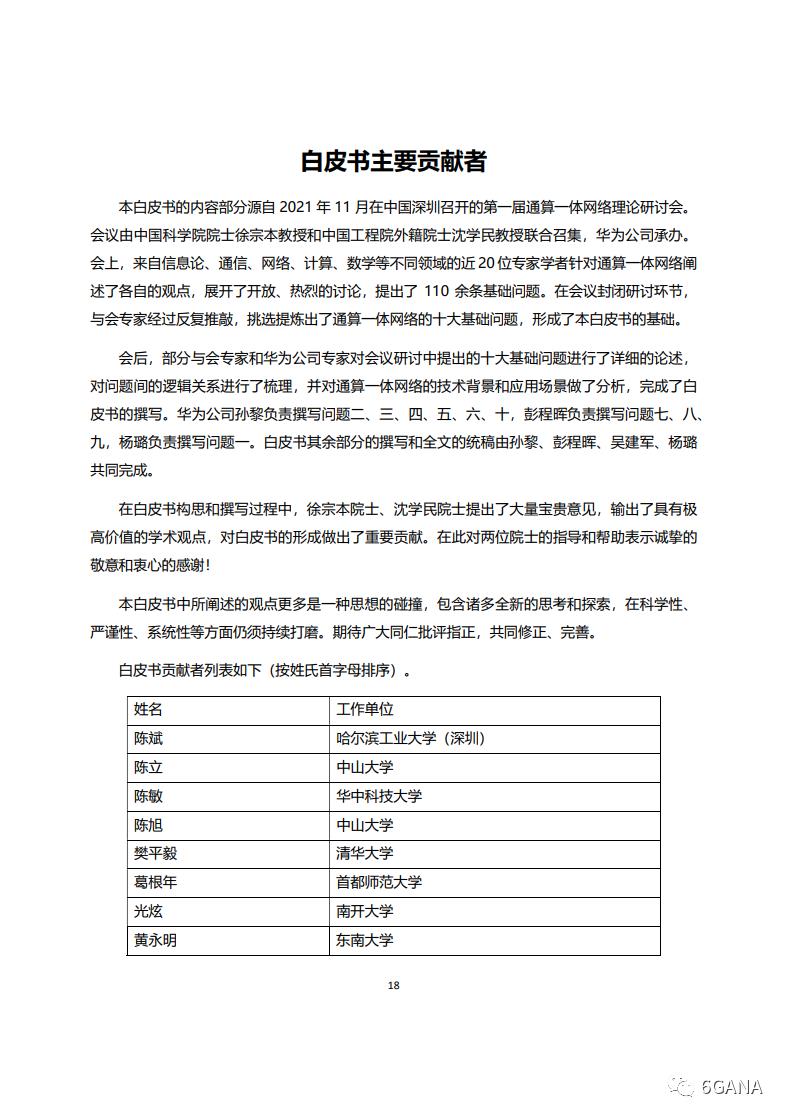

《通算一体网络十大基础问题白皮书》

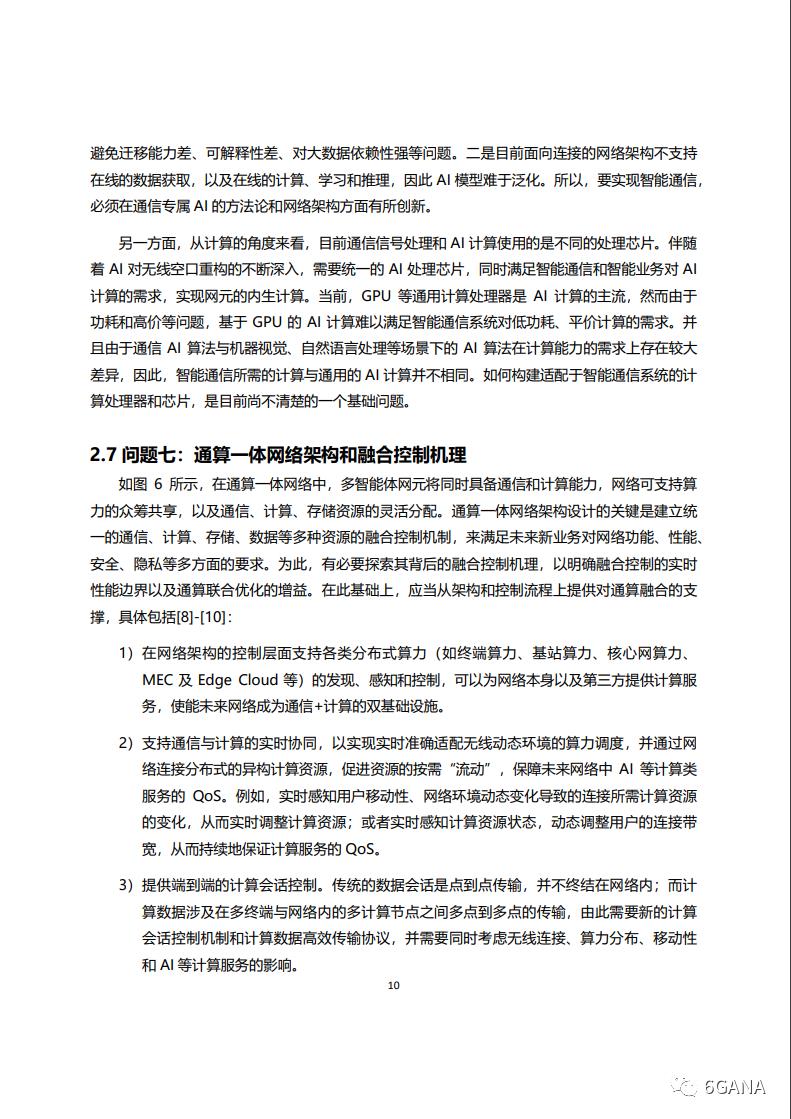

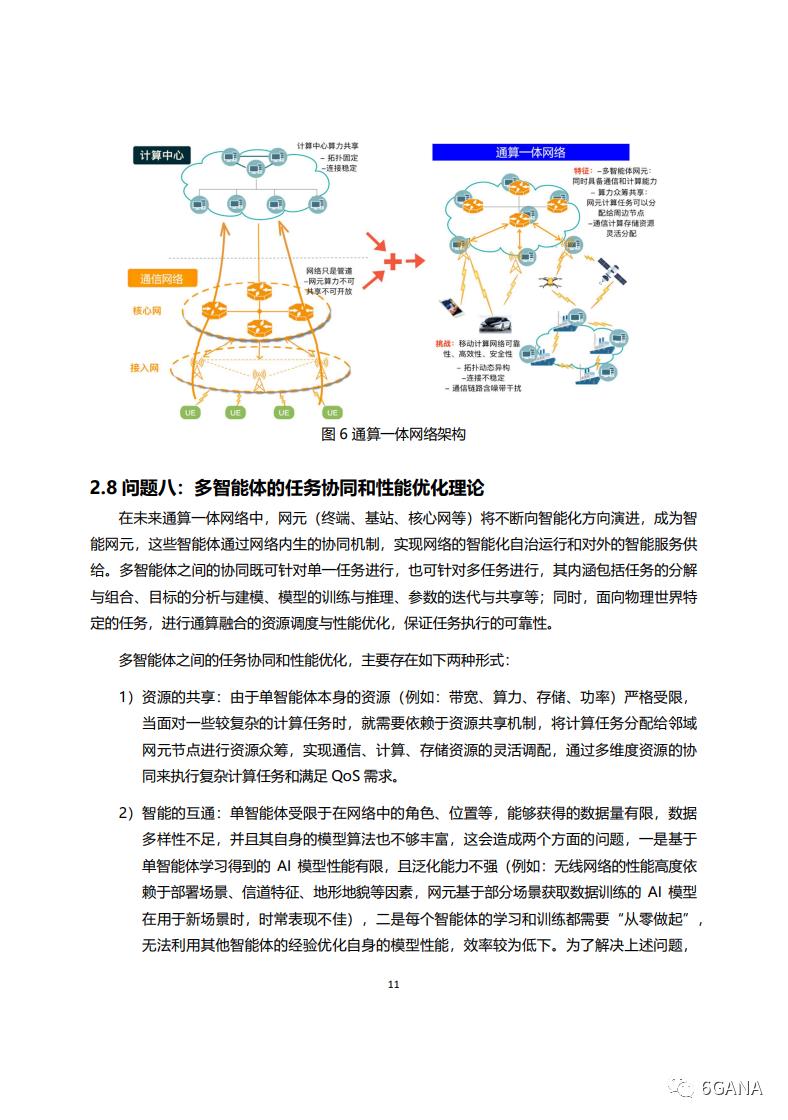

推荐理由

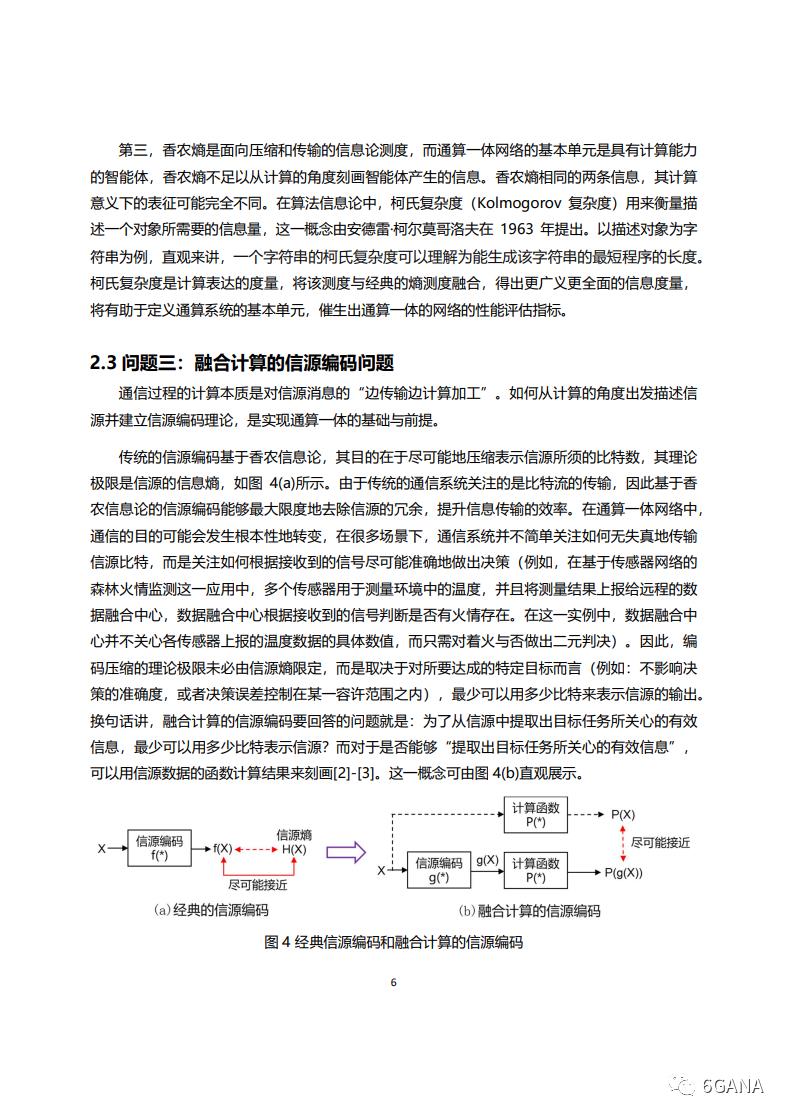

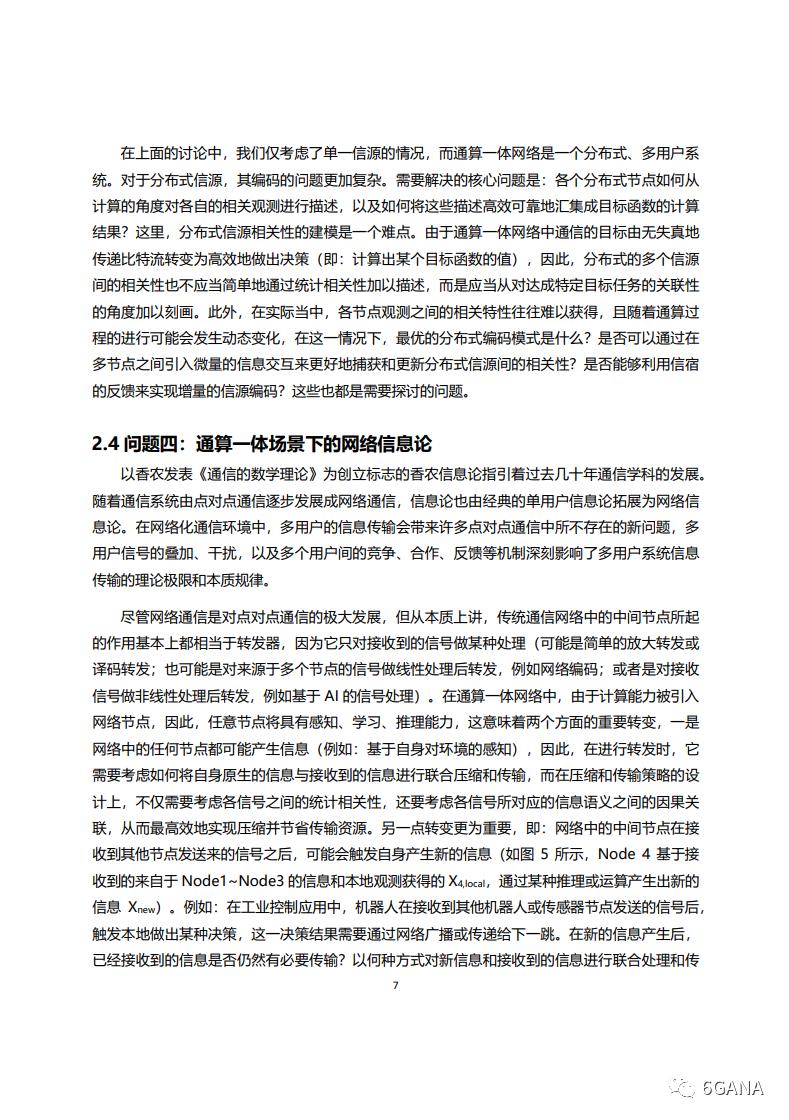

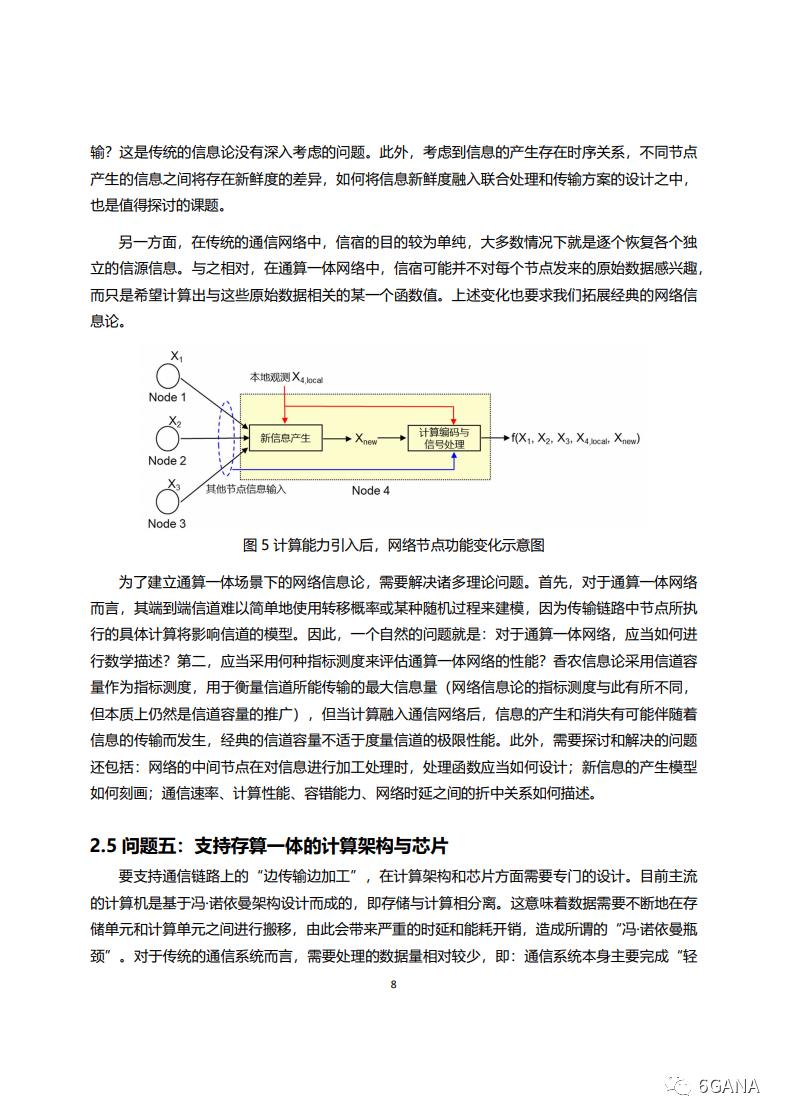

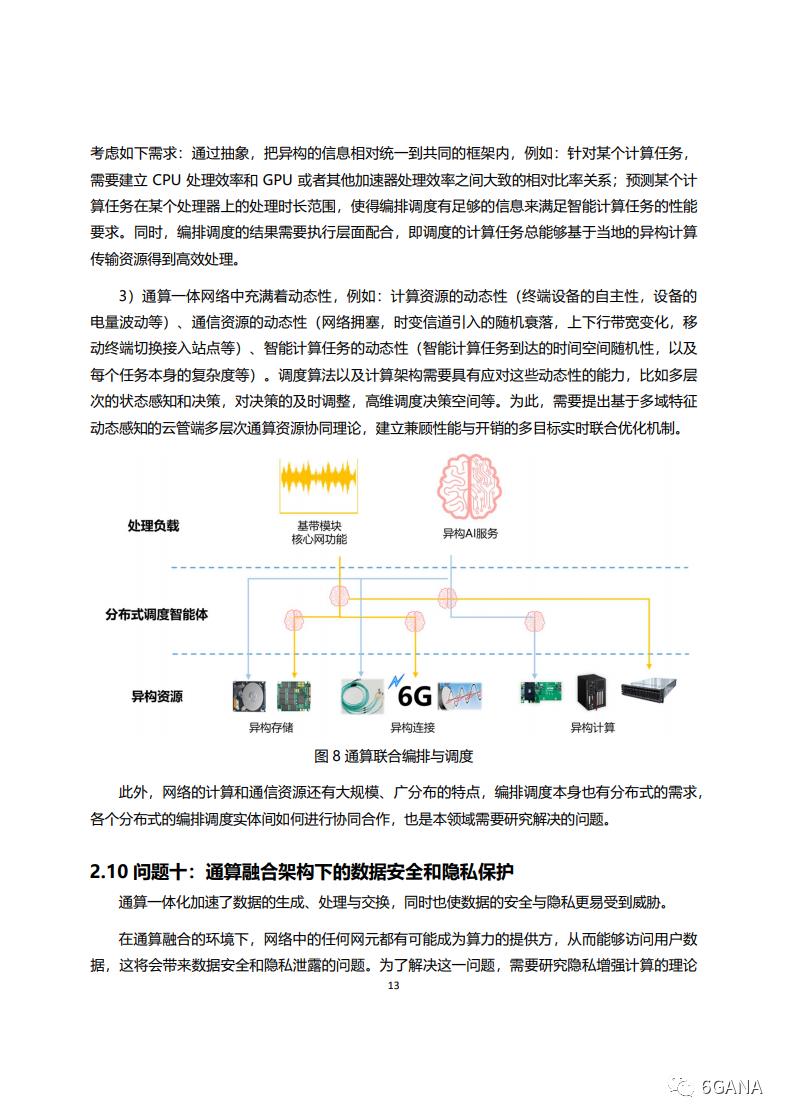

本白皮书首先阐述通算一体网络的内涵和三大典型应用场景,在此基础上提出通算一体网络的十大基础问题,包含:分布式信息处理的数学基础、通算一体环境下信息熵的重定义、融合计算的信源编码问题、通算一体场景下的网络信息论、支持存算一体的计算架构与芯片、智能通信的物理架构与网元内生计算、通算一体网络架构和融合控制机理、多智能体的任务协同和性能优化理论、通信与计算的资源置换机理和联合编排方法、通算融合架构下的数据安全和隐私保护。上述十大问题涉及理论基础、协议架构、算法机制三个层面。对于每个问题,均详细阐述了其具体内涵,以及在研究中所面临的挑战,以期引发学术界和产业界的思考,推动通算一体理论和技术的创新,形成业界共识。

正文内容

以上是关于CPU开发与存算一体技术的主要内容,如果未能解决你的问题,请参考以下文章

存算一体芯片离普及还有多远?听听从业者怎么说 | 对撞派 x 后摩智能